CMT2300A

Rev 1.0 | Page16/46

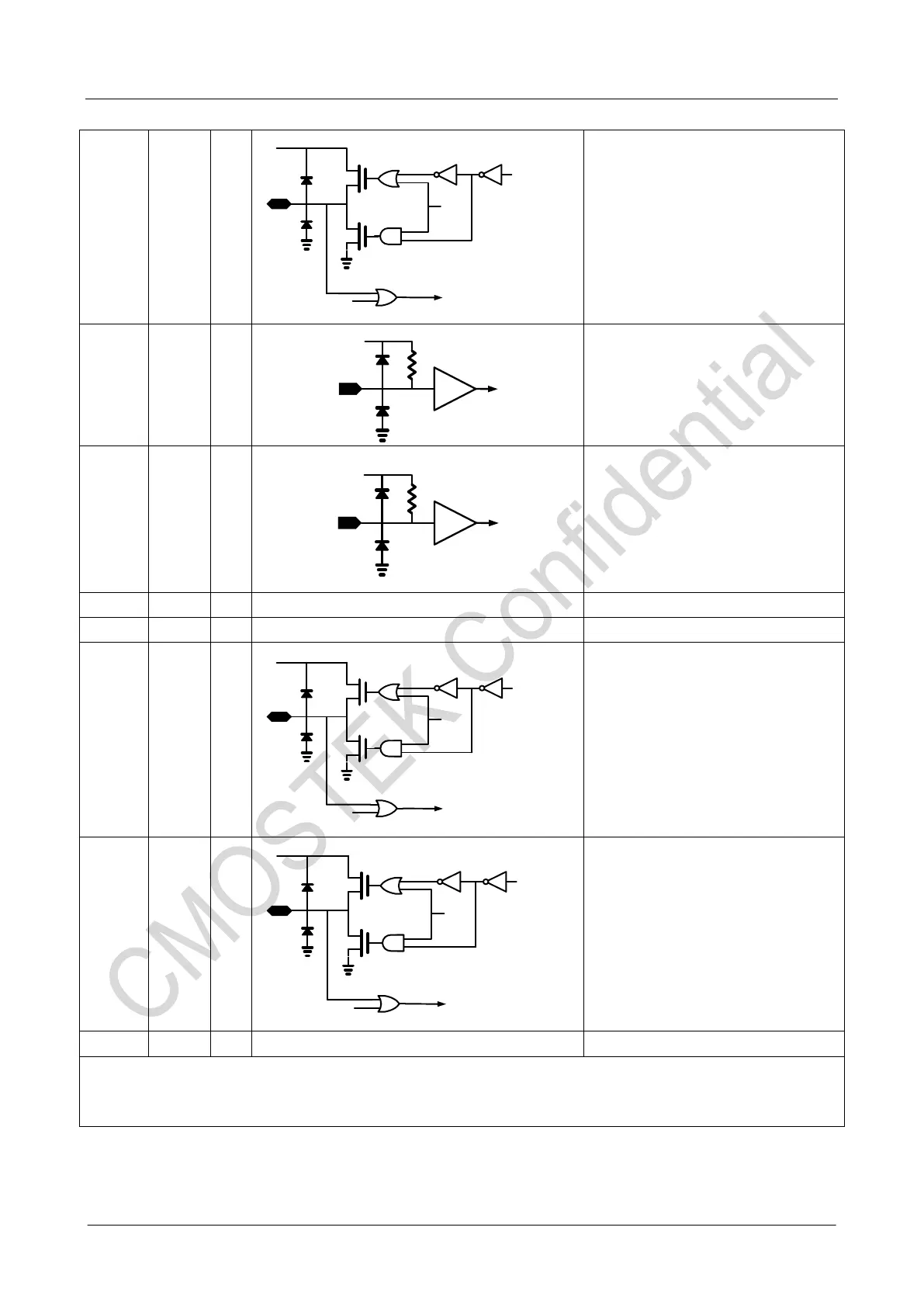

SDIO

din

pd_din

dout

pd_dout

Data tristate

pd_din default value is “0”

pd_dout default value is “1”

VDD

SPI data input and output

SPI chip selection bar for register access,

active low

SPI chip selection bar for FIFO access,

active low

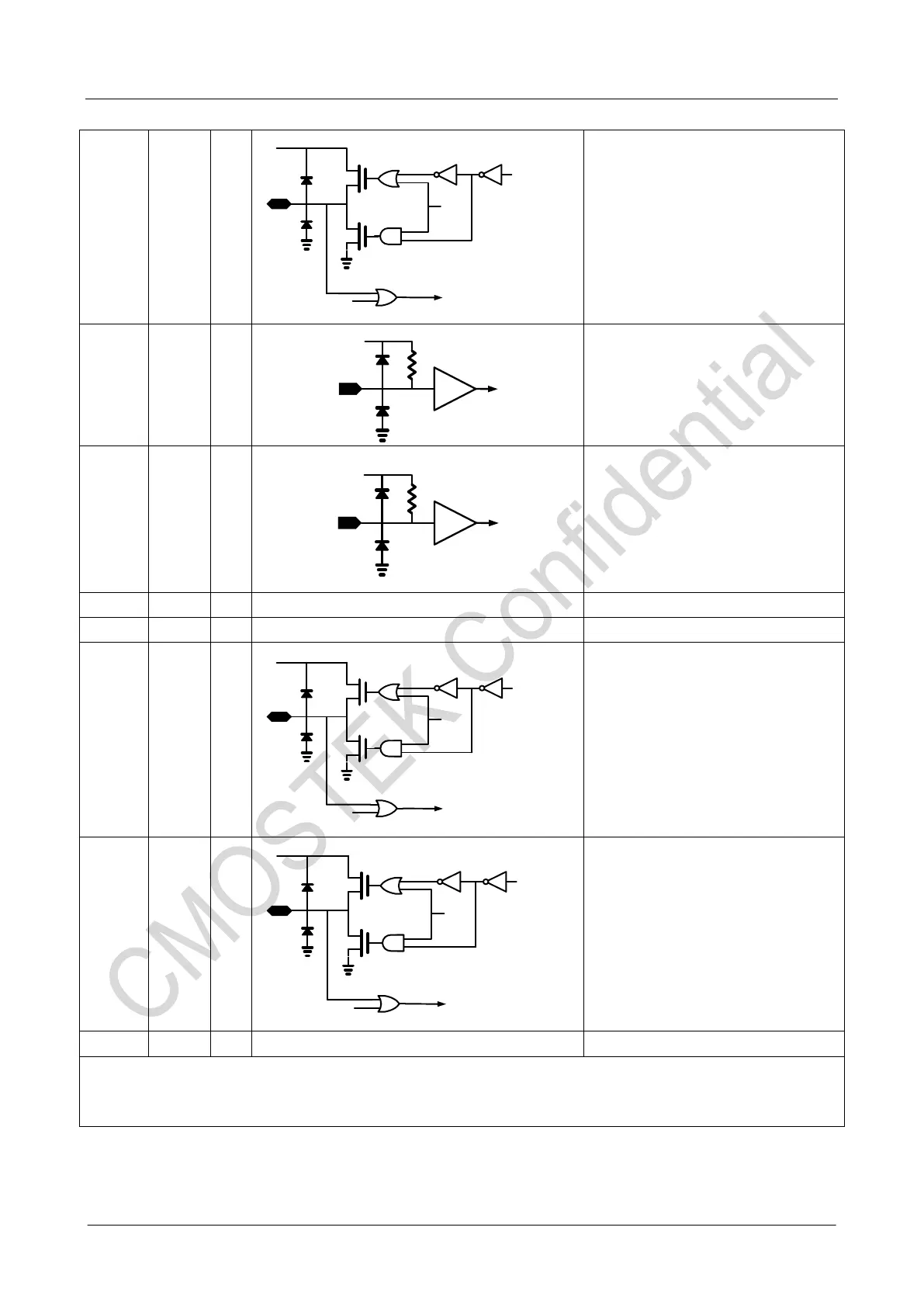

GPIO2

din

pd_din

dout

pd_dout

Data tristate

pd_din default value is “1”

pd_dout default value is “0”

VDD

Configured as INT1, INT2, DOUT/DIN,

DCLK (TX/RX) and RF_SWT

GPIO1

din

pd_din

dout

pd_dout

Data tristate

pd_din default value is “1”

pd_dout default value is “0”

VDD

Configured as DOUT/DIN, INT1, INT2,

DCLK (TX/RX) and RF_SWT

Analog GND. It must be grounded.

Note:

[1]. INT1 and INT2 are interrupts. DOUT is demodulated output. DIN is a modulation input. DCLK is a modulation or

demodulation data rate synchronization clock, automatic switching in TX/RX mode.

Loading...

Loading...