CMT2300A

Rev 1.0 | Page28/46

FIFO_MARGE_EN to 1 to merge the two separated FIFO into one 64-byte FIFO. It can be used both under TX and RX. By

configuring the FIFO_RX_TX_SEL to indicate whether it is currently used as TX FIFO or RX FIFO. When the two FIFO are not

merged, users can fill in the TX FIFO while the RX FIFO is used to receive data in the RX mode.

The FIFO can be accessedvia the SPI interface. The user can clear the FIFO by setting FIFO_CLR_TXor FIFO_CLR_RX to 1.

Also, the user can re-send the old datain the TX FIFO by setting FIFO_RESTORE to 1, without the need of re-filling the data.

5.2.1 FIFO Read Operation

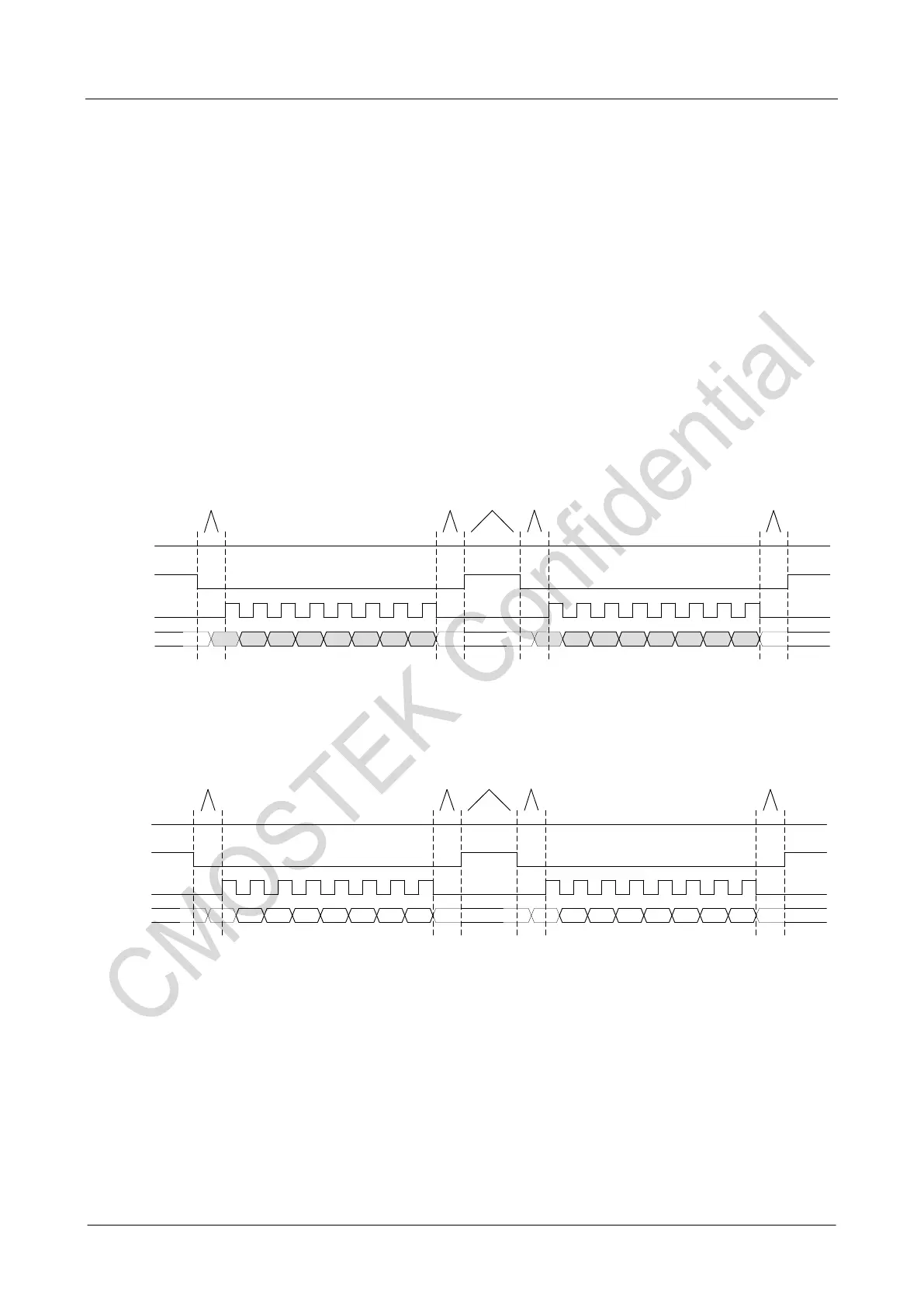

When the MCU accesses to the FIFO, the user must first configure a few registers to setup the FIFO read/write mode, as well as

some other working mode. The details are introduced in “AN143-CMT2219B FIFO and Data Packet Usage Guideline”. Here is

the read-write timing diagram. Note that there is a slight difference in the control of the FCSB for accessing to the FIFO and the

control of the CSB for accessing to the register. When the MCU starts to access to the FIFO, FCSB must be pulled down 1-clock

cycle at first, and then send the rising edge of SCL. After the last falling edge of SCL is sent, the MCU must wait at least 2 us to

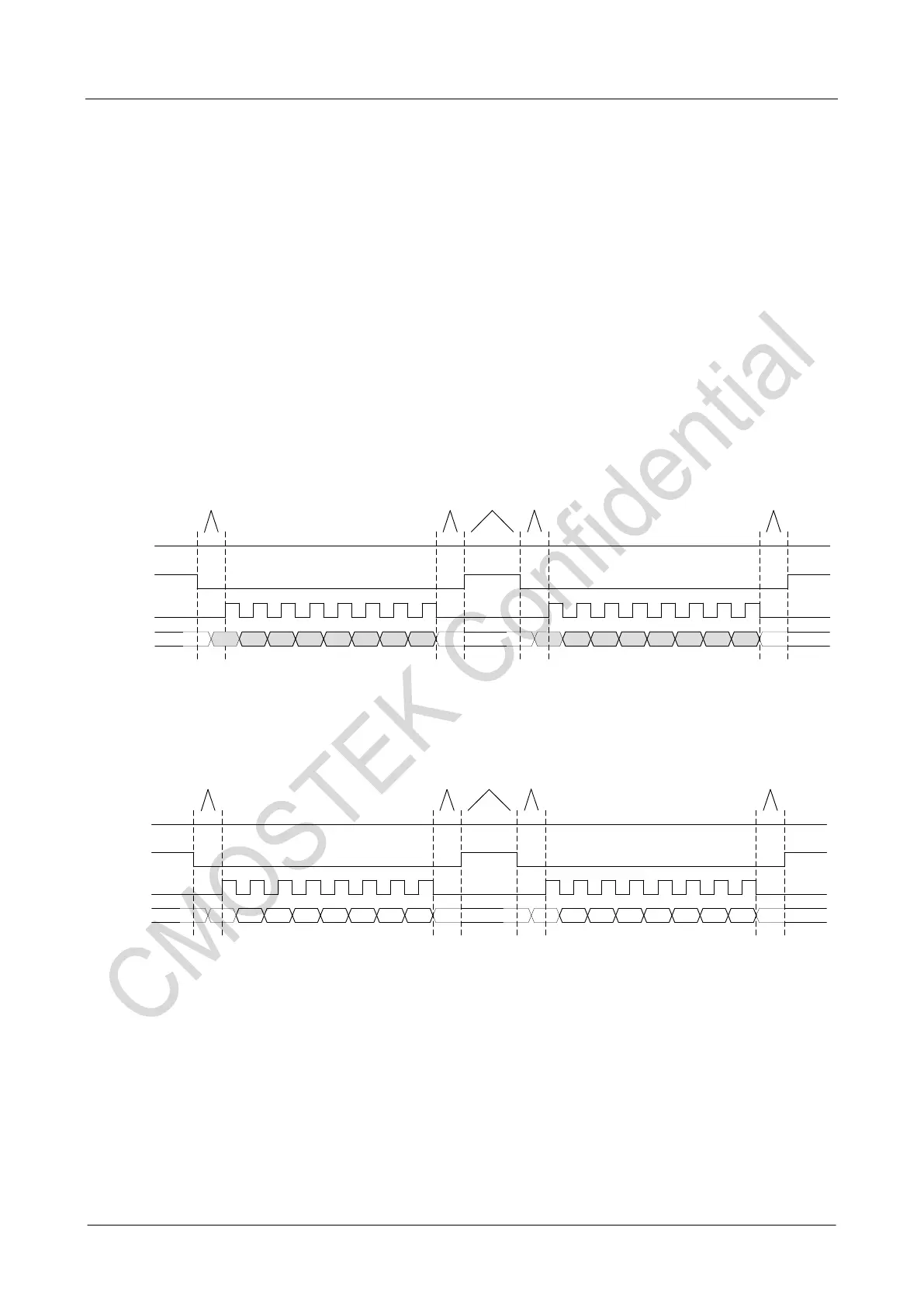

pull up the FCSB. Between the adjacent read/write operations, the FCSB must be pulled high for 4us at least. When writing the

FIFO, the first bit data must be ready 0.5 clock cycles before sending the first rising edge of SCL.

SCLK

FCSB

SDIO

X X

FIFO read data

01234567 01234567X

FIFO read data

CSB

> 1 SCLK cycle > 4 us> 2 us > 2 us> 1 SCLK cycle

Figure 11. SPI read FIFO timing

SCLK

FCSB

SDIO

X X

FIFO write data

01234567 01234567X

FIFO write data

CSB

> 1 SCLK cycle > 4 us> 2 us > 2 us> 1 SCLK cycle

Figure 12. SPI write FIFO timing

5.2.2 FIFO Associated Interrupt

CMT2300A provides rich interrupt sources associated with the FIFO. The interrupt timing for Tx and Rx FIFO is shown below:

Loading...

Loading...