CMT2300A

Rev 1.0 | Page29/46

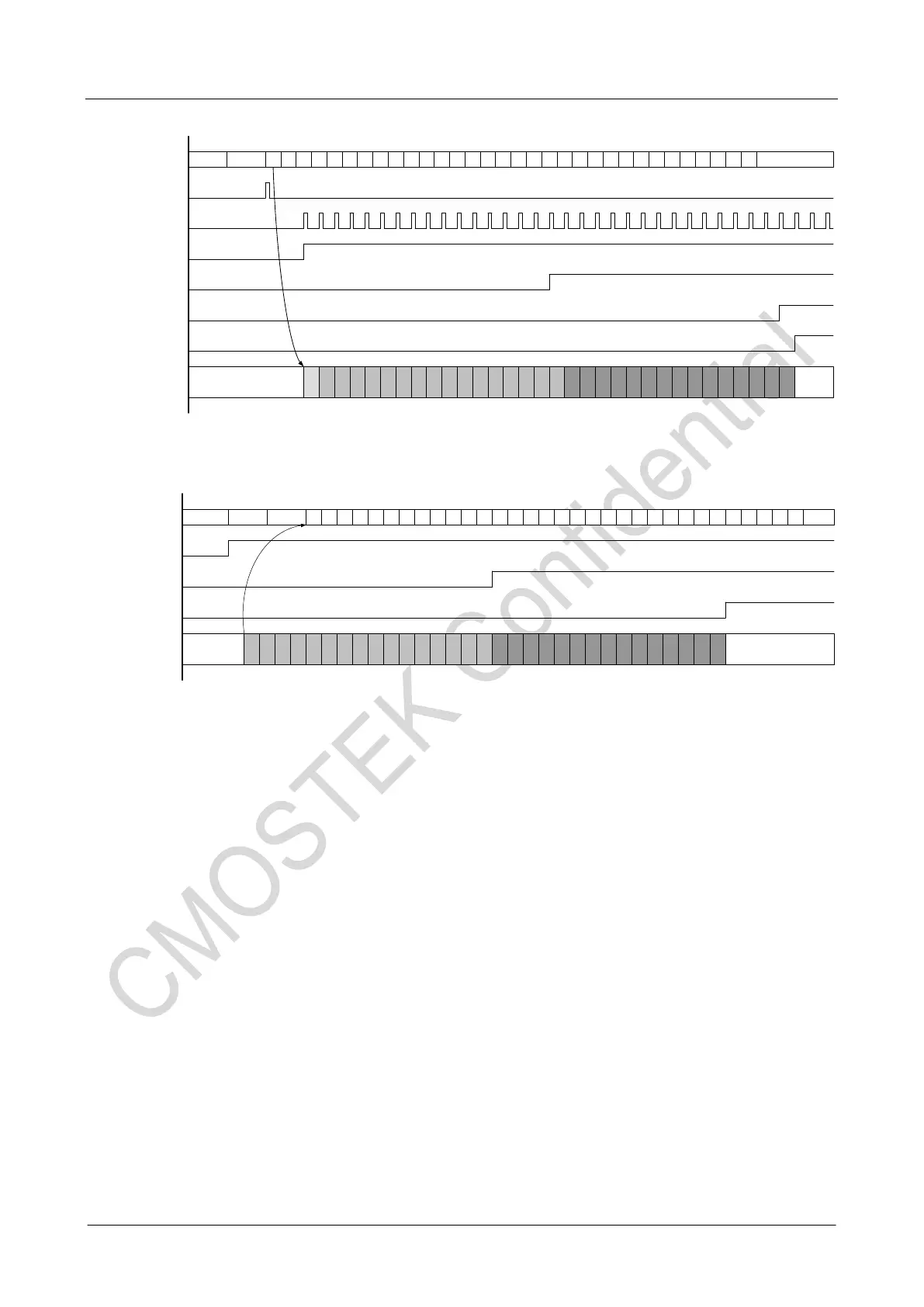

10 32 54 76 98 1110 1312 1514 1716 1918 2120 2322 2524 2726 2928 3130EMPTY FULL

RX_FIFO_NMTY

RX_FIFO_TH

RX_FIFO_FULL

Sync 10 32 54 76 98 1110 1312 1514 1716 1918 2120 2322 2524 2726 2928 3130RX DATA Noise Noise

SYNC_OK

RX FIFO ARRAY

RX_FIFO_OVF

(FIFO_TH = 16)

RX_FIFO_WBYTE

Figure 13. CMT2300ARX FIFO interrupt timing diagram

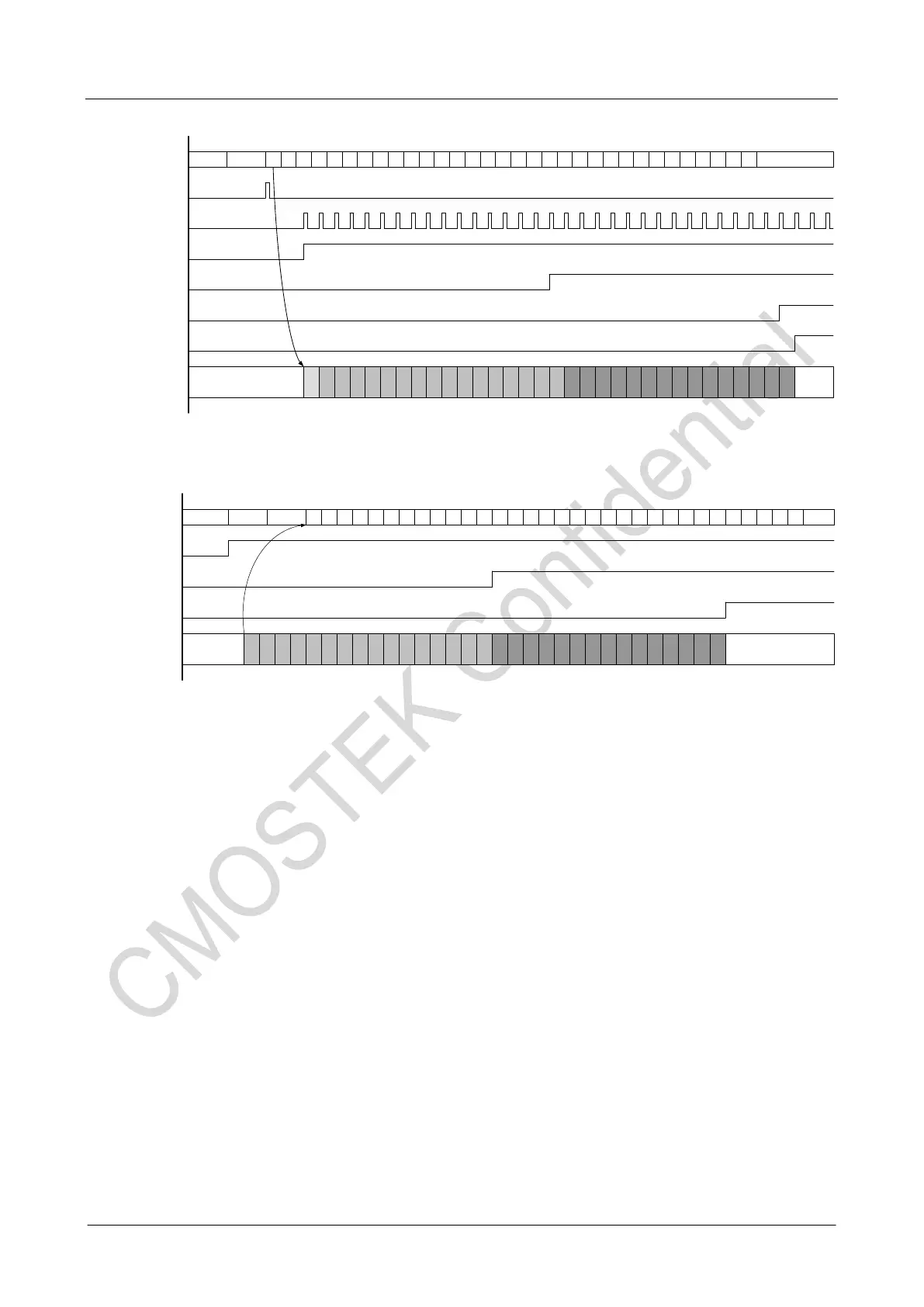

10 32 54 76 98 1110 1312 1514 1716 1918 2120 2322 2524 2726 2928 3130EMPTY FULL

TX_FIFO_NMTY

TX_FIFO_TH

TX_FIFO_FULL

Sync 10 32 54 76 98 1110 1312 1514 1716 1918 2120 2322 2524 2726 2928 3130TX DATA Prefix 0

FIFO ARRAY

(FIFO_TH = 16)

Pream

Figure 14. CMT2300A TX FIFO interrupt timing diagram

5.3 Operation State, Timing and Power Consumption

5.3.1 Startup Timing

After the chip VDD is powered up, the chip usually needs to wait about 1ms, then POR will release. After the release of the POR,

the crystal will start, the start time is 200 us - 1 ms, depending on the characteristics of the crystal itself. After starting, the user

need to wait for the crystal settled, then the system starts working. The default setting is 2.48ms. This time can be modified by

writing XTAL_STB_TIME <2:0> afterword (it has to be longer than the crystal inherent settling time). However, if the inherent

settling time of the crystal is difficult to observed by the user, the default setting of 2.48 ms is recommended and is able to cover

most of the crystals.

The chip remains in the IDLE status until the crystal is settled. After the crystal is settled, the chip will leave the IDLE state and

begin to do the calibration of each module. After the calibration is completed, the chip will stay in the SLEEP and wait until the

user to initialize the configuration. At any time, as long as the soft reset is performed, the chip will go back to the IDLE and be

powered up again.

Loading...

Loading...