3. Instruction Set

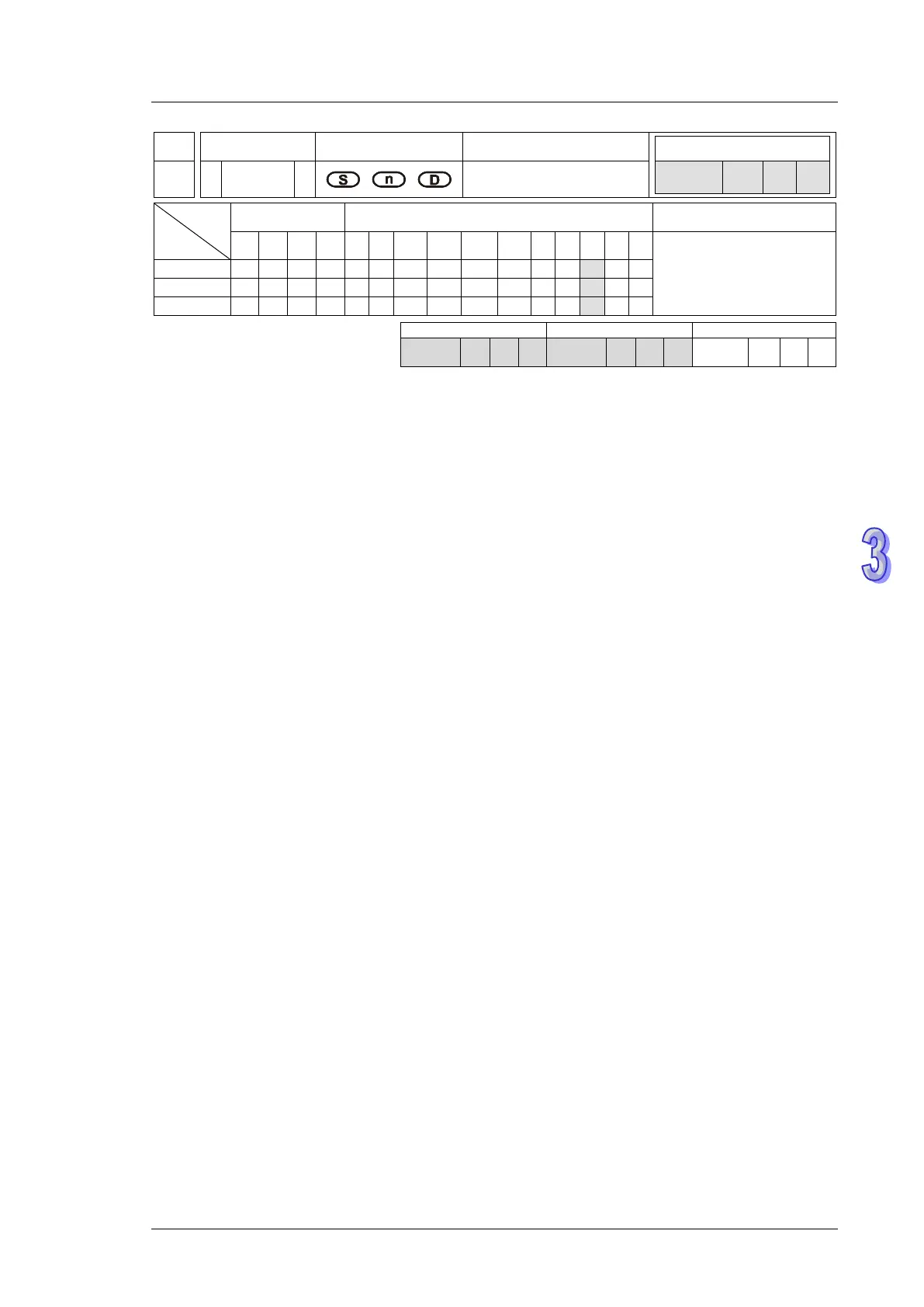

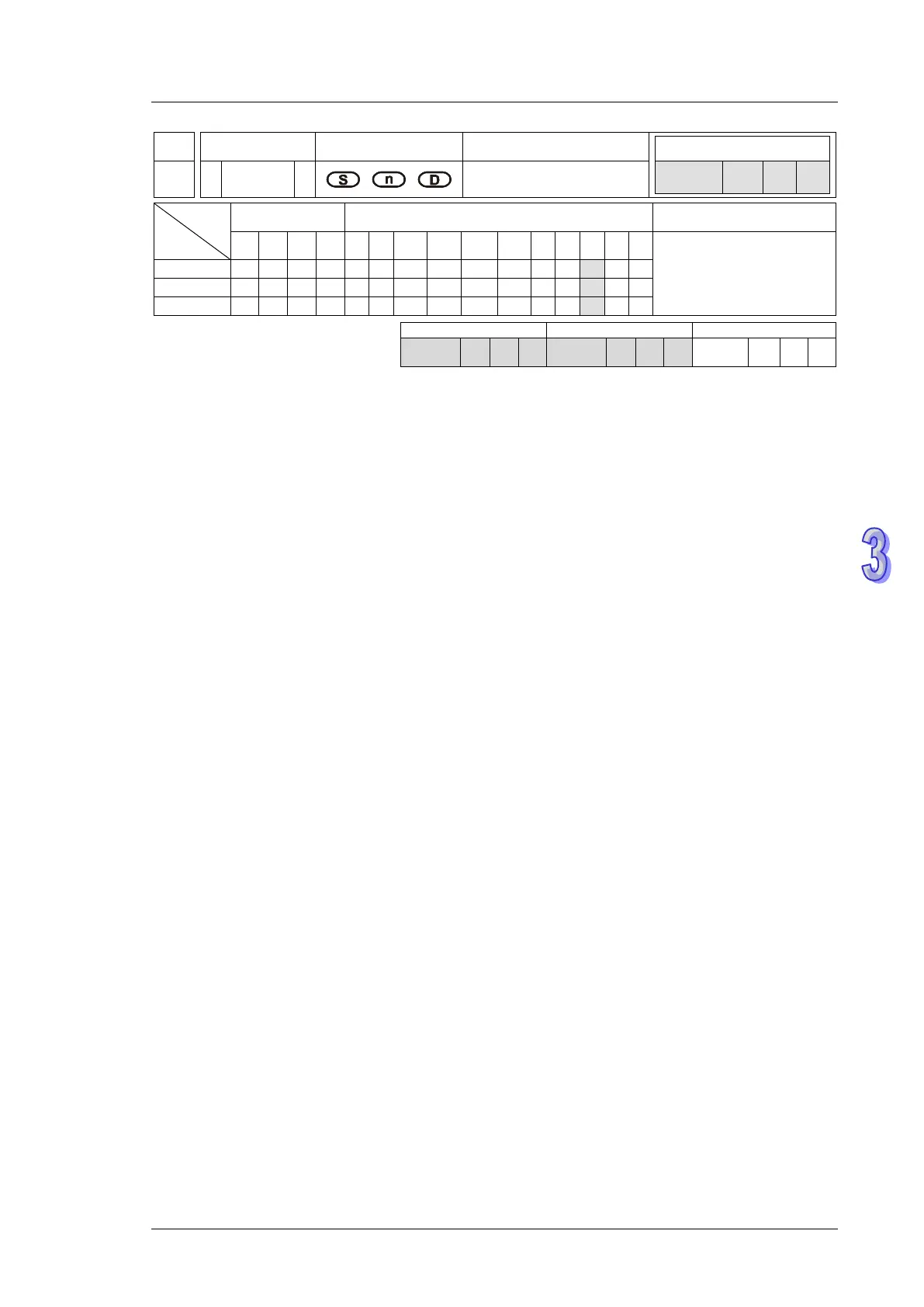

API

Mnemonic Operands Function

107 LRC P

LRC checksum

Type

OP

Bit Devices Word devices Program Steps

X Y M S K H KnX

KnY

KnM

KnS

T C D E F

LRC, LRCP: 7 steps

SS2

SX2

SS2

SX2

SS2

SX2

Operands:

S: Starting device for ASCII mode checksum n: Data length for LRC operation (n = K1~K256)

D: Starting device for storing the operation result

Explanations:

1. n: n must be an even number. If n is out of range, an error will occur and the instruction will not

be executed. At this time, M1067 and M1068 = ON and error code H’0E1A will be recorded in

D1067.

2. 16-bit mode: When LRC instruction operates with M1161 = OFF, hexadecimal data starting from

S is divided into high byte and low byte and the checksum operation is operated on n number of

bytes. After this, operation result will be stored in both hi-byte and low byte of D.

3. 8-bit mode: When LRC instruction operates with M1161 = ON, hexadecimal data starting from S

is divided into high byte (invalid) and low byte and the checksum operation is operated on n

number of low bytes. After this, operation result will be stored in low bytes of D (Consecutive 2

registers).

4. Flag: M1161 8/16-bit mode

Loading...

Loading...