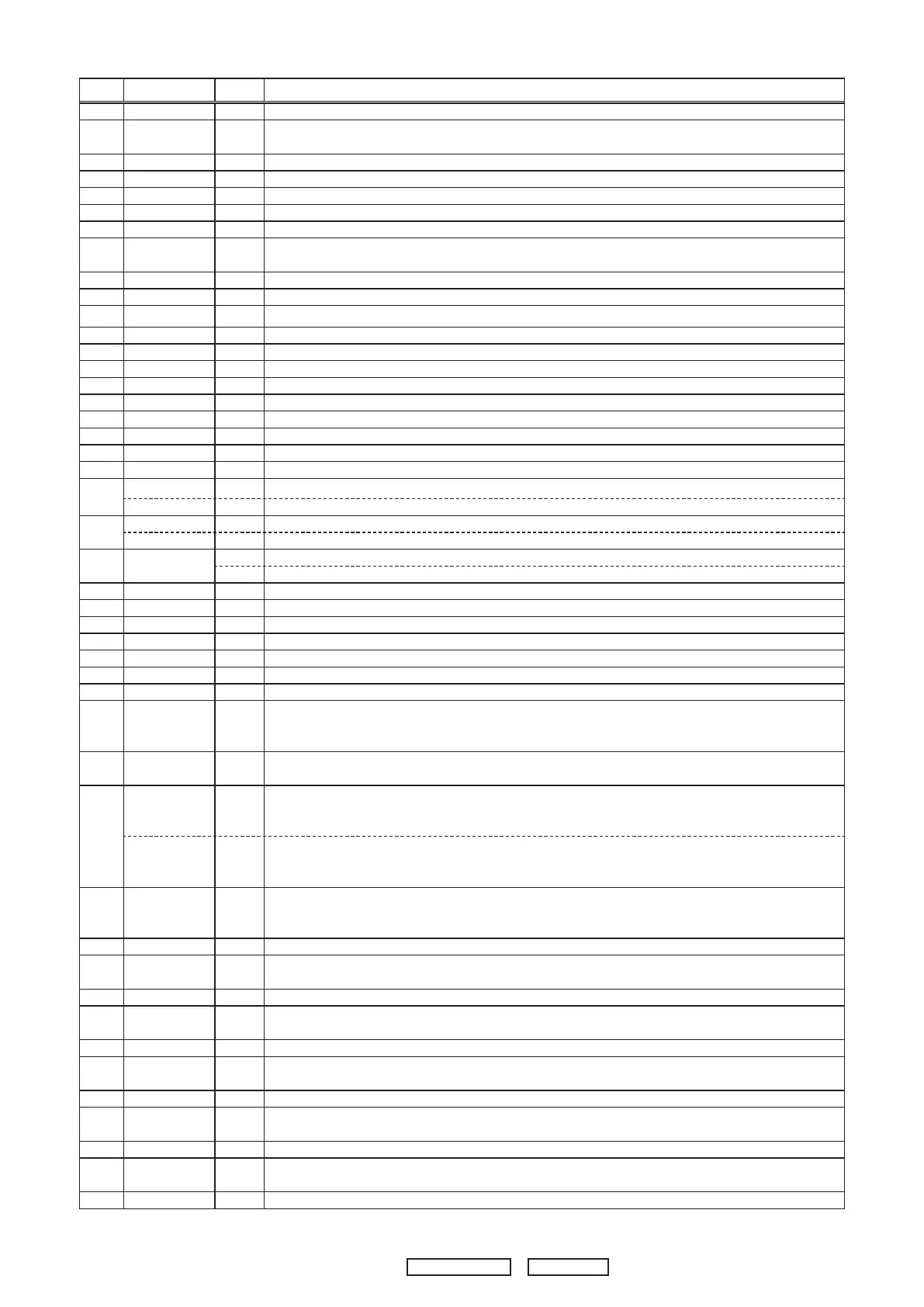

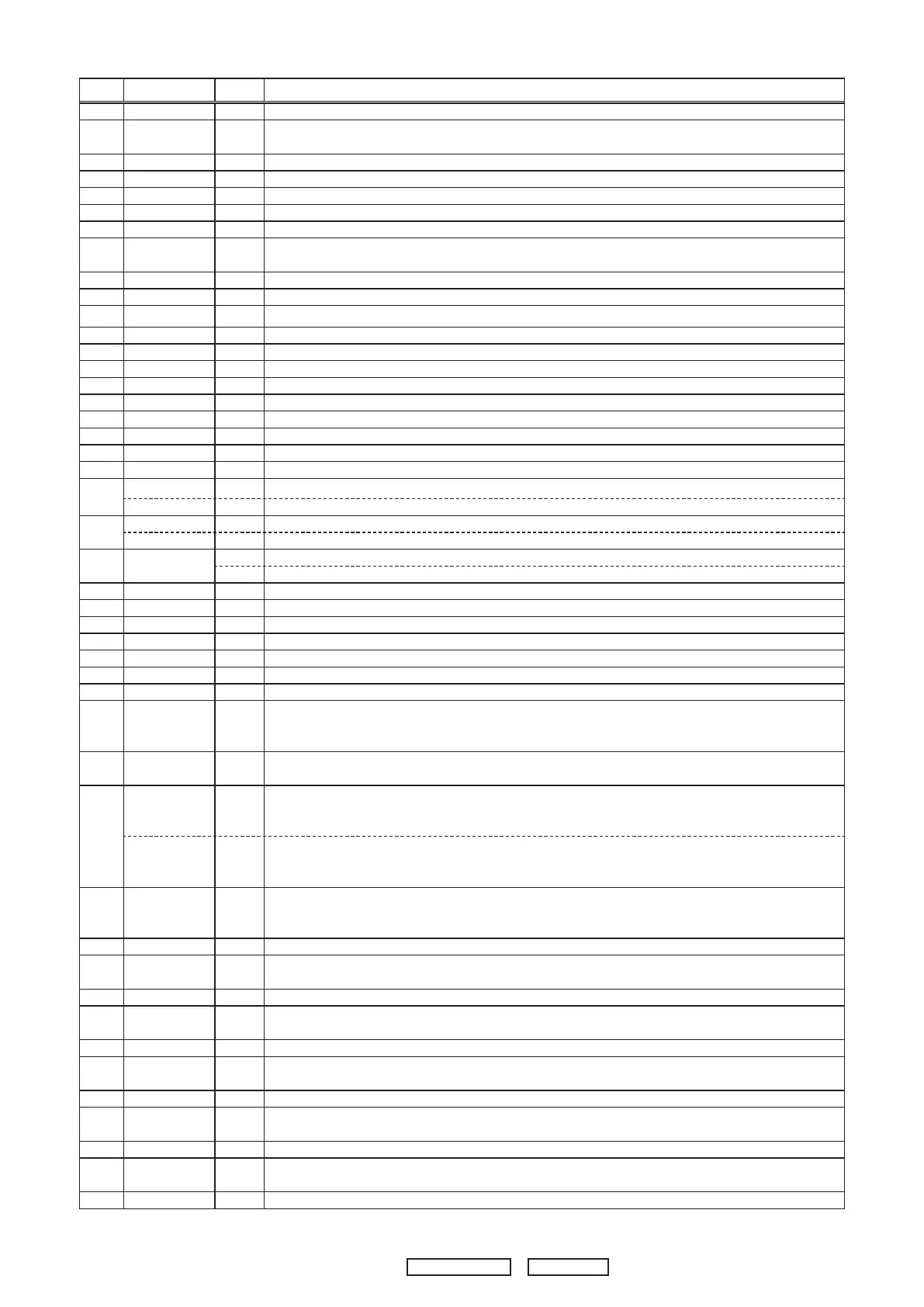

30

DHT-390XP AVR-390

PIN FUNCTION

No. Pin Name I/O Function

1 INT1 O Interrupt 1 Pin

2 BOUT O

Block-Start Output Pin for Receiver Input

"H" during rst 40 ames.

3 TVDD - Output Buffer Power Supply Pin, 2.7V~5.5V

4 DVDD - Digital Power Supply Pin, 4.5V~5.5V

5 DVSS - Digital Ground Pin

6 XTO O X'tal clock Output Pin

7 XTI I X'tal / External clock Input Pin

8 TEST3 I

Test 3 Pin

This pin should be connected to DVSS.

9 MCKO2 O Master Clock Output 2 Pin

10 MCKO1 O Master Clock Output 1 Pin

11 COUT O C-bit Output Pin for Receiver Input

12 UOUT O U-bit Output Pin for Receiver Input

13 VOUT O V-bit Output Pin for Receiver Input

14 SDTO2 O Audio Serial Data Output Pin (DIR/DIT part)

15 BICK2 I/O Audio Serial Data Clock Pin (DIR/DIT part)

16 LRCK2 I/O Channel Clock Pin (DIR/DIT part)

17 SDTO1 O Audio Serial Data Output Pin (ADC/DAC part)

18 BICK1 I/O Audio Serial Data Clock Pin (ADC/DAC part)

19 LRCK1 I/O Input Channel Clock Pin

20 CDTO O Control Data Output Pin in Serial Mode, I2C pin= "L"

21

CCLK I Control Data Clock Pin in Serial Mode, I2C pin= "L"

SCL I Control Data Clock Pin in Serial Mode, I2C pin= "H"

22

CDTI I Control Data Input Pin in Serial Mode, I2C pin= "L".

SDA I/O Control Data Pin in Serial Mode, I2C pin= "H".

23 CSN

I Chip Select Pin in Serial Mode, I2C pin= "L".

I This pin should be connected to DVSS, I2C pin= "H".

24 DAUX1 I AUX Audio Serial Data Input Pin (ADC/DAC part)

25 SDTI4 I DAC4 Audio Serial Data Input Pin

26 SDTI3 I DAC3 Audio Serial Data Input Pin

27 SDTI2 I DAC2 Audio Serial Data Input Pin

28 SDTI1 I DAC1 Audio Serial Data Input Pin

29 XTL1 I X'tal Frequency Select 0 Pin

30 XTL0 I X'tal Frequency Select 1 Pin

31 PDN I

Power-Down Mode Pin

When “L”, the AK4588 is powered-down, all output pin goes “L”, all registers are reset.

When CAD1-0 pins are changed, the AK4588 should be reset by PDN pin.

32 MASTER I

Master Mode Select Pin

“H”: Master mode, “L”: Slave mode

33

DZF2 O

Zero Input Detect 2 Pin (Table 13)

When the input data of the group 1 follow total 8192 LRCK cycles with “0” input data, this pin goes to

“H”. When RSTN1 bit is “0” or PWDAN bit is “0”, this pin goes to “H”.

OVF O

Analog Input Overow Detect Pin

This pin goes to “H” if the analog input of Lch or Rch overows. This pin becomes OVF pin if OVFE

bit is set to 1.

34 DZF1 O

Zero Input Detect 1 Pin (Table 13)

When the input data of the group 1 follow total 8192 LRCK cycles with “0” input data, this pin goes to “H”.

When RSTN1 bit is “0” or PWDAN bit is “0”, this pin goes to “H”.

35 LOUT4 O DAC4 Lch Analog Output Pin

36 NC -

No Connect pin

No internal bonding. This pin should be opened.

37 ROUT4 O DAC4 Rch Analog Output Pin

38 NC -

No Connect pin

No internal bonding. This pin should be opened.

39 LOUT3 O DAC3 Lch Analog Output Pin

40 NC -

No Connect pin

No internal bonding. This pin should be opened.

41 ROUT3 O DAC3 Rch Analog Output Pin

42 NC -

No Connect pin

No internal bonding. This pin should be opened.

43 LOUT2 O DAC2 Lch Analog Output Pin

44 NC -

No Connect pin

No internal bonding. This pin should be opened.

45 ROUT2 O DAC2 Rch Analog Output Pin

Loading...

Loading...