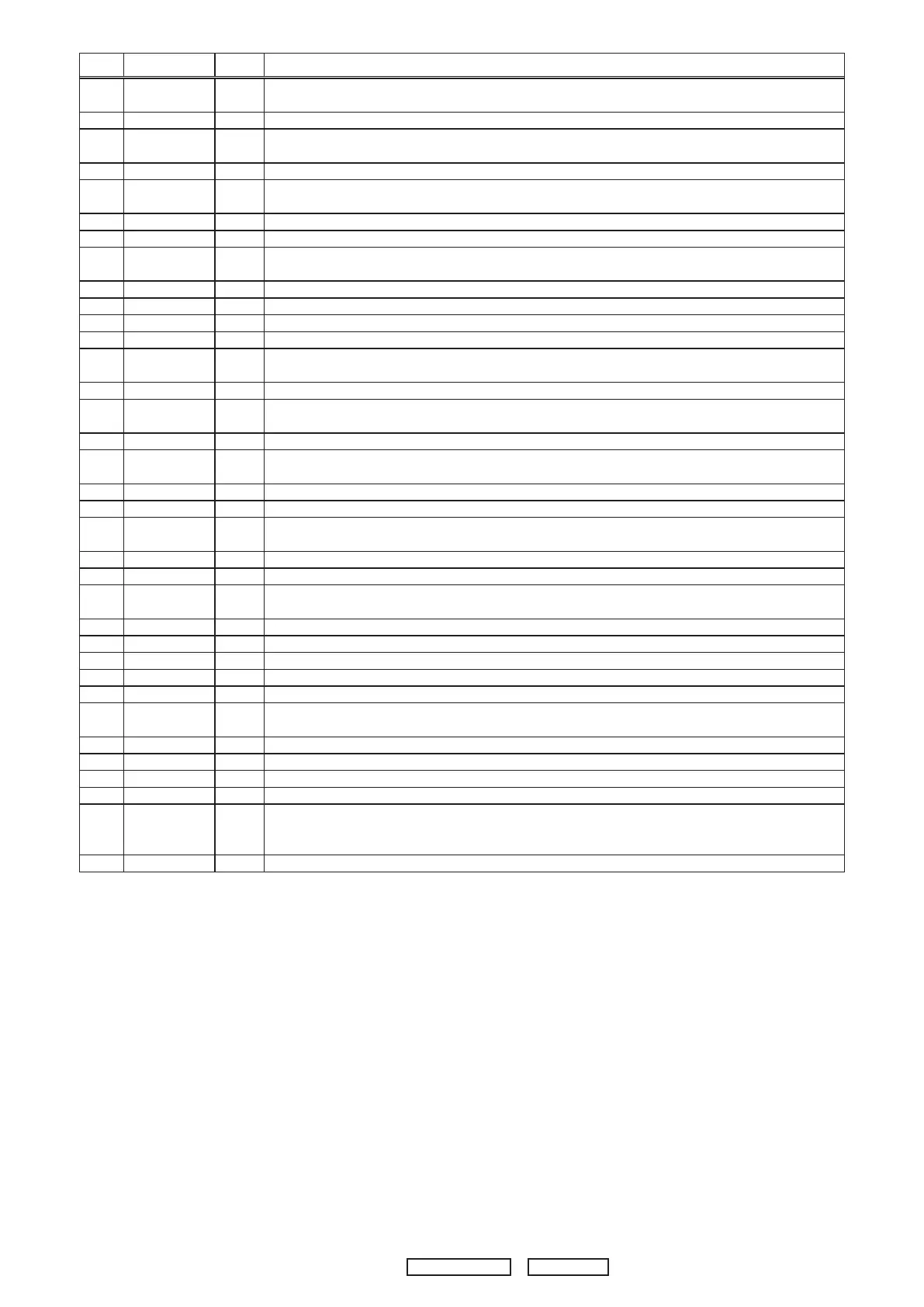

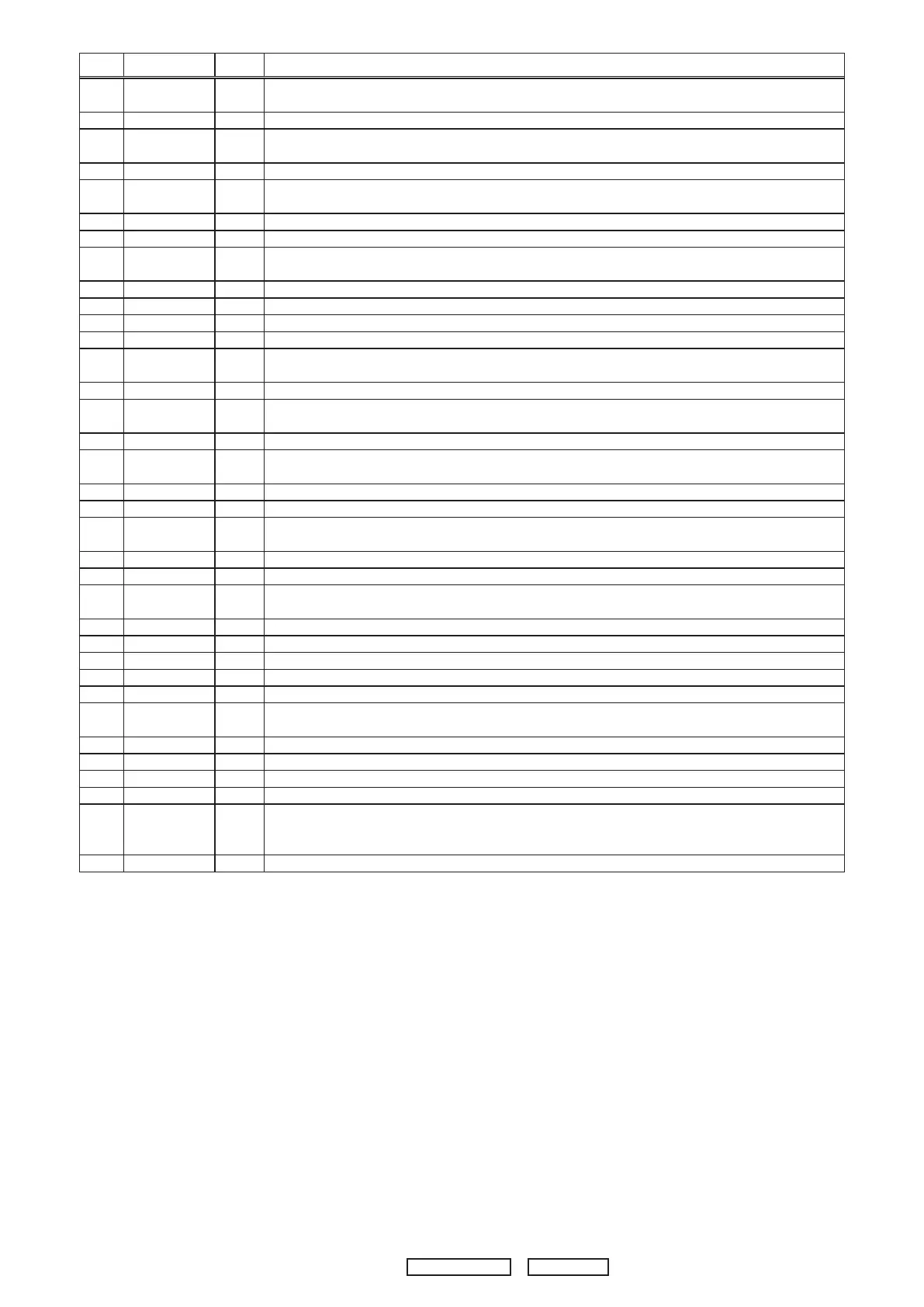

31

DHT-390XP AVR-390

No. Pin Name I/O Function

46 NC -

No Connect pin

No internal bonding. This pin should be opened.

47 LOUT1 O DAC1 Lch Analog Output Pin

48 NC -

No Connect pin

No internal bonding. This pin should be opened.

49 ROUT1 O DAC1 Rch Analog Output Pin

50 NC -

No Connect pin

No internal bonding. This pin should be opened.

51 LIN I Lch Analog Input Pin

52 RIN I Rch Analog Input Pin

53 VCOM -

Common Voltage Output Pin

2.2μF capacitor should be connected to AVSS externally.

54 VREFH - Positive Voltage Reference Input Pin, AVDD

55 AVDD - Analog Power Supply Pin, 4.5V~5.5V

56 AVSS - Analog Ground Pin, 0V

57 RX0 I Receiver Channel 0 Pin (Internal biased pin. Internally biased at PVDD/2)

58 NC -

No Connect pin

No internal bonding. This pin should be connected to PVSS.

59 RX1 I Receiver Channel 1 Pin (Internal biased pin. Internally biased at PVDD/2)

60 TEST1 I

Test 1 Pin

This pin should be connected to PVSS.

61 RX2 I Receiver Channel 2 Pin (Internal biased pin. Internally biased at PVDD/2)

62 NC -

No Connect pin

No internal bonding. This pin should be connected to PVSS.

63 RX3 I Receiver Channel 3 Pin (Internal biased pin. Internally biased at PVDD/2)

64 PVSS - PLL Ground pin

65 R -

External Resistor Pin

12kΩ +/-1% resistor should be connected to PVSS externally.

66 PVDD - PLL Power supply Pin, 4.5V~5.5V

67 RX4 I Receiver Channel 4 Pin (Internal biased pin. Internally biased at PVDD/2)

68 TEST2 I

Test 2 Pin

This pin should be connected to PVSS.

69 RX5 I Receiver Channel 5 Pin (Internal biased pin. Internally biased at PVDD/2)

70 CAD0 I Chip Address 0 Pin (ADC/DAC part)

71 RX6 I Receiver Channel 6 Pin (Internal biased pin. Internally biased at PVDD/2)

72 CAD1 I Chip Address 1 Pin (ADC/DAC part)

73 RX7 I Receiver Channel 7 Pin (Internal biased pin. Internally biased at PVDD/2)

74 I2C I

Control Mode Select Pin.

"L" : 4-wire Serial, "H" : I

2

C Bus

75 DAUX2 I Auxiliary Audio Data Input Pin (DIR/DIT part)

76 VIN

I V-bit Input Pin for Transmitter Output

77 MCLK I Master Clock Input Pin

78 TX0 O Transmit Channel (Through Data) Output 0 Pin

79 TX1 O

Transmit Channel Output1 pin

When TX bit = "0", Transmit Channel (Through Data) Output 1 Pin.

When TX bit = "1", Transmit Channel (DAUX2 Data) Output Pin (Default).

80 INT0 O Interrupt 0 Pin

Note: All input pins except internal biased pins and internal pull-down pin should not be left oating.

Loading...

Loading...