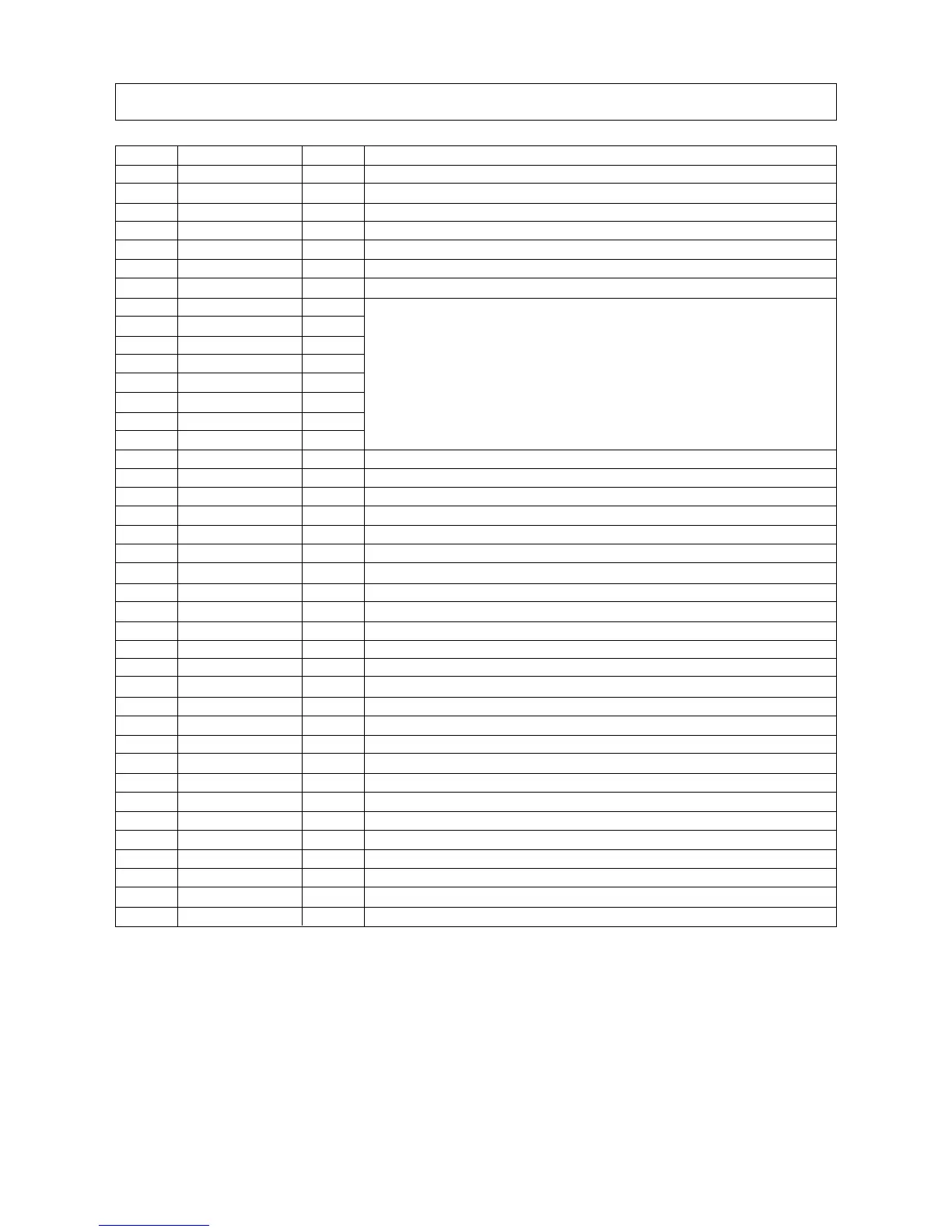

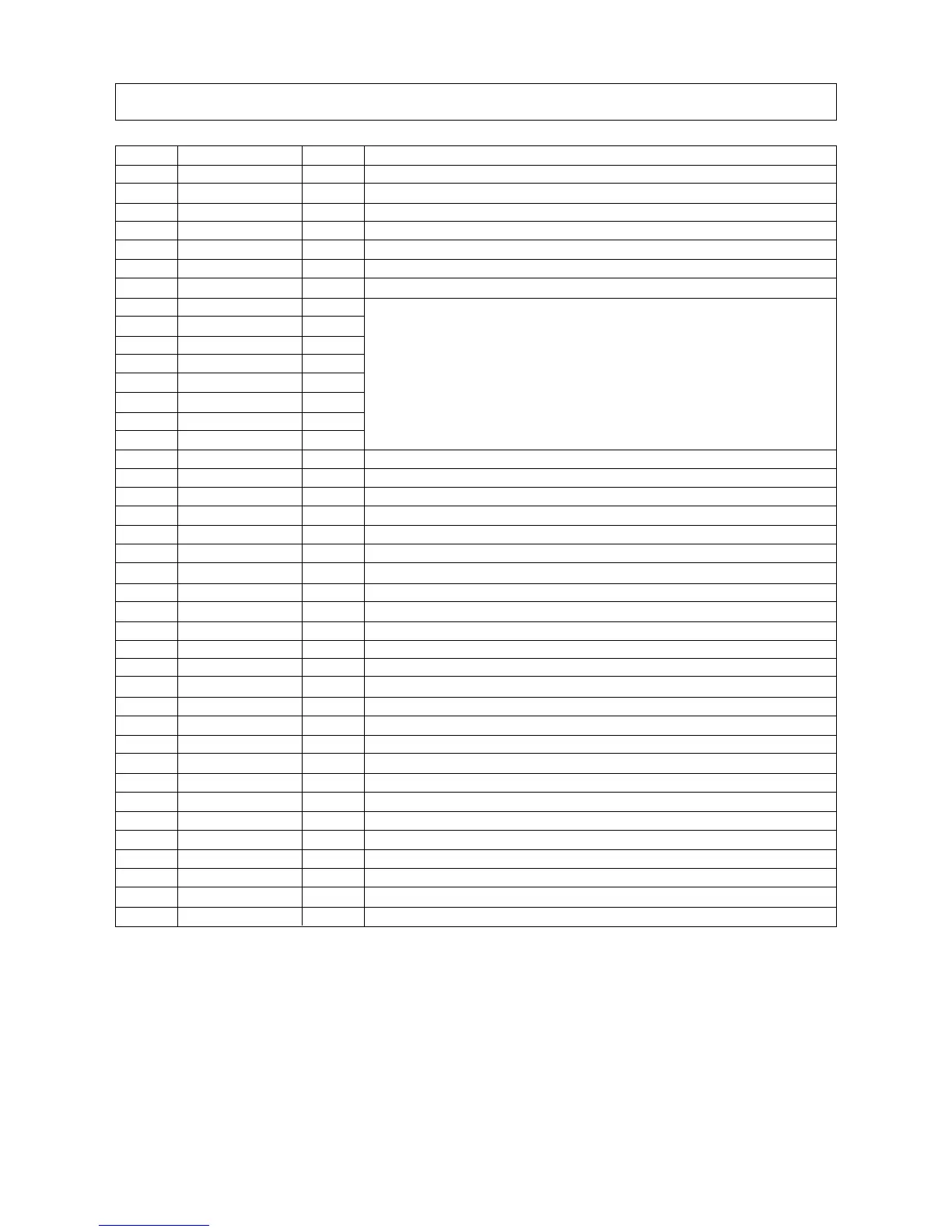

PIN No. Pin Name I/O Function

1,12,23 +VD1 - Digital Power supply. Normally +2.5v

2,13,24 DGND - Digital Ground

3 AUD3 O SPDIF transmitter output/Digital audio output(N.C)

4 WR I Host write strobe pin(connected to GND with an external resistor)

5 RD I Host parallel output enable pin(pulled up with an external resistor)

6 CS_DA I SPI Serial data input pin

7 CS_CK I Serial control clock input pin

8 EMAD7 I/O

9 EMAD6 I/O

10 EMAD5 I/O

11 EMAD4 I/O Serial data IN/OUTPUT pins(pulled up with an external resistor)

14 EMAD3 I/O

15 EMAD2 I/O

16 EMAD1 I/O

17 EMAD0 I/O

18 CS_CE I Host parallel chip select pin

19 SCDIO(AK_DOUT) O Serial control port data ouput pin

20 INTREQ O Control port interrupt request output pin

21 EXTMEM I/O External Memory Chip Selector(pulled up with an external resistor)

22 SDATAN1(SDI) I PCM audio data input number 1 pin

25 SCLKN1(BICK) I PCM audio input bit clock pin

26 LRCLKN1(LRCK) I PCM audio input sample rate clock pin

27 CMPDAT(SDI) I PCM audio data input number 2 pin

28 CMPCLK(BICK) I PCM audio input bit clock pin

29 CREQ(LRCK) I PCM audio input sample rate clock pin

30 CLKIN(XIN) I Master clock input(used external clock)

31 CLKSEL(GND) I DSP clock mode select pin: connect the GND

32 FILT1 Connects to an external filter for the on-chip phase-locked loop

33 FILT1 Connects to an external filter for the on-chip phase-locked loop

34 +2.5V - Analog Power supply for clock generator . Normally +2.5V

35 AGND - Analog ground supply for clock generator PLL.

36 RESET(CS_RST) I Master reset input pin

37 DBDATA - Reserved pin and should be pulled up with an external resistor.

38 DBCLK - Reserved pin and should be pulled up with an external resistor.

39 AUD2(SDO2) O PCM multi-format digital-audio data ouput2 pin

40 AUD1(SDO1) O PCM multi-format digital-audio data ouput1 pin

41 AUD0(SDO0) O PCM multi-format digital-audio data ouput0 pin

42 LRCLK I Audio output sample rate clock pin

43 SCLK(BICK) I Audio ouput bit clock pin

44 MCLK I Audio master clock output pin

AUDIO DSP (CS493263 - CLG : IC75)

Loading...

Loading...