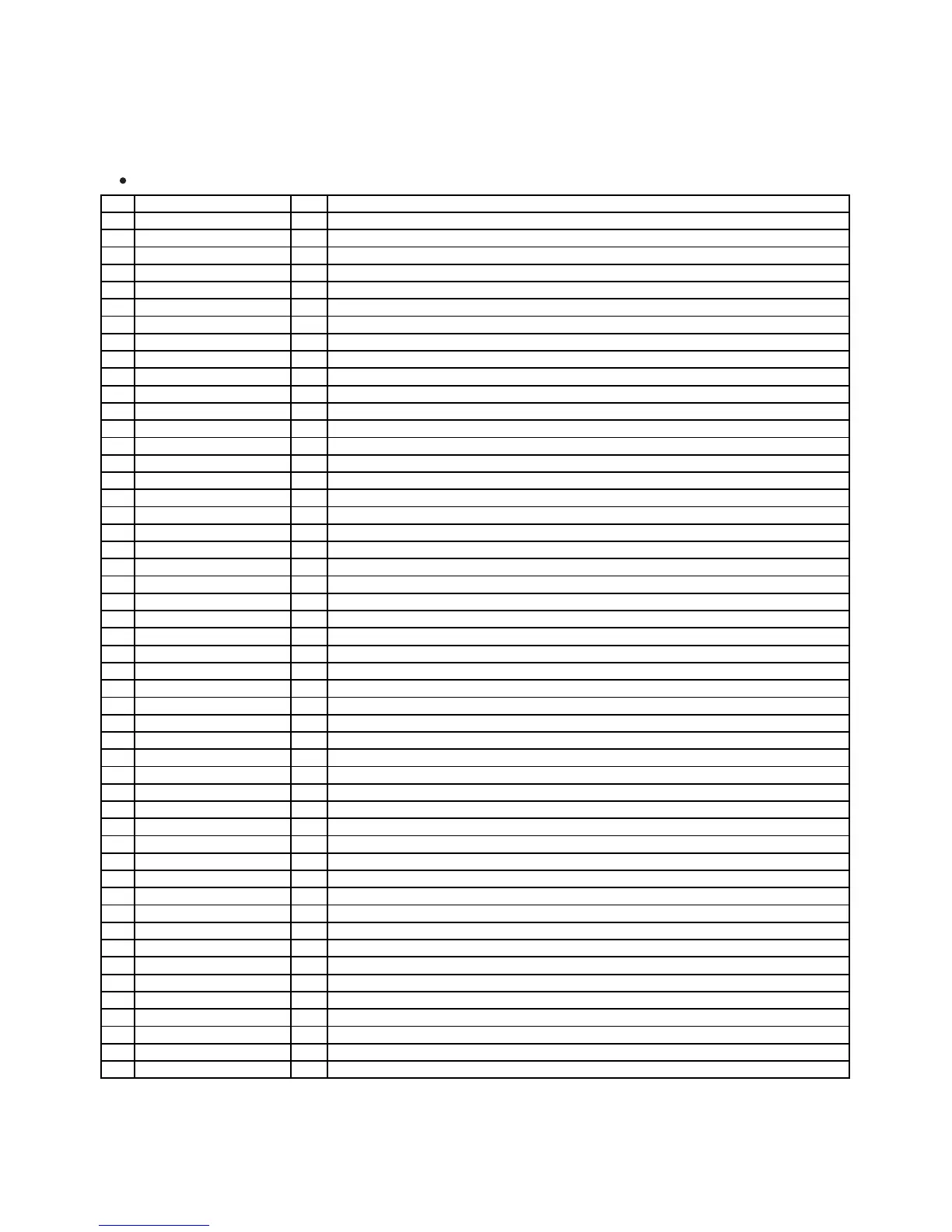

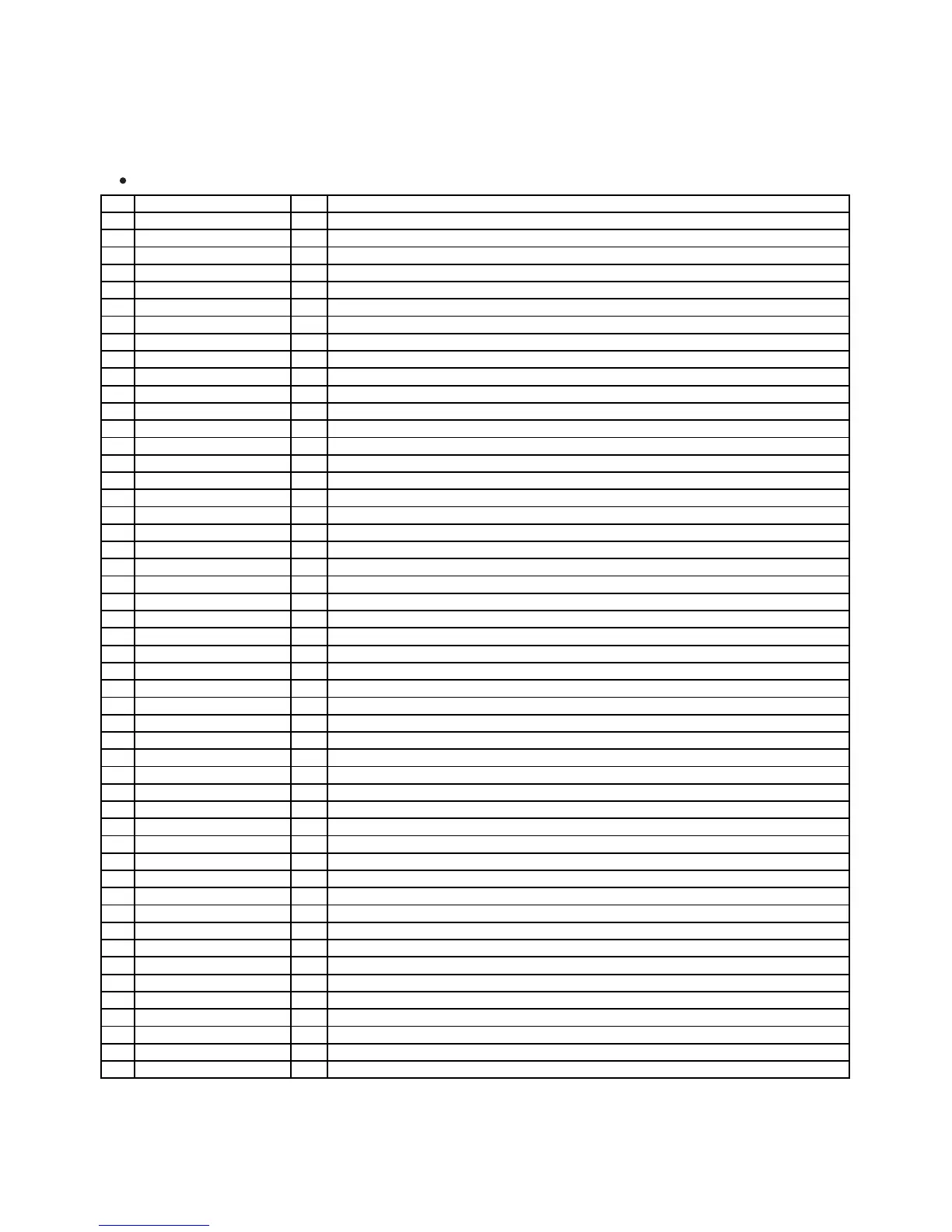

No. PIN MANE I/O

1

VREF (+5.0V) I

2

+5.0V I

3

NC I/O

4

OSD_DATA I/O

5

OSD_CLK I/O

6

HP_VOL

I/O

7

FE.AGC_O(M) I/O

8 DATA_OUT(FC)

I/O

9 DATA_IN(FC)

I/O

10 CLK(FC)

I/O

11

EDID_PROTECT I/O

12

TRAP_MAIN I/O

13

GND I

14

CNVSS(FLASH) I

15

DSUB COMP I/O

16

RGBSW I/O

17

RESET I

18

16MHz oscillation O

19

GND I

20

16MHz oscillation I

21

+5.0V I

22

NMI(+5.0V) I

23

RMCON(AVC) I/O

24

V.FREQ_2(VIDEO) I/O

25

V.FREQ_1/3 I/O

26

SCV.SYNC I/O

27

IRQ

PM-IRQ) I/O

28

MCV.SYNC I/O

29

POWER_LED I/O

30

H.FREQ_2(VIDEO) I/O

31

PDP_WVGA_LCD_SW_2 I/O

32

H.FREQ_1/_3 I/O

33

PDWN

I/O

34

RXD2 I/O

35

TXD2 I/O

36

TXD1(RS232C/FLASH) I/O

37

I

38

RXD1(RS232C/FLASH) I/O

39

I

40

SCLK(FLASH) I/O

41

BUSY(FLASH) I/O

42

TXD0(PDP) I/O

43

RXD0(PDP) I/O

44

SDA4(panel) I/O

45

SCL4(panel) I/O

46

M_ENABLE I/O

47

M_SCLK I/O

48

M_SDA I/O

49

M_WAKEUP I/O

50

PDPGO(PM_ON) I/O

5V

NC

OSD DATA

OSD CLK

GND

CNVSS(FLASH)

TRAP-MAIN

FUNCTION

5V

Head Phone Volume

Memory Protect

AGC Voltage(F/E)

FC DATA

FC CLOCK

FC DATA

SYNC-SW

SYNC-SW

RESET

OSC-OUT

GND

OSC-IN

5V

5V PULL UP

IR Signal

TA1370(LA7213), COMPONENT2

TA1370(LA7213), COMPONENT(Main)/ DSUB COMPONENT

CVBS for SYNC Detection(Sub Picture)

PANEL MODULE Condition(L:Normal,H:Erroe)

CVBS for SYNC Detection(Main Picture)

LLED ON(Power Save)

TA1370(LA7213), COMPONENT2

PDP/42WVGA/LCD detection

TA1370(LA7213), COMPONENT1(Main), D-SUB

RESERVE(LVDS Power Down mode(PANEL))

DTT

DATA(RS-232C)

5V

DATA(RS-232C)

DTT

GND

CLOCK(FRASH MEMORY Writing)

BUSY(FRASH MEMORY Writing)

I

2

C-BUS Contorol DATA

Ether Net

Ether Net

I

2

C-BUS Contorol CLOCK

Media Enable

Media Clock

Media Data

Media Wakeup

PDP PALEL Contorol

Loading...

Loading...