8662A Option H25

08862-92039

Page 9 of 17

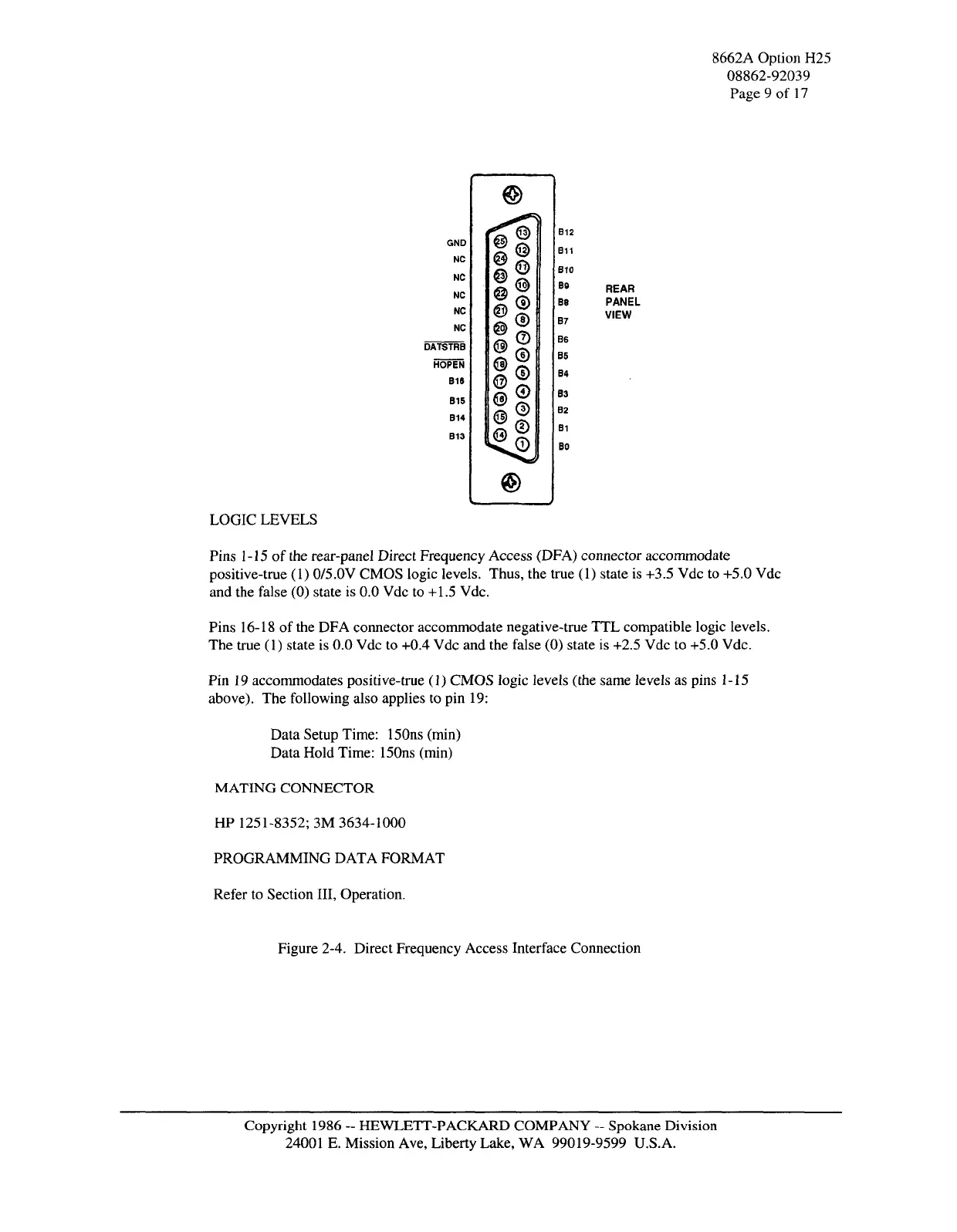

REAR

PANEL

VIEW

LOGIC LEVELS

Pins 1-15 of the rear-panel Direct Frequency Access (DFA) connector accommodate

positive-true (1)

0/5.0V

CMOS logic levels. Thus, the true (1) state is +3.5 Vdc to +5.0 Vdc

and the false (0) state is 0.0 Vdc to +1.5 Vdc.

Pins 16-18 of the DFA connector accommodate negative-true TTL compatible logic levels.

The true (1) state is 0.0 Vdc to +0.4 Vdc and the false (0) state is +2.5 Vdc to +5.0 Vdc.

Pin 19 accommodates positive-true (1) CMOS logic levels (the same levels as pins 1-15

above).

The following also applies to pin 19:

Data Setup Time: 150ns (min)

Data Hold Time: 150ns (min)

MATING CONNECTOR

HP 1251-8352; 3M 3634-1000

PROGRAMMING DATA FORMAT

Refer to Section III, Operation.

Figure 2-4. Direct Frequency Access Interface Connection

Copyright 1986 - HEWLETT-PACKARD COMPANY ~ Spokane Division

24001 E. Mission Ave, Liberty Lake, WA 99019-9599 U.S.A.

Loading...

Loading...