4-4 www.hp.com Technical Reference Guide

System Support

Link Layer

The link layer provides data integrity by adding a sequence information prefix and a CRC suffix

to the packet created by the transaction layer. Flow-control methods ensure that a packet will

only be transferred if the receiving device is ready to accomodate it. A corrupted packet will be

automatically re-sent.

Physical Layer

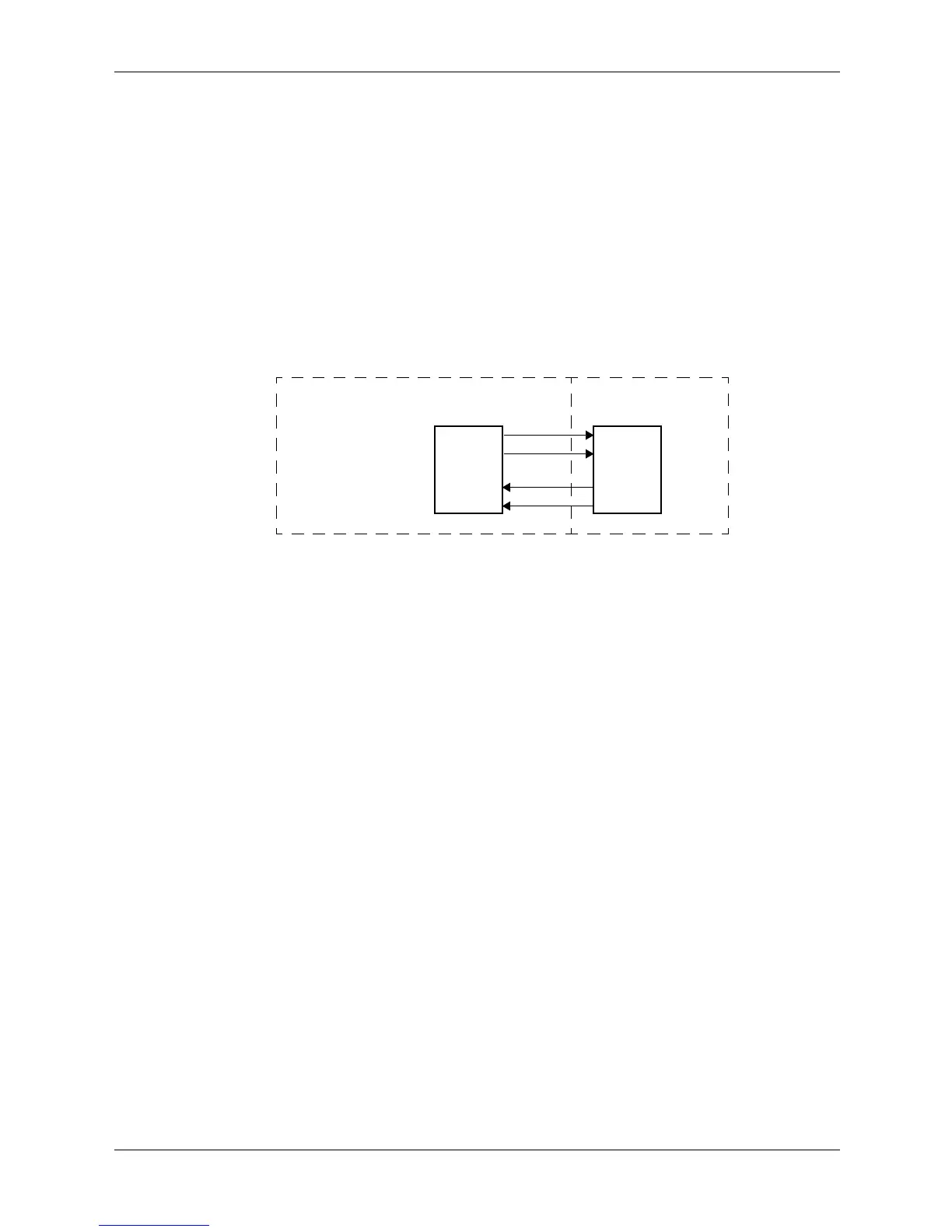

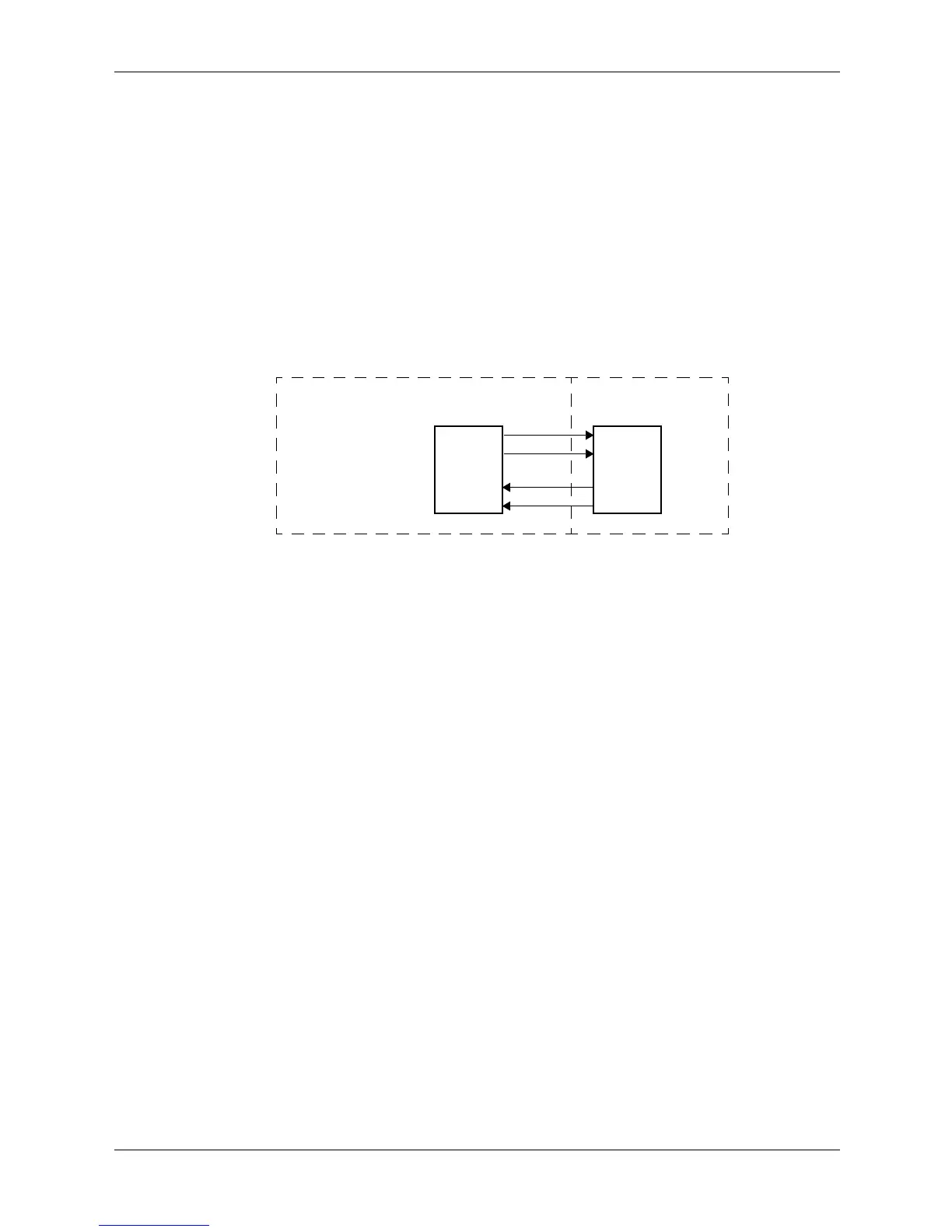

The PCI Express bus uses a point-to-point, high-speed TX/RX serial lane topology. One or more

full-duplex lanes transfer data serially, and the design allows for scalability depending on

end-point capabilities. Each lane consists of two differential pairs of signal paths; one for

transmit, one for receive (Figure 4-1).

Figure 4-1. PCI Express Bus Lane

Each byte is transferred using 8b/10b encoding. which embeds the clock signal with the data.

Operating at a 2.5 Gigabit transfer rate, a single lane can provide a data flow of 200 MBps. The

bandwidth is increased if additional lanes are available for use. During the initialization process,

two PCI Express devices will negotiate for the number of lanes available and the speed the link

can operate at. In a x1 (single lane) interface, all data bytes are transferred serially over the lane.

In a multi-lane interface, data bytes are distributed across the lanes using a multiplex scheme.

4.2.3 Option ROM Mapping

During POST, the PCI bus is scanned for devices that contain their own specific firmware in

ROM. Such option ROM data, if detected, is loaded into system memory's DOS compatibility

area (refer to the system memory map shown in chapter 3).

4.2.4 PCI Interrupts

Eight interrupt signals (INTA- thru INTH-) are available for use by PCI devices. These signals

may be generated by on-board PCI devices or by devices installed in the PCI slots. For more

information on interrupts including PCI interrupt mapping refer to the “System Resources”

section 4.3.

4.2.5 PCI Power Management Support

This system complies with the PCI Power Management Interface Specification (rev 1.0). The

PCI Power Management Enable (PME-) signal is supported by the chipset and allows compliant

PCI peripherals to initiate the power management routine.

Device A

Device B

TX

System Board

PCI Express Card

RX

Loading...

Loading...