E The Transfer Width Exponent (E) is two to the transfer width exponent bytes wide. Valid data

transfer widths are 8 bits (E = 00h) and 16 bits (E = 01h). Value of E greater than 01h are

reserved.

9.1.3.1 Transfer Width Negotiation Started by the Initiator

If the Initiator recognizes that negotiation is required and sends a Wide Data Transfer Request message out,

the Target responds by changing to the Message In phase and sending a Wide Data Transfer Request

message in to the Initiator prior to transfer any additional message bytes (or any other Information phase

bytes) from the Initiator. This provides an interlock during the data transfer width negotiation.

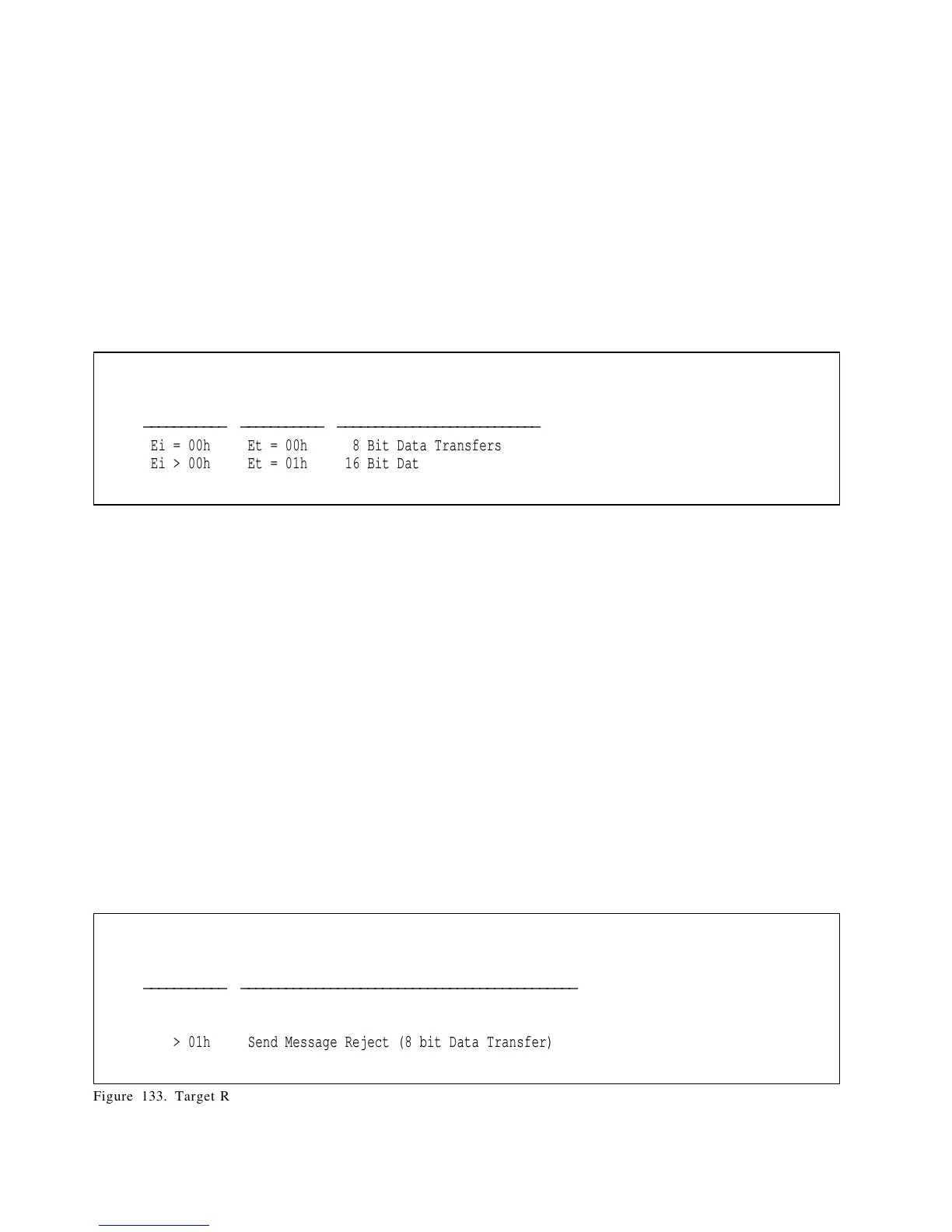

The Drive responds to each Initiator requested transfer width exponent as shown in the following table.

Target

Initiator Target Data Transfer

Request Response Width

ÄÄÄÄÄÄÄÄÄÄÄ ÄÄÄÄÄÄÄÄÄÄÄ ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

Ei = 00h Et = 00h 8 Bit Data Transfers

Ei > 00h Et = 01h 16 Bit Data Transfers

Figure 132. Initiator Request/Target Response

If following the Target's response above the Initiator asserts the ATN signal and the first message received is

either a Massage Parity Error or a Message Reject message, the Target negates the data transfer width agree-

ment and goes to 8 bits mode. For the Massage Parity Error case, the implied data transfer width agreement

is reinstated if the Target successfully retransmits the Wide Data Transfer Request message to the Initiator.

For any other message, the Target completes negotiation and goes to the negotiated data transfer width.

9.1.3.2 Transfer Width Negotiation Started by the Target

If the Target recognizes that negotiation is required, the Target sends a Wide Data Transfer Request message

to the Initiator with the transfer width exponent equal to 1 (E = 01h). The Initiator must respond by

asserting the ATN signal prior to its release of ACK for the REQ/ACK handshake of the last byte of the

Wide Data Transfer Request message. This provides an interlock during the wide data transfer negotiation.

If the Initiator does not assert the ATN signal, the Target goes to 8 bit mode. If the Initiator does assert the

ATN signal, the Target changes to the Message Out phase and receives a message from the Initiator.

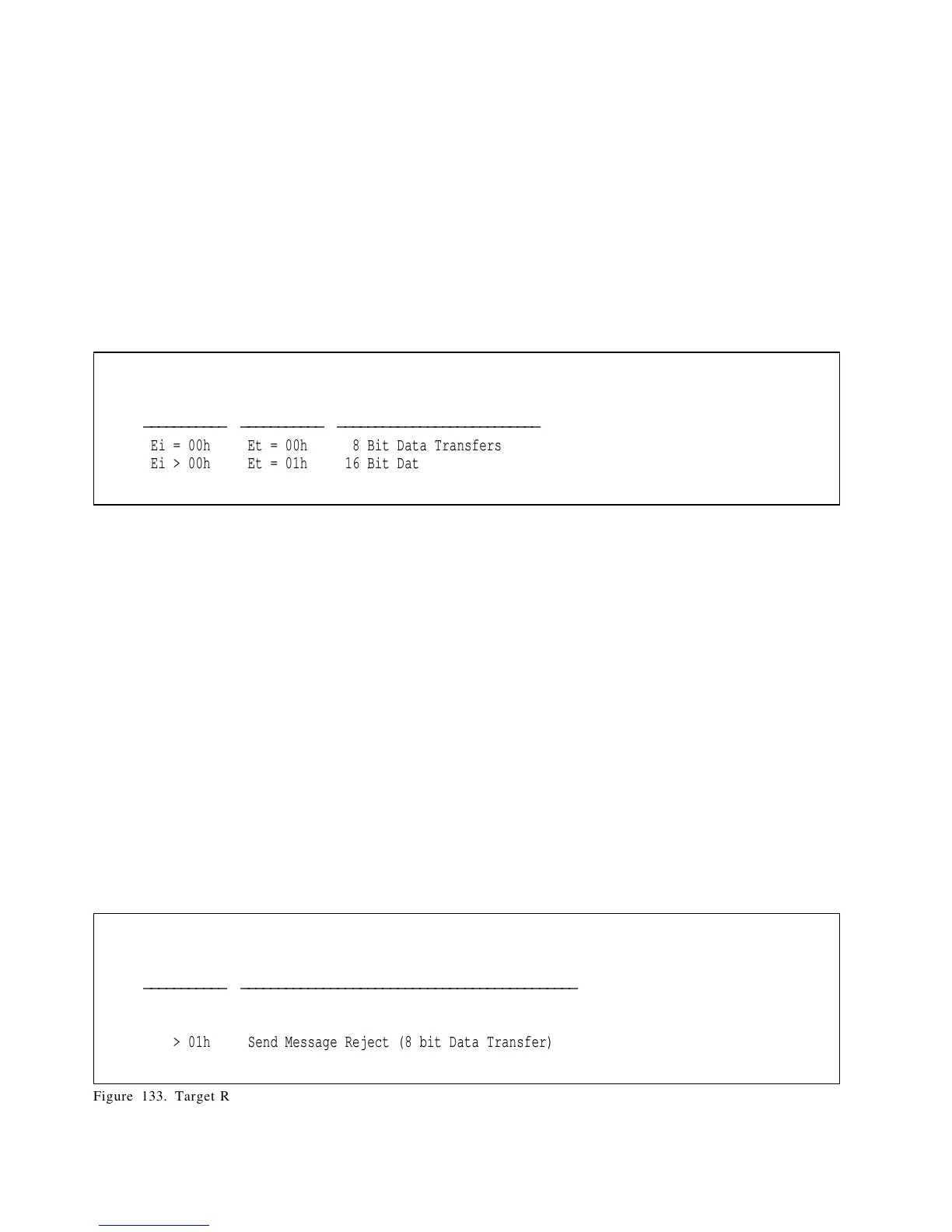

If the first message received is a Wide Data Transfer Request message, the Target establishes the new data

transfer mode. The Drive interprets the Initiator corresponding transfer width exponent as shown in the

following table.

Target

Initiator Data Transfer

Request Width

ÄÄÄÄÄÄÄÄÄÄÄ ÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄÄ

Ei = 00h 8 Bit Data Transfers

Ei = 01h 16 Bit Data Transfers

Ei > 01h Send Message Reject (8 bit Data Transfer)

Figure 133. Target Request to Initiator

168 OEM Spec. of DDRS-3xxxx

Loading...

Loading...