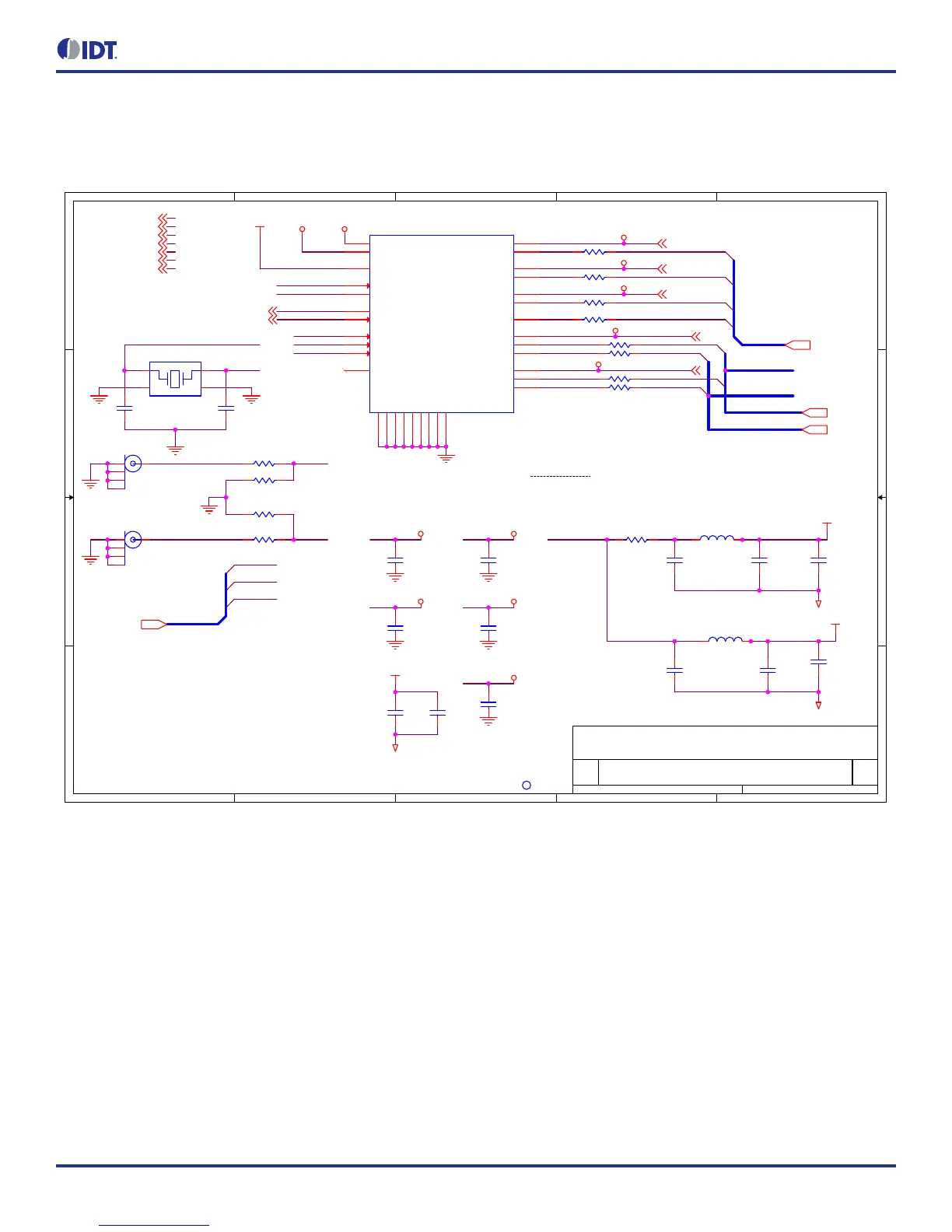

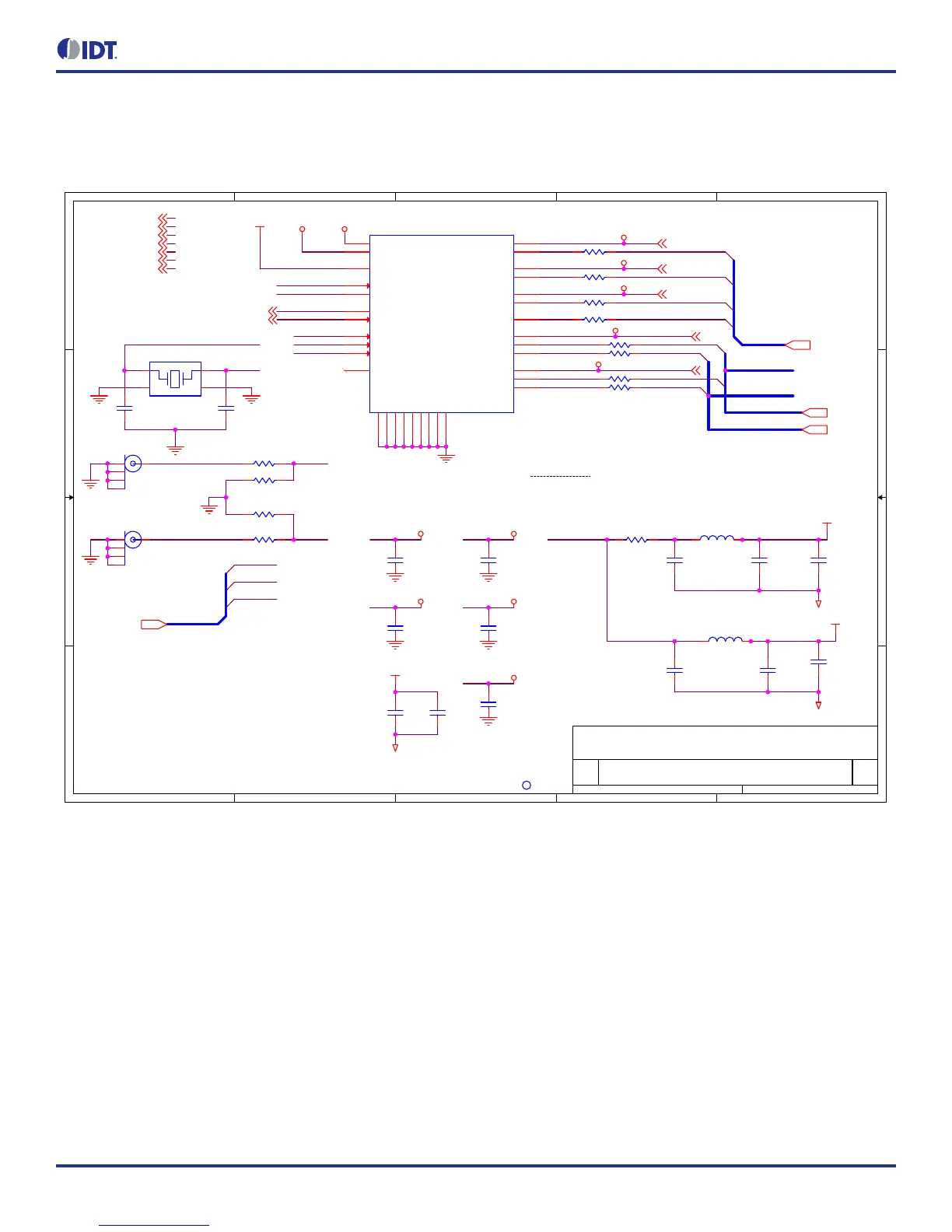

Figure 5. Evaluation Board Schematic (1)

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Layout notes.

2.Do not share crystal load

3.Route power from bead through

4.Do not share ground vias. One

ground pin one ground via.

1.Separate Xout and Xin traces

by at least 3 x the trace width.

other components.

capacitor ground via with

then to clock chip Vdd pad.

through 0.1uF capacitor pad

bulk capacitor pad then

grounded but is not required.

5.Exposed pad should be

Locate near U1.6

Locate near DUT

power pin

CLKINB

CLKIN

SCL_DFC1

SDA_DFC0

SER1

SER2

SER3

SE_1

SE_2

SE_3

OE1

OE2

OE3

SER4

SE_4

SE_[4:1]

CLKIN

CLKINB

GND

CLKIN_CONN

CLKINB_CONN

CLKIN

CLKINB

OE[3:1]

OE3

OE2

DIFFRT1

DIFFRC1

DIFFRC2

DIFFRT2

OE1

DIFF_T1

DIFF_C1

DIFF_C2

DIFF_T2

DIFF_T[2:1]

DIFF_C[2:1]

DIFF_T[2:1]

DIFF_C[2:1]

VDDSE2

VDDSE3

Node#3

VDDA_VDDD1

SE_[4:1]

OE[3:1]

DIFF_T[2:1]

DIFF_C[2:1]

VBAT_PS VDDD VDDA

VDDSE1

VDDSE2

VDDSE3

VDDDIFF1

VDDDIFF2

VBAT_PS

GND

VDDDIFF1

VDDDIFF2

VDDSE1

VDDSE2

VDDSE3

VDDA

GND

GND

VDDD

SDA_DFC0

2,3

SCL_DFC1

2,3

VDDSE1

1,3,4

VDDSE2

1,3,4

VDDSE3

1,3,4

VDDDIFF1

4

VDDDIFF2

4

VDDA_VDDD1

3,4

VDDSE1

1,3,4

VDDSE2

1,3,4

VDDSE3

1,3,4

VDDDIF1

4

VDDDIF2

4

VDDD

4

Size

Document Number Re v

Date: Sheet

of

C1

Integrated Device Technology

A

14Friday, November 04, 2016

5L35023/5P35023

San Jose, CA

Size

Document Number Re v

Date: Sheet

of

C1

Integrated Device Technology

A

14Friday, November 04, 2016

5L35023/5P35023

San Jose, CA

Size

Document Number Re v

Date: Sheet

of

C1

Integrated Device Technology

A

14Friday, November 04, 2016

5L35023/5P35023

San Jose, CA

R8

0_NP

1 2

U1

5P53023

VDDA

1

VDDD

9

VBAT

6

CLKINB/X2

5

CLKIN/X1

4

SDA/DFC0

2

SCL/DFC1

3

OE2

10

OE1

15

OE3

21

NC

7

VDDSE1

13

SE1

14

VDDSE2

11

SE2

12

VDDSE3

20

SE3

19

REF

8

VDDDIFF1

16

DIFF1

18

DIFF1B

17

VDDDIFF2

22

DIFF2

24

DIFF2B

23

TPAD1

25

TPAD2

26

TPAD3

27

TPAD4

28

TPAD5

29

TPAD6

30

TPAD7

31

TPAD8

32

TPAD9

33

R4 33

1 2

R59

2.2

1 2

J1

CON SMA4

12

3

4

5

FB4

BLM18AG601SN1D

1 2

C25

0.1 uF

12

C42

0.1 uF

12

C26

10 uF

12

C48

0.1 uF

12

R80 33

1 2

C33

0.1 uF

12

C30

0.1 uF

12

C54 10 uF

12

R1 33

1 2

R79 33

1 2

C16.8 pF

12

R2 33

1 2

FB5

BLM18AG601SN1D

1 2

C26.8 pF

12

R3 33

1 2

C50 0.1 uF

12

J2

CON SMA4

12

3

4

5

C31

0.1 uF

12

GNDGND

Y1

25 MHz 8 pF

4

1

2

3

R81 33

1 2

C53

0.1 uF

12

R5

0_NP

1 2

C34

0.1 uF

12

R82 33

1 2

R6

49.9_NP

1 2

C37

0.1 uF

12

LOGO1

R7

49.9_NP

1 2

C43

10 uF

12

Loading...

Loading...