80960KB

9

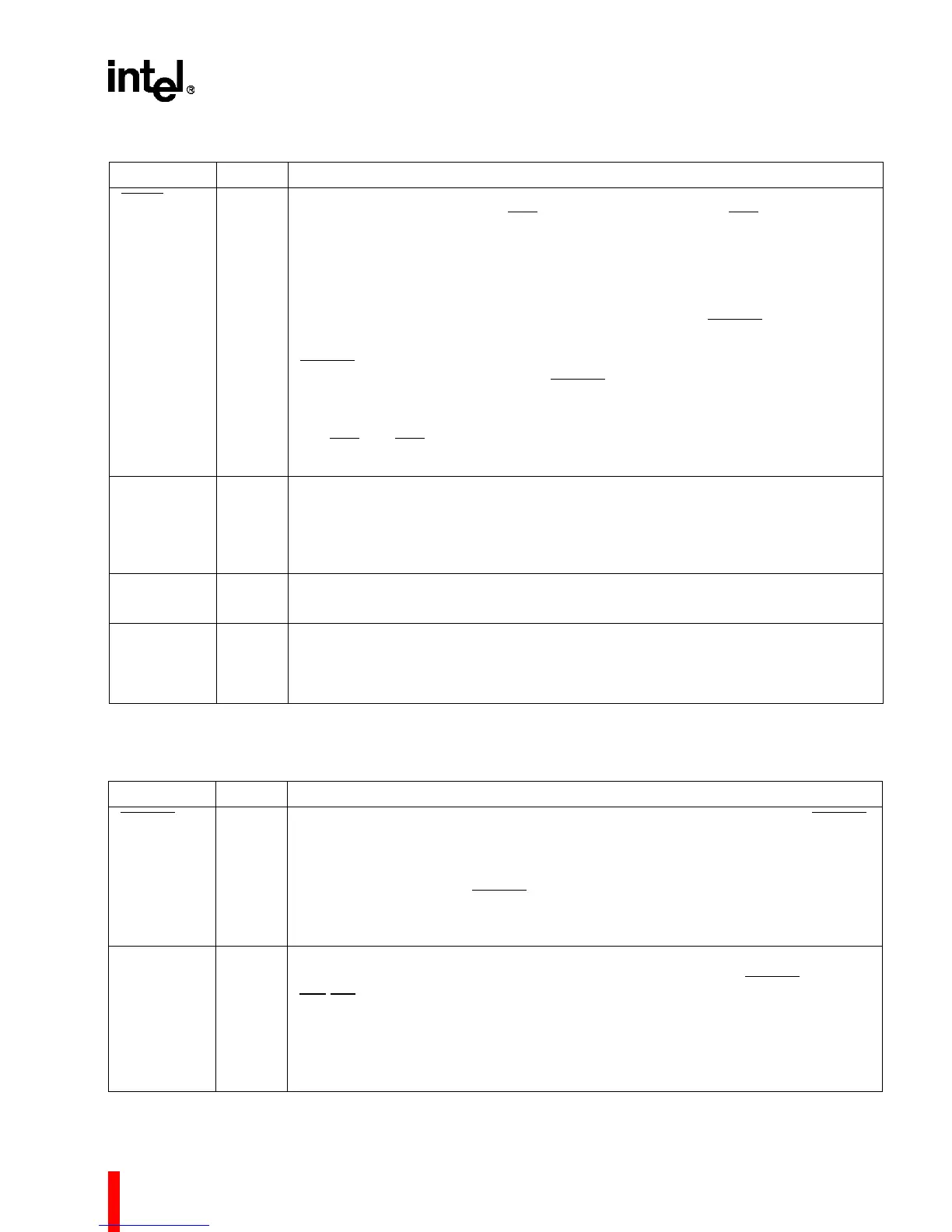

BE3:0 O

O.D.

BYTE ENABLE LINES specify the data bytes (up to four) on the bus which are

used in the current bus cycle. BE3

corresponds to LAD31:24; BE0 corresponds to

LAD7:0.

The byte enables are provided in advance of data:

Byte enables asserted during T

a

specify the bytes of the first data word.

Byte enables asserted during T

d

specify the bytes of the next data word, if any

(the word to be transmitted following the next assertion of READY

).

Byte enables that occur during T

d

cycles that precede the last assertion of

READY

are undefined. Byte enables are latched on-chip and remain constant

from one T

d

cycle to the next when READY is not asserted.

For reads, byte enables specify the byte(s) that the processor will actually use.

L-Bus agents are required to assert only adjacent byte enables (e.g., asserting

just BE0

and BE2 is not permitted) and are required to assert at least one byte

enable. Address bits A

0

and A

1

can be decoded externally from the byte enables.

HOLD I HOLD: A request from an external bus master to acquire the bus. When the

processor receives HOLD and grants bus control to another master, it floats its

three-state bus lines and open-drain control lines, asserts HLDA and enters the

T

h

state. When HOLD deasserts, the processor deasserts HLDA and enters the

T

i

or T

a

state.

HLDA O

T. S .

HOLD ACKNOWLEDGE: Notifies an external bus master that the processor has

relinquished control of the bus.

CACHE O

T. S.

CACHE indicates when an access is cacheable during a T

a

cycle. It is not

asserted during any synchronous access, such as a synchronous load or move

instruction used for sending an IAC message. The CACHE signal floats to a high

impedance state when the processor is idle.

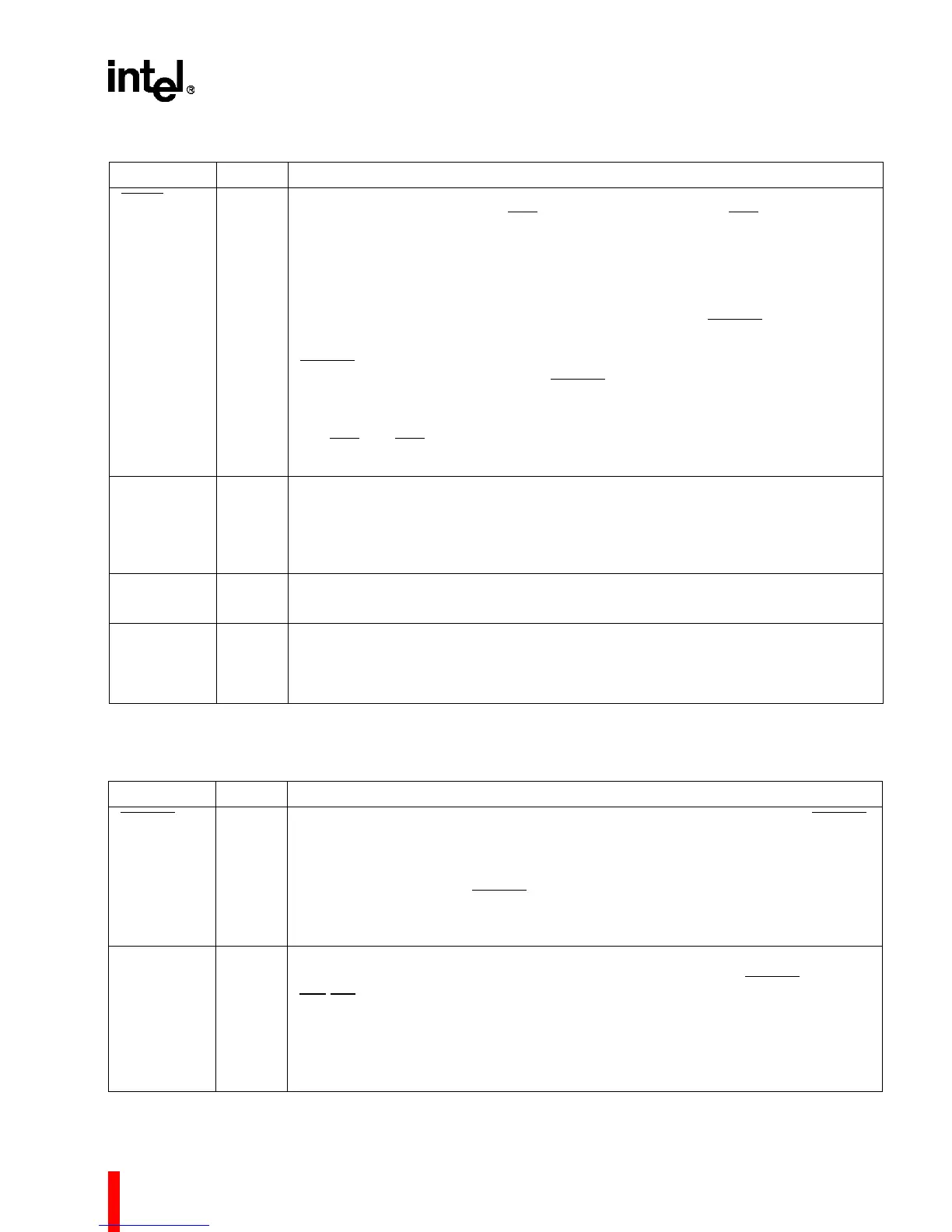

Table 5. 80960KB Pin Description: Support Signals (Sheet 1 of 2)

NAME TYPE DESCRIPTION

BADAC

I BAD ACCESS, if asserted in the cycle following the one in which the last READY

of a transaction is asserted, indicates that an unrecoverable error has occurred

on the current bus transaction or that a synchronous load/store instruction has not

been acknowledged.

During system reset the BADAC

signal is interpreted differently. If the signal is

high, it indicates that this processor will perform system initialization. If it is low,

another processor in the system will perform system initialization instead.

RESET I RESET clears the processor’s internal logic and causes it to reinitialize.

During RESET assertion, the input pins are ignored (except for BADAC

and

IAC

/INT

0

), the three-state output pins are placed in a high impedance state and

other output pins are placed in their non-asserted states.

RESET must be asserted for at least 41 CLK2 cycles for a predictable RESET.

The HIGH to LOW transition of RESET should occur after the rising edge of both

CLK2 and the external bus clock and before the next rising edge of CLK2.

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

Table 4. 80960KB Pin Description: L-Bus Signals (Sheet 2 of 2)

NAME TYPE DESCRIPTION

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

Loading...

Loading...