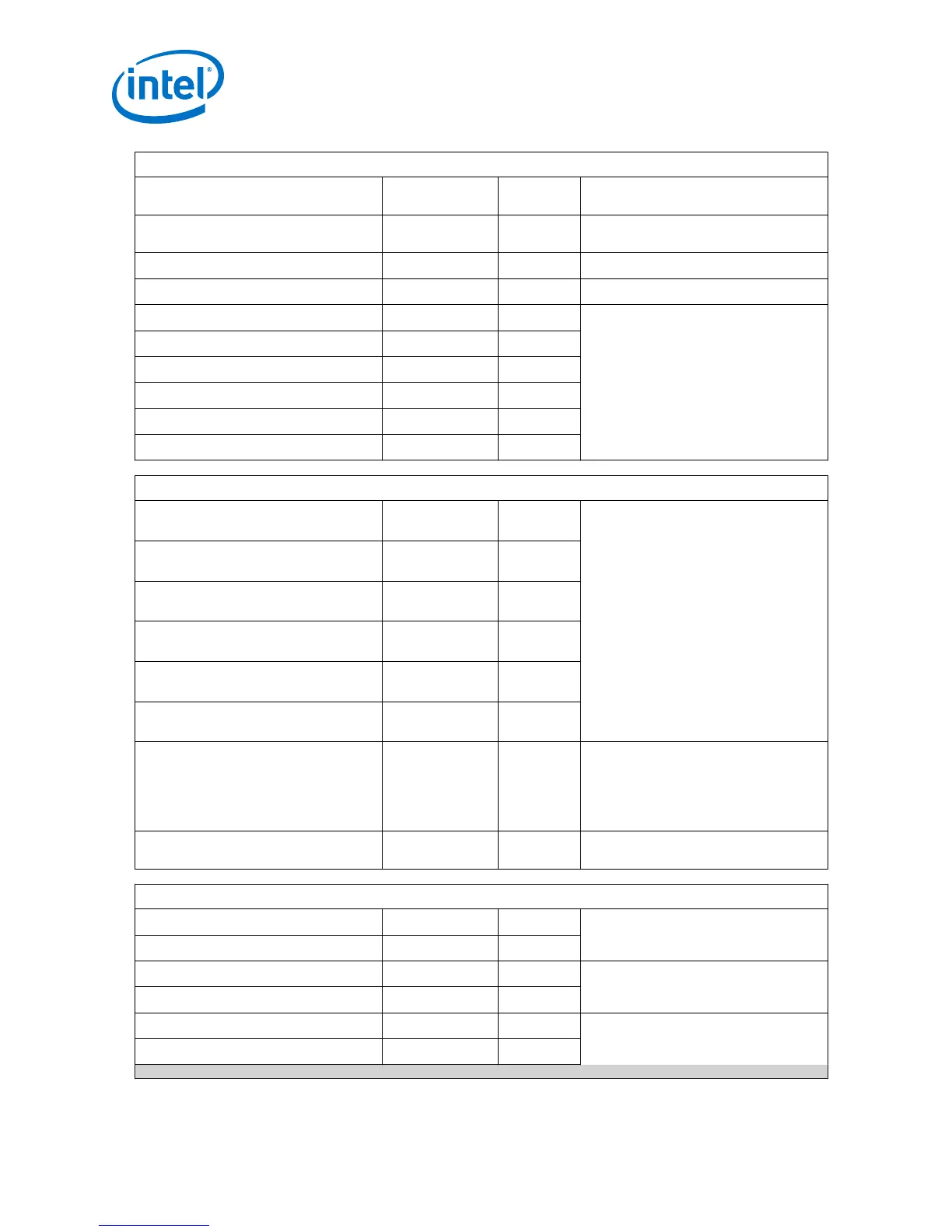

TX Transceiver and IOPLL Signals

gxb_tx_cal_busy_out

Output 4 TX Native PHY calibration busy signal to

the transceiver arbiter

gxb_tx_cal_busy_in

Input 4 Calibration busy signal from the

transceiver arbiter to the TX Native PHY

iopll_locked

Output 1 Indicate IOPLL is locked

txpll_locked

Output 1 Indicate TX PLL is locked

gxb_reconfig_write

Input 4 Transceiver reconfiguration Avalon-MM

interface from the TX Native PHY to the

transceiver arbiter

gxb_reconfig_read

Input 4

gxb_reconfig_address

Input 40

gxb_reconfig_writedata

Input 128

gxb_reconfig_readdata

Output 128

gxb_reconfig_waitrequest

Output 4

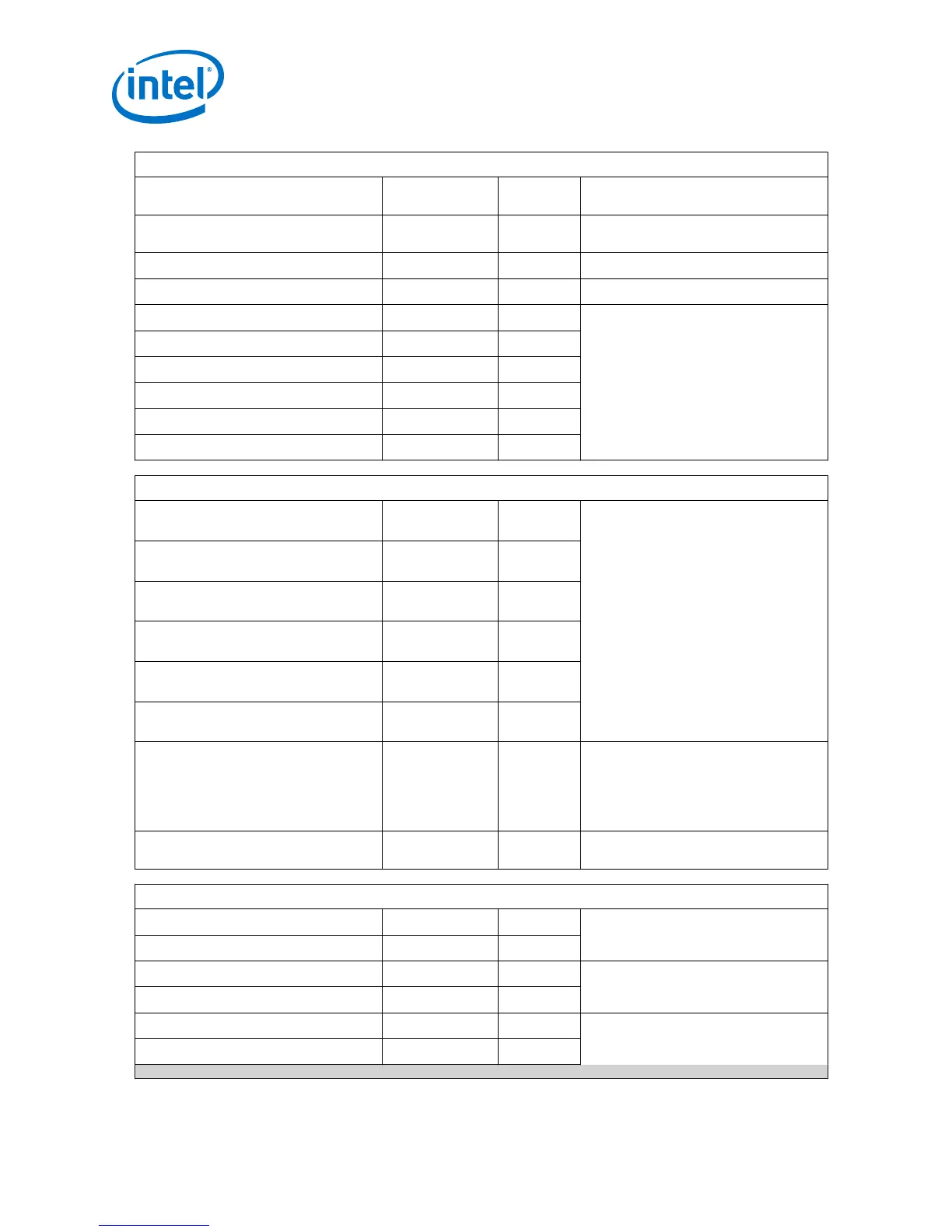

TX IOPLL and TX PLL Reconfiguration Signals

pll_reconfig_write/

tx_pll_reconfig_write

Input 1 TX IOPLL/TX PLL reconfiguration Avalon-

MM interfaces

pll_reconfig_read/

tx_pll_reconfig_read

Input 1

pll_reconfig_address/

tx_pll_reconfig_address

Input 10

pll_reconfig_writedata/

tx_pll_reconfig_writedata

Input 32

pll_reconfig_readdata/

tx_pll_reconfig_readdata

Output 32

pll_reconfig_waitrequest/

tx_pll_reconfig_waitrequest

Output 1

os

Input 2 Oversampling factor:

• 0: No oversampling

• 1: 3× oversampling

• 2: 4× oversampling

• 3: 5× oversampling

measure

Input 24 Indicates the TMDS clock frequency of the

transmitting video resolution.

HDMI TX Core Signals

ctrl

Input 6*N HDMI TX core control interfaces

Note: N = Symbols per clock

mode

Input 1

TMDS_Bit_clock_Ratio

Input 1 SCDC register interfaces

Scrambler_Enable

Input 1

audio_de

Input 1 HDMI TX core audio interfaces

audio_mute

Input 1

continued...

2 Intel FPGA HDMI Design Example Detailed Description

UG-20077 | 2017.11.06

Intel

®

FPGA HDMI Design Example User Guide for Intel

®

Arria 10 Devices

30

Loading...

Loading...