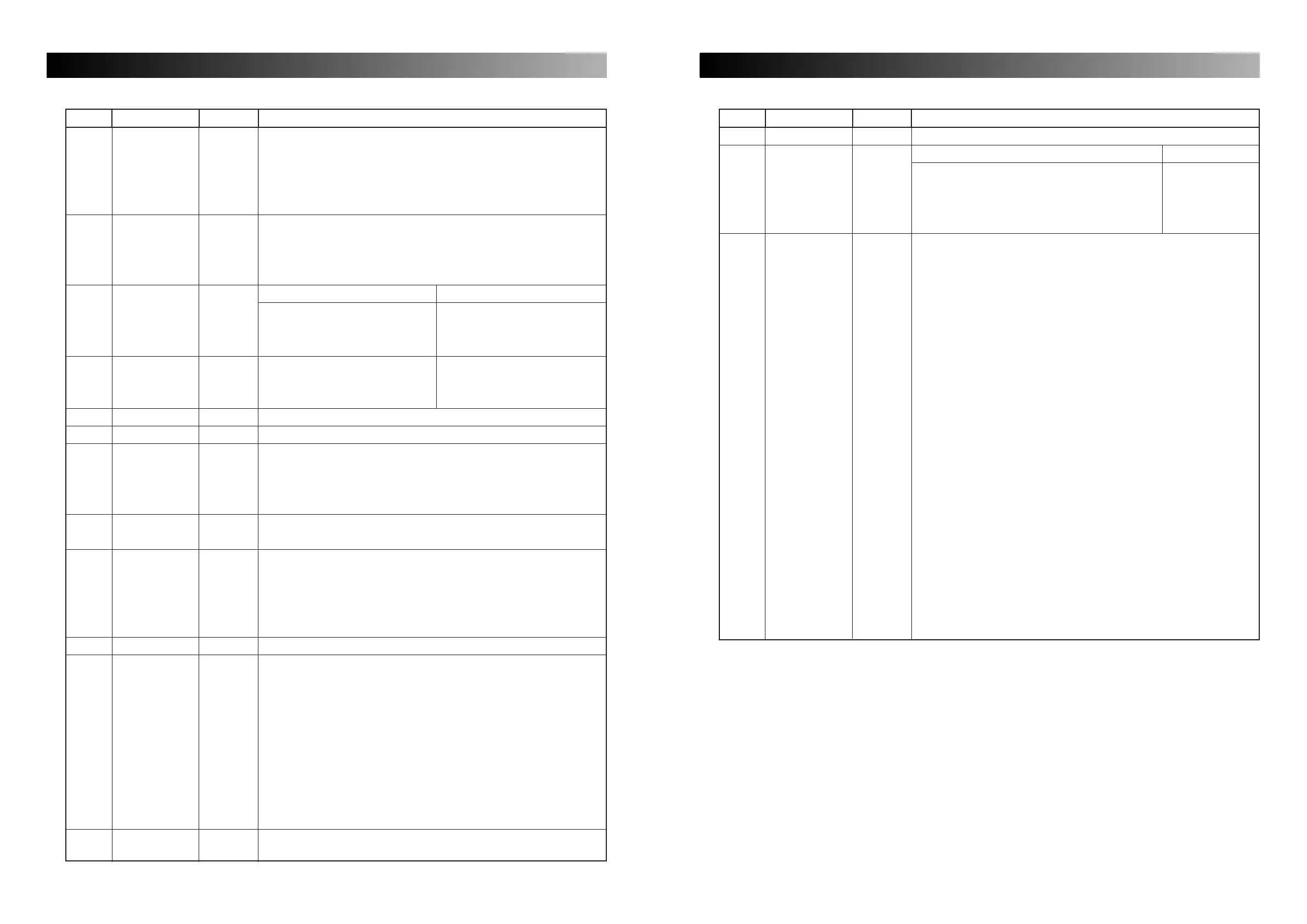

54

No. Name I/O Pin Function Description

1 MD4 I/O External RAM interface data terminal

2 MD3 I/O External RAM interface data terminal

3 MD0 I/O External RAM interface data terminal

4 MD1 I/O External RAM interface data terminal

5 MD2 I/O External RAM interface data terminal

6 MCKO O DOEN=‘L’: Master clock output (12.288MHz)

DOEN=‘H’: Fixed to ‘L’

7XOOX’tal oscillator terminal

8XIIX’tal oscillator terminal or external clock input (12.288MHz)

MODE=‘H’ MODE=‘L’

9 ER0/CSN I+s ER0: E/R preset select 0 CSN: CPU I/F chip select

10 ER1/SCKN I+s ER1: E/R preset select 1 SCKN: CPU I/F serial clock

11 ER2/CDI I+s ER2: E/R preset select 2 CDI: CPU I/F serial data

12 REV0 I+ Reverbration preset select 0

13 REV1 I+ Reverbration preset select 1

14 REV2 I+ Reverbration preset select 2

15 MUTEN I+ Output muting control (low-active)

16 ICN Is Initial clear input

17 PRG I+ DSP program select (available only when MODE=‘H’)

‘L’: Mode 0, ‘H’: Mode 1

18 MODE I+ Operation mode select

‘L’: Register control mode, ‘H’: Preset mode

19 VSS – Ground mode select

20 AVSS –A Ground (analog block)

21 CVA –A L-ch ADC center voltage terminal

22 AORL OA Rear L-ch DAC output

23 AORR OA Rear R-ch DAC output

24 CHL –A AIL input sample/hold capacitor terminal

25 AIL IA L-ch ADC input

26 VDD – +5V power supply (digital block)

27 AIR IA R-ch ADC input

28 CHR –A AIR input sample/hold capacitor terminal

29 AOFL/AOCE OA DOEN=‘H’: Front L-ch DAC output

DOEN=‘L’: C-ch DAC output

30 AOFR/AOCE OA DOEN=‘H’: Front R-ch DAC output

DOEN=‘L’: C-ch DAC output

31 AVDD –A +5V power supply (analog block)

32 CVB –A R-ch, C-ch ADC center voltage terminal

33 AVDD –A +5V power supply (analog block)

34 VDD –A +5V power supply (digital lock)

35 TST0 I+ LSI test terminal (Connect to VDD)

36 TST1 I+ LSI test terminal (Connect to VDD)

NOTE) I+: Input terminal with a pull-up register

IS: Schmitt input

A: Analog terminal

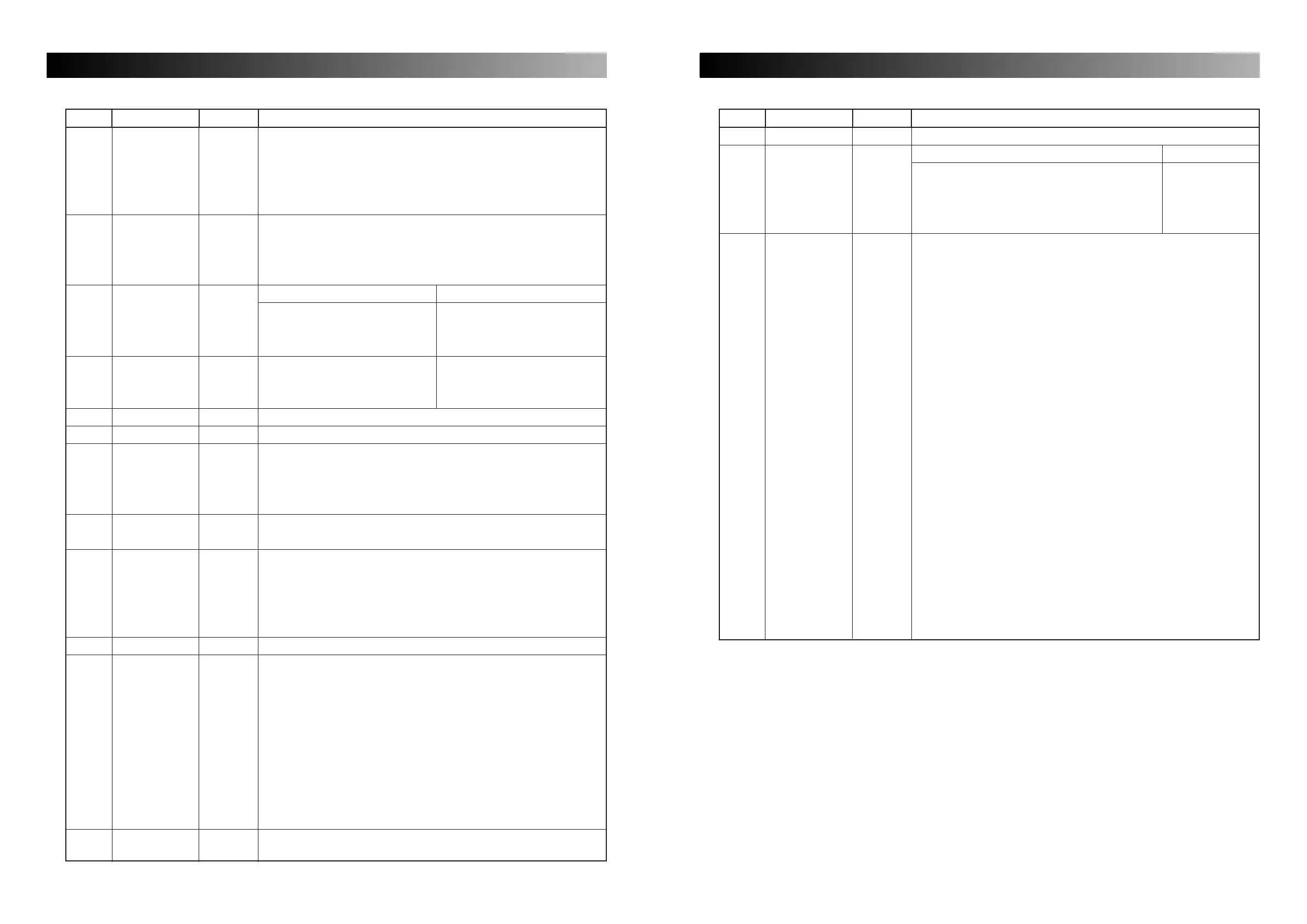

No. Name I/O Pin Function Description

37 DOEN I+ Digital signal output/Analog C-ch output enable

DOEN=‘L’ DOEN=‘H’

38 SDO1 O Digital signal output rear channel (RL, RR) Fixed to ‘L’

39 SDO0 O Digital signal output front channel (FL, FR) Fixed to ‘L’

40 WC O Digital signal output word clock is Fixed to ‘L’

41 BCO O Digital signal output bit clock 64fs Fixed to ‘H’

42 MA0 O External RAM interface address terminal

43 MA1 O External RAM interface address terminal

44 MA2 O External RAM interface address terminal

45 MA3 O External RAM interface address terminal

46 MA4 O External RAM interface address terminal

47 MA5 O External RAM interface address terminal

48 MA6 O External RAM interface address terminal

49 MA7 O External RAM interface address terminal

50 MA12 O External RAM interface address terminal

51 MA14 O External RAM interface address terminal

52 VSS – Ground (digital block)

53 MA10 O External RAM interface address terminal

54 MA11 O External RAM interface address terminal

55 MA9 O External RAM interface address terminal

56 MA8 O External RAM interface address terminal

57 MA13 O External RAM interface address terminal

58 VDD – +5V power supply (digital block)

59 WEN O External RAM interface write enable terminal

60 OEN O External RAM interface output enable terminal

61 CEN O External RAM interface chip enable terminal

62 MD7 I/O External RAM interface data terminal

63 MD6 I/O External RAM interface data terminal

64 MD5 I/O External RAM interface data terminal

Loading...

Loading...