KD-SX980

1-23

Description of major ICs

A0

A1

A2

GND

1

2

3

4

Vcc

WP

SCL

SDA

8

7

6

5

1kbit EEPROM ARRAY

7bit

ADDRESS

DECODER

SLAVE/WORD

ADDRESS REGISTER

7bit

8bit

DATA

REGISTER

CONTROL LOGIC

HIGH VOLTAGE GEN. Vcc LEVEL DETECT

ACK

START

STOP

BR24C01AFV-W-X (IC502) : EEPROM

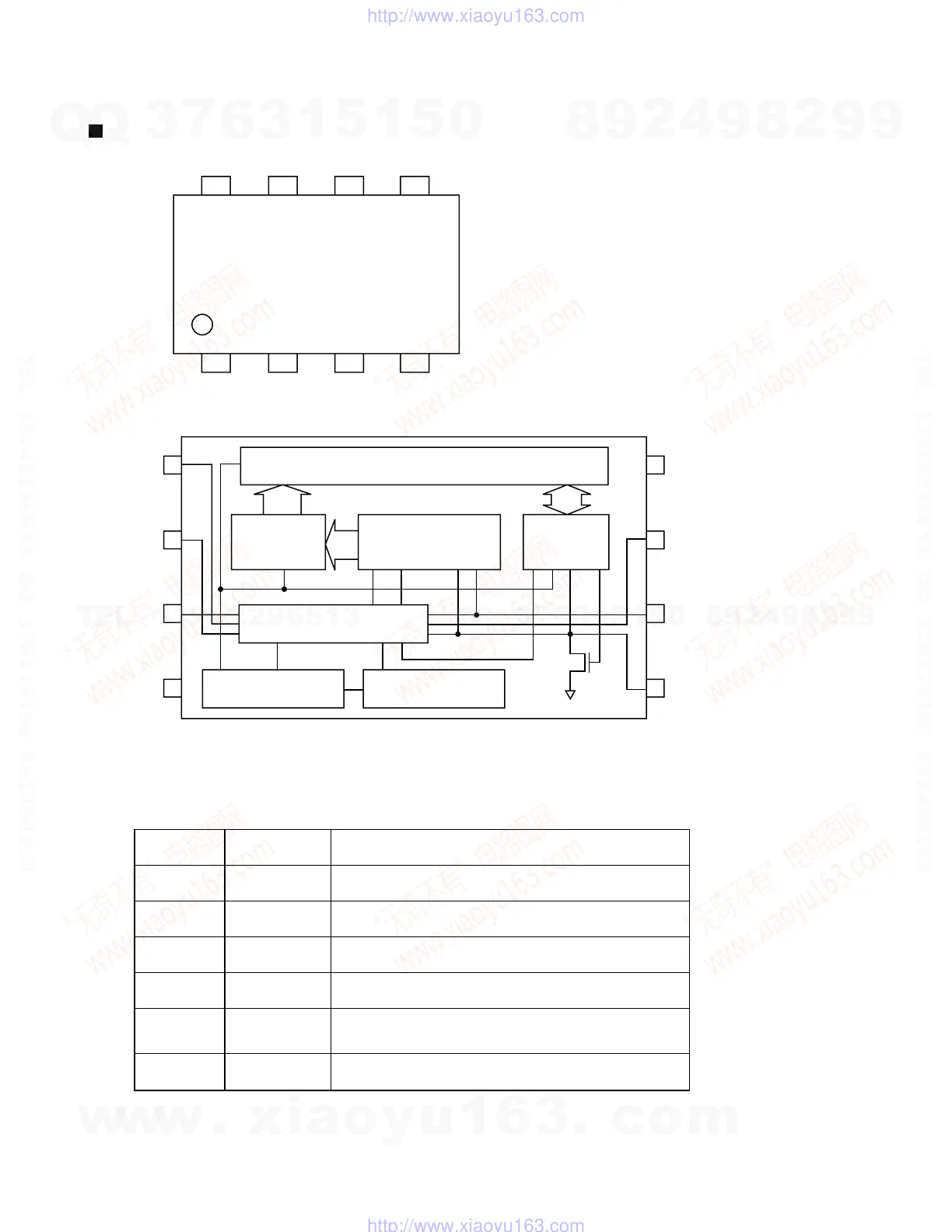

1.Pin layout

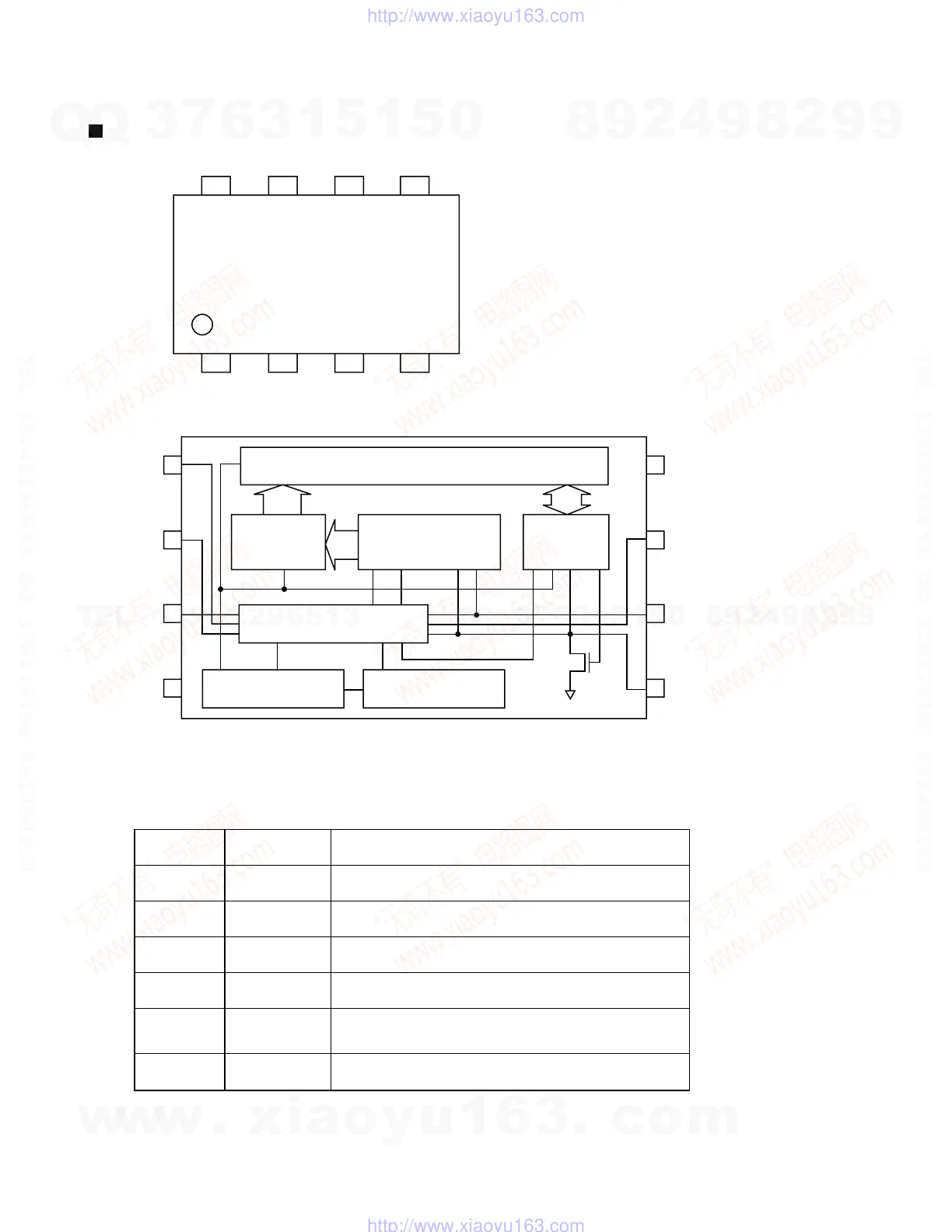

2.Block diagram

3.Pin function

A0 A1 A2 GND

Vcc WP SCL SDA

Pin name I/O

Function

Vcc

GND

A0,A1,A2

SCL

SDA

WP

-

-

IN

IN

IN / OUT

IN

*1 An open drain output requires a pull-up resister.

Power supply

Ground (0v)

Slave address set

Serial clock input

Slave and word address,

serial data input, serial data output *1

Write protect input

w

w

w

.

x

i

a

o

y

u

1

6

3

.

c

o

m

Q

Q

3

7

6

3

1

5

1

5

0

9

9

2

8

9

4

2

9

8

T

E

L

1

3

9

4

2

2

9

6

5

1

3

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299

http://www.xiaoyu163.com

http://www.xiaoyu163.com

Loading...

Loading...