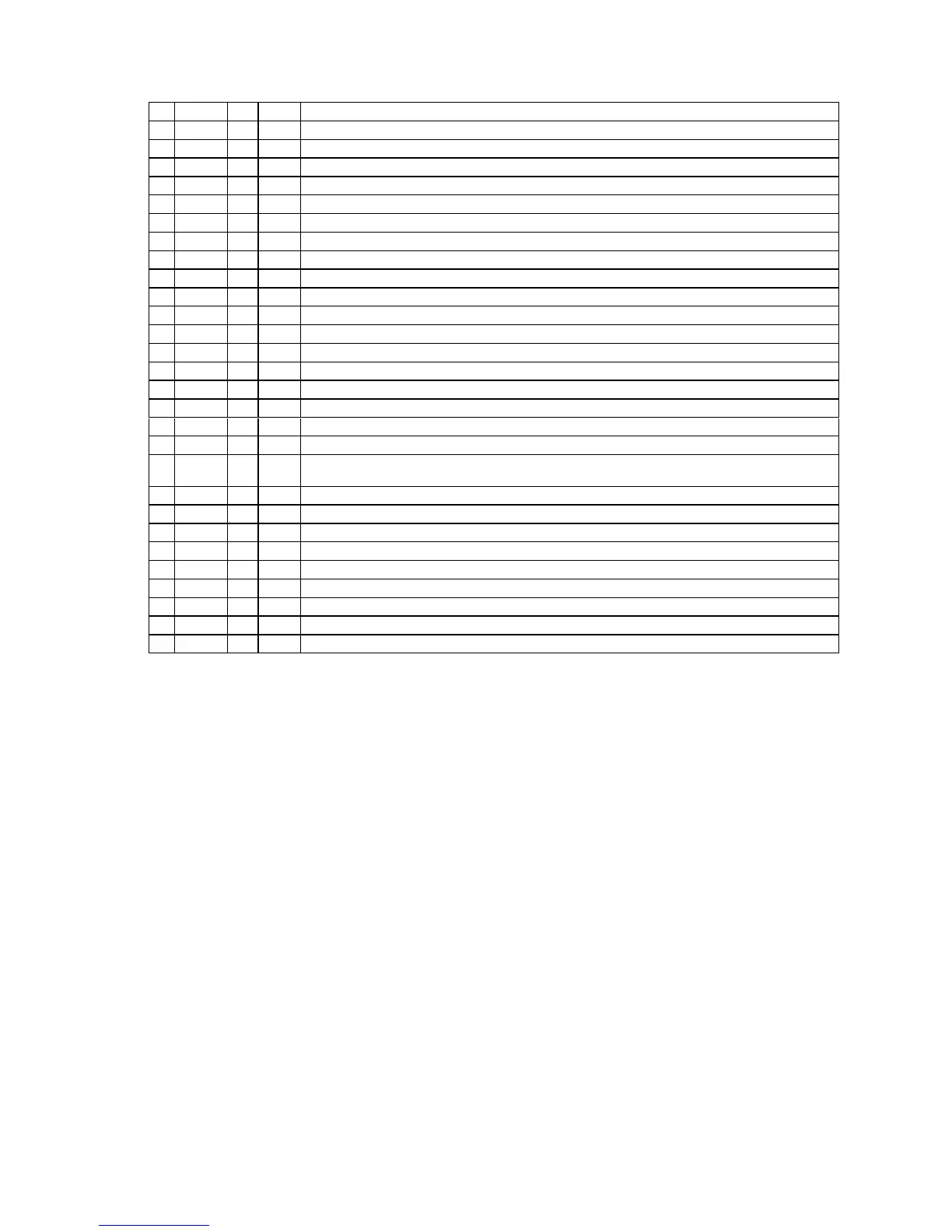

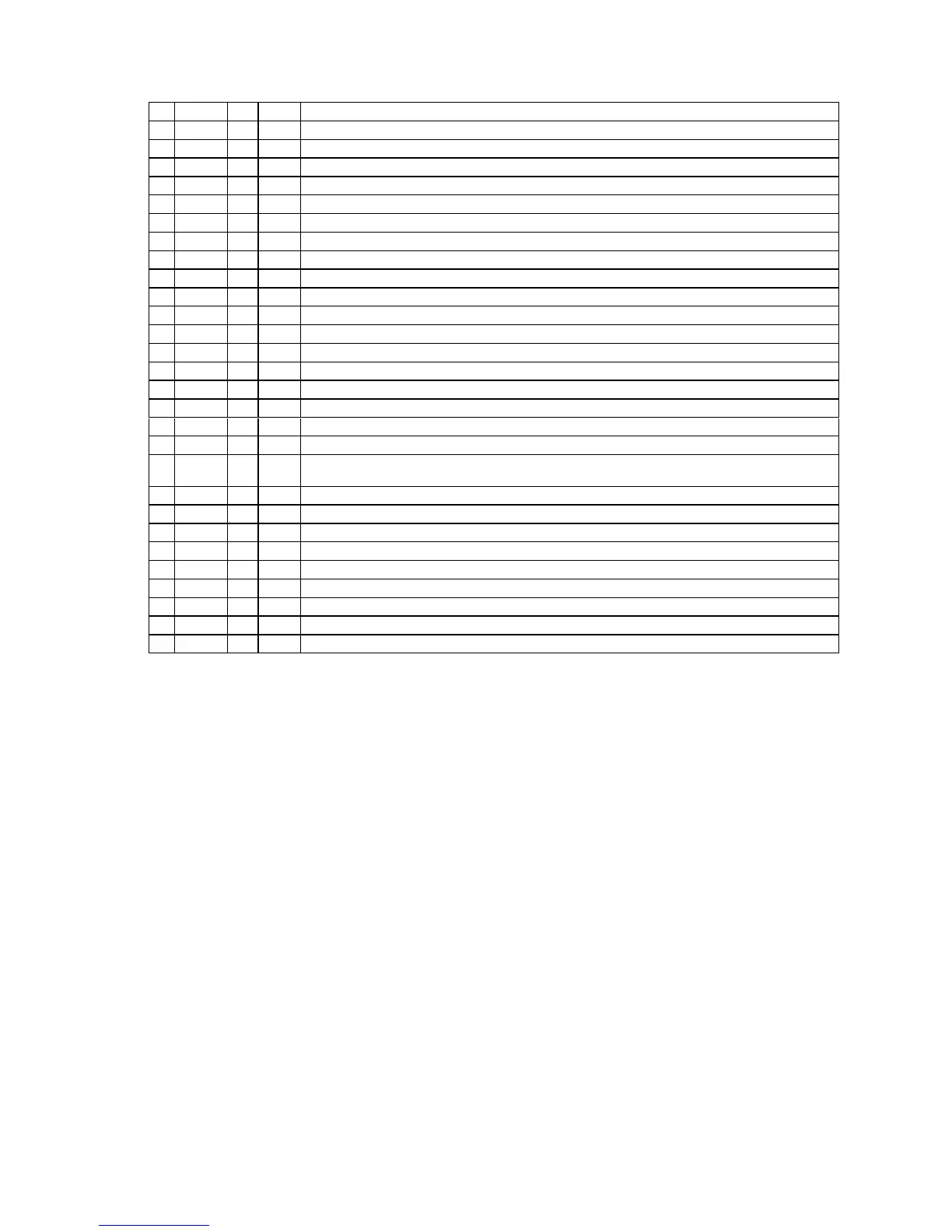

35

IC203 : CXD3068Q

53 FILO O Analog Master PLL filter output (slave = digital PLL).

54 FILI I Master PLL filter input.

55 PCO O 1, Z, 0 Master PLL charge pump output.

56 AVDD1 — — Analog power supply.

57 BIAS I Asymmetry circuit constant current input.

58 VCTL I Wide-band EFM PLL VCO2 control voltage input.

Wide-band EFM PLL VCO2 oscillation output. Serves as wide-band EFM

59 V16M I/O 1, 0 PLL clock input by switching with the command.

60 VPCO O 1, Z, 0 Wide-band EFM PLL charge pump output.

61 DVDD2 — — Digital power supply.

62 ASYE I Asymmetry circuit on/off (low = off, high = on).

63 MD2 I Digital Out on/off control (low = off, high = on).

64 DOUT O 1, 0 Digital Out output.

65 LRCK O 1, 0 D/A interface. LR clock output. f = Fs

66 PCMD O 1, 0 D/A interface. Serial data output (two's complement, MSB first).

67 BCK O 1, 0 D/A interface. Bit clock output. Outputs a high signal when the playback disc has emphasis, and a low

68 EMPH O 1, 0 Outputs a high signal when the playback disc has emphasis, and a low signal when there is no emphasis.

69 XTSL I Crystal selection input. Low when the crystal is 16.9344MHz; high when it is 33.8688MHz.

70 DVSS2 — — Digital GND.

71 XTAI I Crystal oscillation circuit input. When the master clock is input externally,

input it from this pin.

72 XTAO O Crystal oscillation circuit output.

73 SOUT O 1, 0 Serial data output in servo block.

74 SOCK O 1, 0 Serial data readout clock output in servo block.

75 XOLT O 1, 0 Serial data latch output in servo block.

76 SQSO O 1, 0 Sub-Q 80-bit, PCM peak or level data outputs. CD TEXT data output.

77 SQCK I SQSO readout clock input.

78 SCSY I GRSCOR resynchronization input.

79 SBSO O 1, 0 Sub-Q P to W serial output.

80 EXCK I SBSO readout clock input.

Notes)

PCMD is a MSB first, two’s complement output.

XUGF is the frame sync obtained from the EFM signal, and is negative pulse. It is the signal before sync protection.

XPCK is the inverse of the EFM PLL clock. The PLL is designed so that the falling edge and the EFM signal transition

point coincide.

The GFS signal goes high when the frame sync and the insertion protection timing match.

C2PO represents the data error status.

Loading...

Loading...