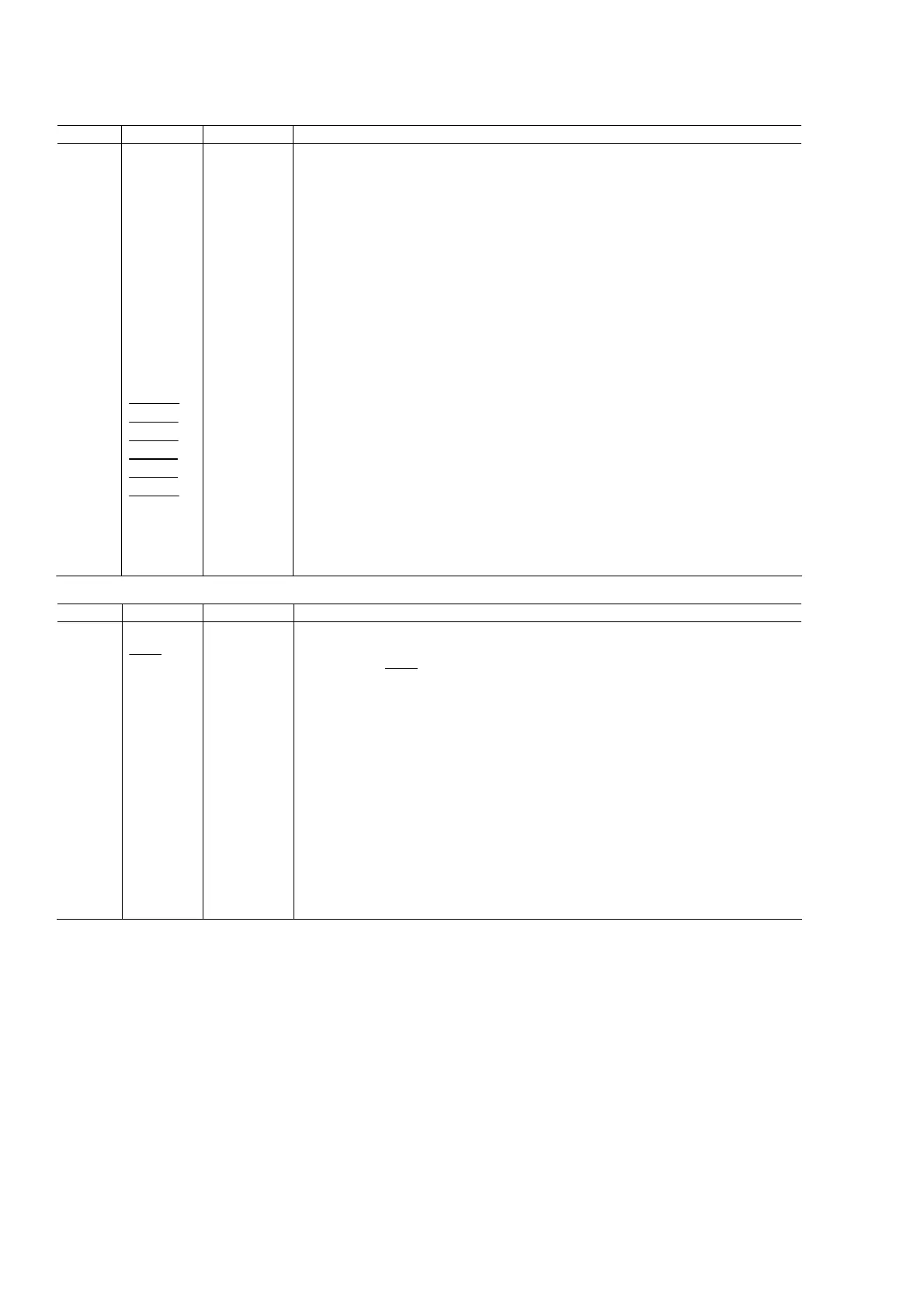

[PM01] QN01 : ADV7320

Pin No. Mnemonic Input/Output Description

62–58,

55–51

S9 to S0 I

SD or Progressive Scan/HDTV Input Port for Cr[Red/V] Data in 4:4:4 Input Mode. LSB is set up

on Pin S0. For 8-bit data input, LSB is set up on S2.

33

RESET

I

This input resets the on-chip timing generator and sets the ADV7320/ADV7321 into default

register setting. RESET

is an active low signal.

47, 35 R

SET1

, R

SET2

I

A 3040 Ω resistor must be connected from this pin to AGND and is used to control the

amplitudes of the DAC outputs.

22 SCLK I I

2

C Port Serial Interface Clock Input.

21 SDA I/O I

2

C Port Serial Data Input/Output.

20 ALSB I

TTL Address Input. This signal sets up the LSB of the I

2

C address. When this pin is tied low, the

I

2

C filter is activated, which reduces noise on the I

2

C interface.

1 V

DD_IO

P Power Supply for Digital Inputs and Outputs.

10, 56 V

DD

P Digital Power Supply.

41 V

AA

P Analog Power Supply.

46 V

REF

I/O Optional External Voltage Reference Input for DACs or Voltage Reference Output (1.235 V).

34 EXT_LF I External Loop Filter for the Internal PLL.

31 RTC_SCR_TR I Multifunctional Input. Real-time control (RTC) input, timing reset input, subcarrier reset input.

19 I

2

C I This input pin must be tied high (V

DD_IO

) for the ADV7320/ADV7321 to interface over the I

2

C port.

64 GND_IO Digital Input/Output Ground.

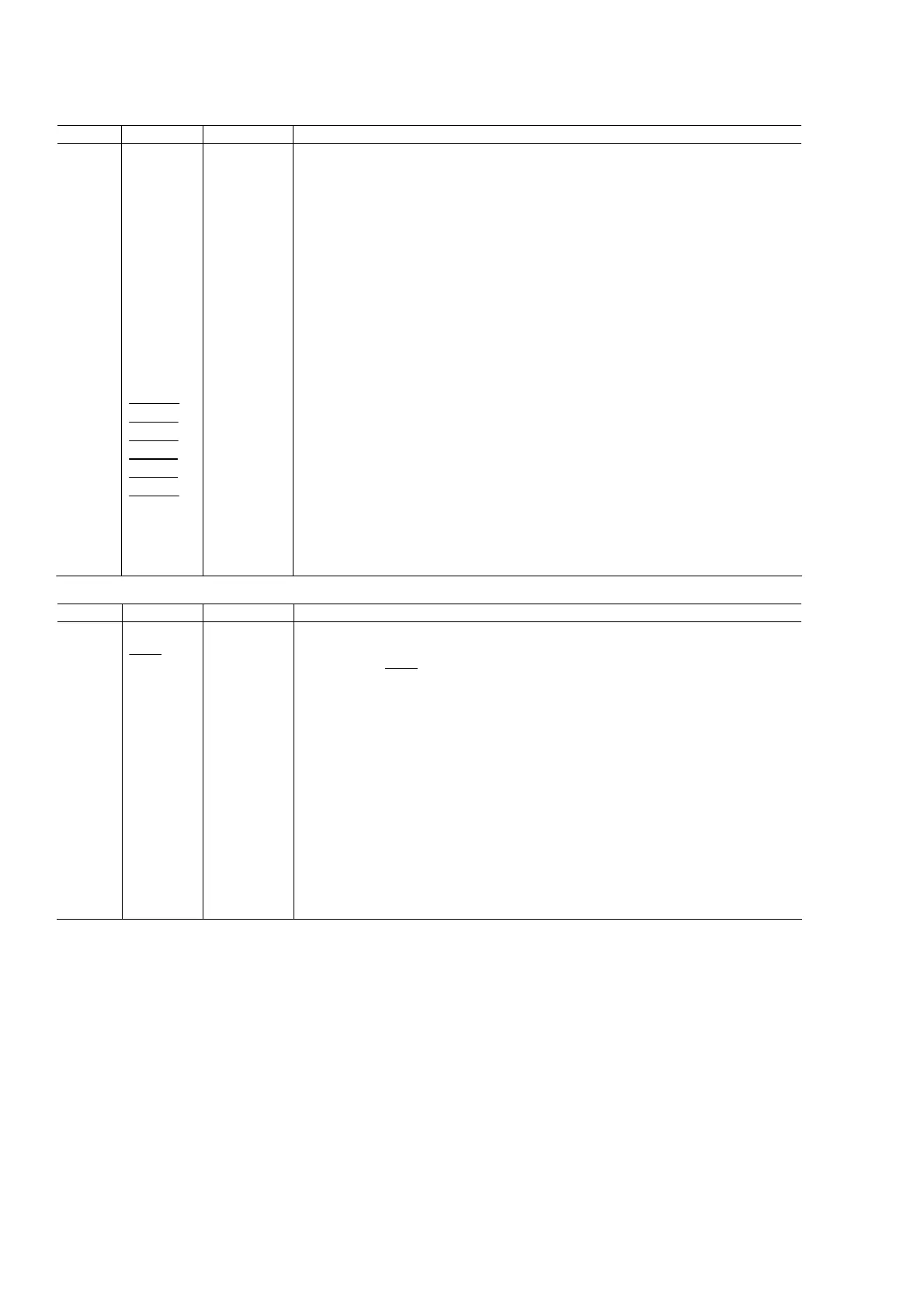

Pin No. Mnemonic Input/Output Description

11, 57 DGND G Digital Ground.

40 AGND G Analog Ground.

32 CLKIN_A I Pixel Clock Input for HD (74.25 MHz Only, PS Only (27 MHz), SD Only (27 MHz).

63 CLKIN_B I

Pixel Clock Input. Requires a 27 MHz reference clock for progressive scan mode or a 74.25 MHz

(74.1758 MHz) reference clock in HDTV mode. This clock is only used in dual modes.

45, 36

COMP1,

COMP2

O Compensation Pin for DACs. Connect 0.1 μF capacitor from COMP pin to V

AA

.

44 DAC A O CVBS/Green/Y/Y Analog Output.

43 DAC B O Chroma/Blue/U/Pb Analog Output.

42 DAC C O Luma/Red/V/Pr Analog Output.

39 DAC D O

In SD Only Mode: CVBS/Green/Y Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Y/Green [HD] Analog Output.

38 DAC E O

In SD Only Mode: Luma/Blue/U Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Pr/Red Analog Output.

37 DAC F O

In SD Only Mode: Chroma/Red/V Analog Output; in HD Only Mode and Simultaneous HD/SD

Mode: Pb/Blue [HD] Analog Output.

23

P_HSYNC

I Video Horizontal Sync Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

24

P_VSYNC

I Video Vertical Sync Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

25

P_BLANK

I Video Blanking Control Signal for HD in Simultaneous SD/HD Mode and HD Only Mode.

48

S_BLANK

I/O Video Blanking Control Signal for SD Only.

49

S_VSYNC

I/O Video Vertical Sync Control Signal for SD Only.

50

S_HSYNC

I/O Video Horizontal Sync Control Signal for SD Only.

13,12,

9–2

Y9 to Y0 I

SD or Progressive Scan/HDTV Input Port for Y Data. Input port for interleaved progressive scan

data. The LSB is set up on Pin Y0. For 8-bit data input, LSB is set up on Y2.

30–26,

18–14

C9 to C0 I

Progressive Scan/HDTV Input Port 4:4:4 Input Mode. This port is used for the Cb[Blue/U] data.

The LSB is set up on Pin C0. For 8-bit data input, LSB is set up on C2.

182

Loading...

Loading...