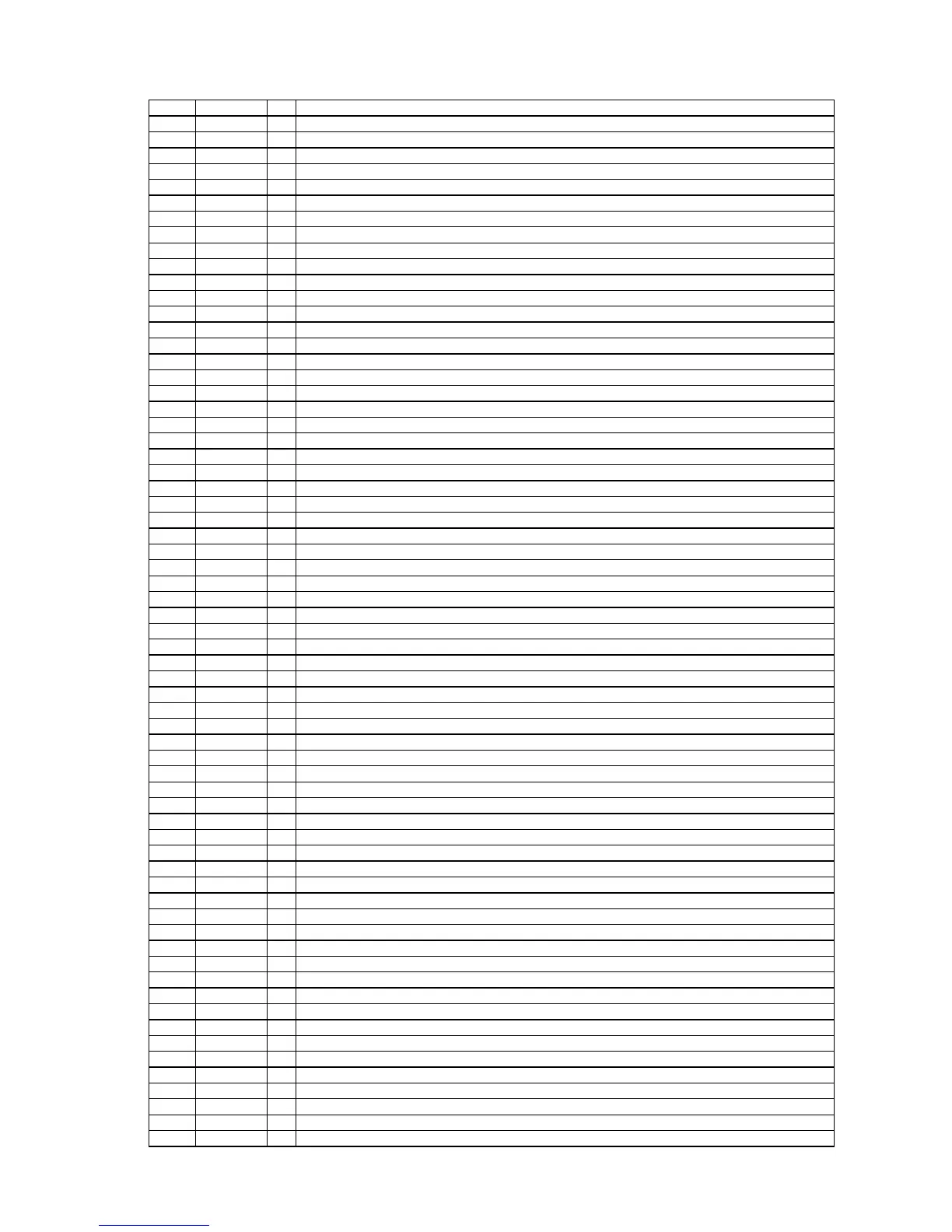

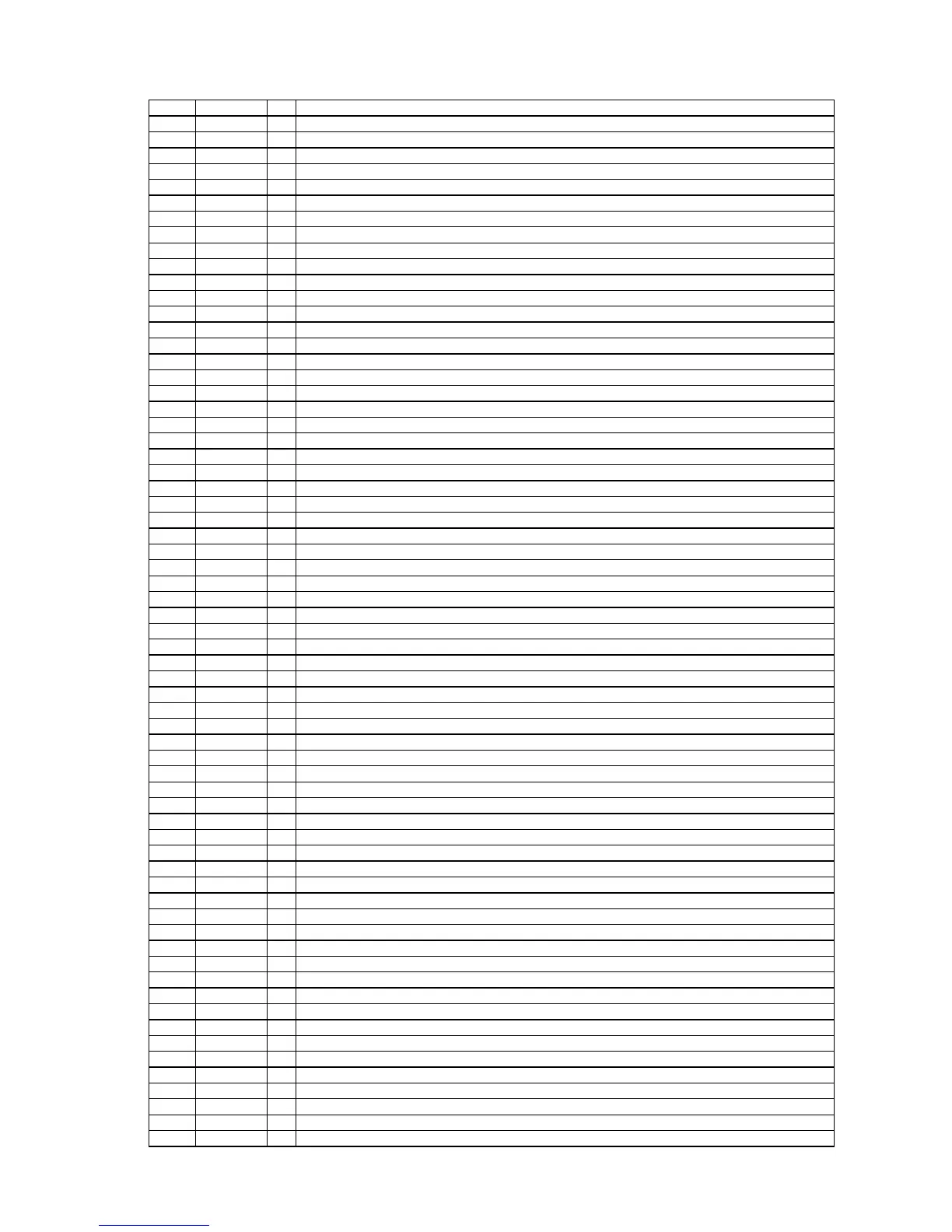

39

Q125 : GXPQ7100(MASK)

Pin No. Pin Name I/O Description

1 FTMUT O Actuator driver mute signal for foc/track

2 SLMUT O Actuator driver mute signal for spin/sledg

3 AMUT O Muting on/off "L" : muting on for CXD3068Q

4 SMUT O Muting on/off signal output to the DSD decoder "H" : muting on

5 XRST O System reset signal output (L= reset)

6 CD/XDVD O CD/DVD(SACD) mode selection signal output (L=CD, H=SACD)

7 LOCK I GFS is sampled by 460 Hz "H" input when GFS is. "H"

8 MBHLD - NC

9 AMPSDT I/O Serial data transfer DATA signal input,output

10 AMPSCK O Serial data transfer clock signal output

11 AMPSEN O Serial data transfer enable signal (H=enable)

12 XDECSEL O OPU block on/off for modulation circuit (L=on)

13 VSS O Ground terminal (digital system)

14 D0 I/O Two-way data bus

15 D1 I/O Two-way data bus

16 D2 I/O Two-way data bus

17 D3 I/O Two-way data bus

18 D4 I/O Two-way data bus

19 D5 I/O Two-way data bus

20 D6 I/O Two-way data bus

21 D7 I/O Two-way data bus

22 XDECINT0 I Interrupt signal input from CXD1881R

23 XDECINT1 I Interrupt signal input from CXD1881R

24 TZC I Track signal, OPU in case by traversal the disc track line

25 PE3 - NC

26 PE3 - NC

27 SEEK O Display data ready signal output to the feature MPU ("H" : read)

28 REQST O Reqest signal CXD1882R

29 NC - Not used (open)

30 DECMNT1 I RF signal monitor input from CXD1882R

31 FOK I Focus on signal

32 GFSDEC I Guard frame sync signal input

33 DRVRXD I Input signal data from the feature MPU

34 DRVTXD O Output signal data for the featur MPU

35 DRVCLK I Input signal clock from the featur MPU

36 XDRVRDY O Output data signal readey for the featur MPU

37 DRVIRQ O Iutput data signal readey from the featur MPU

38 XRESET I Power on reset signal input (L=reset)

39 VSS Ground terminal (digital system)

40 XTAL I System clock input terminal (20 MHz)

41 EXTAL O System clock output terminal (20 MHz)

42 VDD Power supply terminal (+3.3V) (digital system)

43 DSPXLAT O Serial data latch pulse signal output to the CXD3068Q

44 XMSLAT O Serial data latch pulse signal output to the CXD2752R

45 MSCK O Serial data transfer clock signal output to CXD2752R

46 MSDTO O Serial data output to the DSD CXD2752R

47 MSDTI I Serial data input from the CXD2752R

48 MSREADY I Ready signal input from the CXD2752R "L" : ready

49 DSPDTO O Serial data output to the CXD3068Q

50 DSPSCK O Serial data clock input from the CXD3068Q

51 SENS I Internal status (SENSE) signal input from CXD3068Q

52 SQSO I Subcode Q data input

53 SNSCK O Serial status data clock output to the CXD3068Q

54 SQCK O Subcode Q data reading clock signal output

55 VSS Ground terminal (digital system)

56 JITIN I Jitter signal input terminal

57 AMPMNT I Monitor signal from the CXD1881R

58 -ATT I -12dB atteneation request signal input "L" : attenation on

59 P17 - NC

60 PJ0 - NC

61 SCSY O GRSCOR data sync request signal for CXD3068Q

62 GFSDSP I Frequency generator signal input

63 C2PO I C2 pointer signal input from the CXD3068Q

64 MIRR I Mirror signal input from CXD3068Q

65 DECMNT2 I Monitor signal from the CXD1882R

Loading...

Loading...