2018 Microchip Technology Inc. DS70005340A-page 33

CAN FD Protocol Module

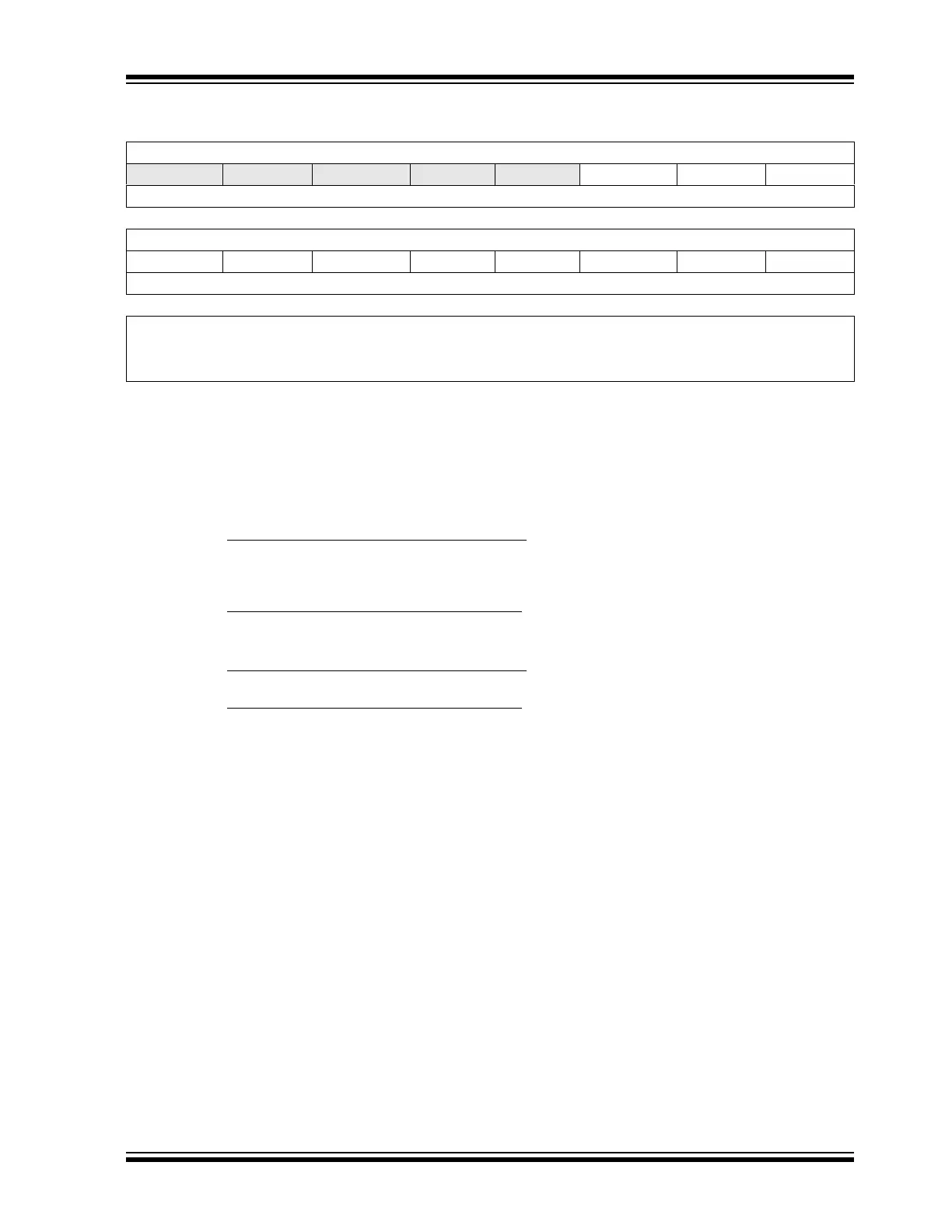

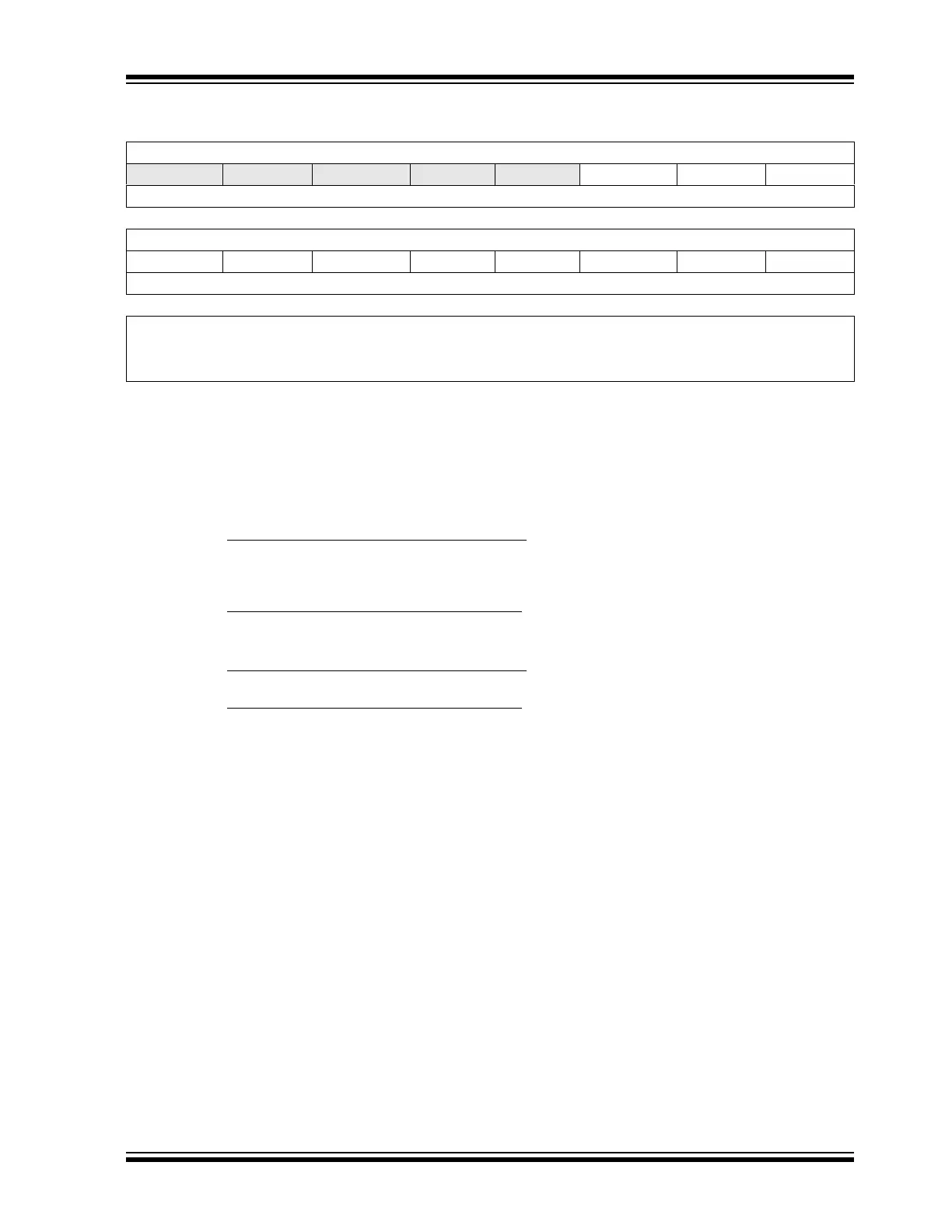

Register 3-33: C1FIFOCONxL: CAN FIFO Control Register x (x = 1 to 31) Low

U-0 U-0 U-0 U-0 U-0 S/HC-1 R/W/HC-0 S/HC-0

— — — — — FRESET TXREQ UINC

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

TXEN RTREN RXTSEN

(1)

TXATIE RXOVIE TFERFFIE TFHRFHIE TFNRFNIE

bit 7 bit 0

Legend: S = Settable bit HC = Hardware Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as ‘0’

bit 10 FRESET: FIFO Reset bit

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; user should poll

whether this bit is clear before taking any action

0 = No effect

bit 9 TXREQ: Message Send Request bit

TXEN =

1 (FIFO configured as a transmit FIFO):

1 = Requests sending a message; the bit will automatically clear when all the messages queued in

the FIFO are successfully sent

0 = Clearing the bit to ‘0’ while set (‘1’) will request a message abort

TXEN = 0 (FIFO configured as a receive FIFO):

This bit has no effect.

bit 8 UINC: Increment Head/Tail bit

TXEN = 1 (FIFO configured as a transmit FIFO):

When this bit is set, the FIFO head will increment by a single message.

TXEN = 0 (FIFO configured as a receive FIFO):

When this bit is set, the FIFO tail will increment by a single message.

bit 7 TXEN: TX/RX Buffer Selection bit

1 = Transmits message object

0 = Receives message object

bit 6 RTREN: Auto-Remote Transmit (RTR) Enable bit

1 = When a Remote Transmit is received, TXREQ will be set

0 = When a Remote Transmit is received, TXREQ will be unaffected

bit 5 RXTSEN: Received Message Timestamp Enable bit

(1)

1 = Captures timestamp in received message object in RAM

0 = Does not capture time stamp

bit 4 TXATIE: Transmit Attempts Exhausted Interrupt Enable bit

1 = Enables interrupt

0 = Disables interrupt

bit 3 RXOVIE: Overflow Interrupt Enable bit

1 = Interrupt is enabled for overflow event

0 = Interrupt is disabled for overflow event

Note 1: These bits can only be modified in Configuration mode (OPMOD<2:0> = 100).

Loading...

Loading...