2018 Microchip Technology Inc. DS70005340A-page 57

CAN FD Protocol Module

5.0 CONFIGURATION

5.1 Clock Configuration

The sample point of all nodes in a CAN FD network should be at the same position. Hence, it is

recommended to use the same clock frequency and bit time settings for all nodes. Therefore, a

SYSCLK of 80 MHz, 40 MHz, 20 MHz or 10 MHz is recommended

The CLKSEL bit allows the selection of the clock source to the CAN FD module.

• If CLKSEL = 1, then the auxiliary clock will be selected as a clock source

• If CLKSEL = 0, then the clock from the CAN clock generator will be selected

The following register is used to configure the CAN clock generator.

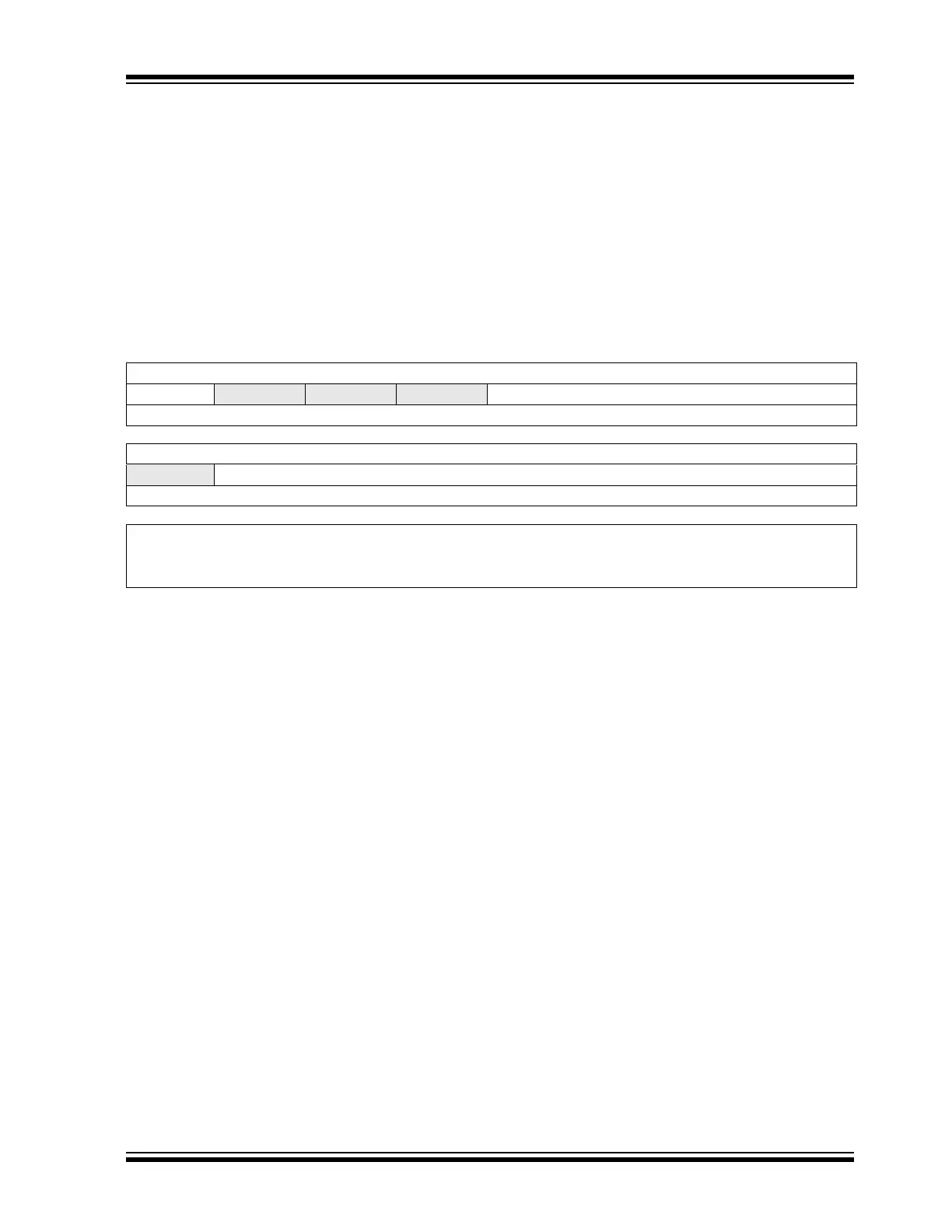

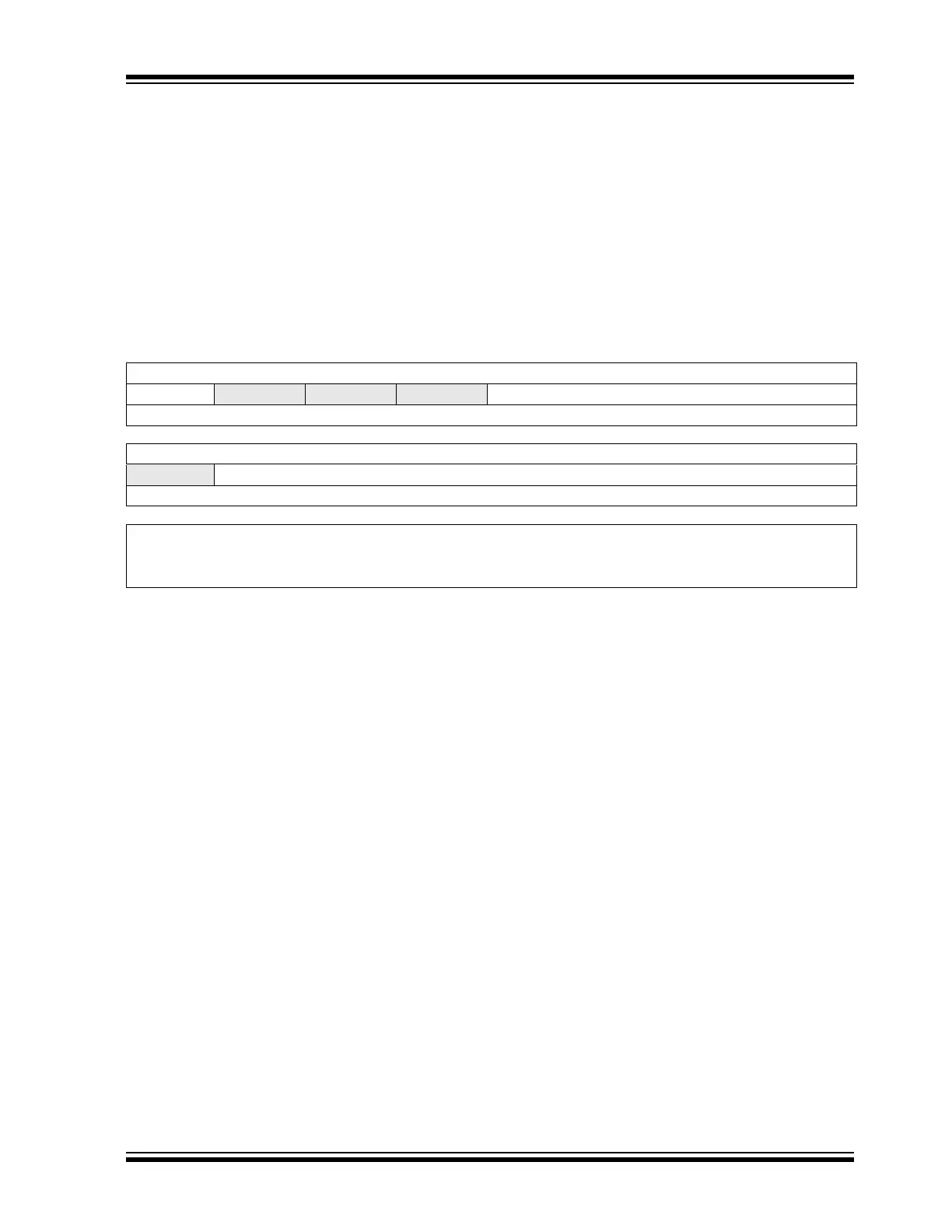

Register 5-1: CANCLKCON: CAN Clock Control Register

(1)

R/W-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0

CANCLKEN

— — — CANCLKSEL<3:0>

(1)

bit 15 bit 8

U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— CANCLKDIV<6:0>

(2,3)

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15 CANCLKEN: CAN Clock Generator Enable bit

1 = CAN clock generation circuitry is enabled

0 = CAN clock generation circuitry is disabled

bit 14-12 Unimplemented: Read as ‘0’

bit 11-8 CANCLKSEL<3:0>: Can Clock Source Select bits

(1)

1011-1111 = Reserved (no clock selected)

1010 = AF

VCO

/4 clock

1001 = AF

VCO

/3 clock

1000 = AF

VCO

/2 clock

0111 = AF

PLLVCO

clock

0110 = Auxiliary clock

0101 = VCO/4 clock

0100 = VCO/3 clock

0011 = VCO/2 clock

0010 = PLLDIV clock

0001 = VCO clock

0000 = 0 (No clock selected)

bit 7 Unimplemented: Read as ‘0’

bit 6-0 CANCLKDIV<6:0>: CAN Clock Divider Select bits

(2,3)

1111111 = Divide by 128

•••

0000010 = Divide by 3

0000001 = Divide by 2

0000000 = Divide by 1

Note 1: The user must ensure the input clock source is 640 MHz or less. Operation with input reference frequency

above 640 MHz will result in unpredictable behavior.

2: The CANCLKDIVx divider value must not be changed during CAN module operation.

3: The user must ensure the maximum clock output frequency of the divider is 80 MHz or less.

Loading...

Loading...