dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 48 2018 Microchip Technology Inc.

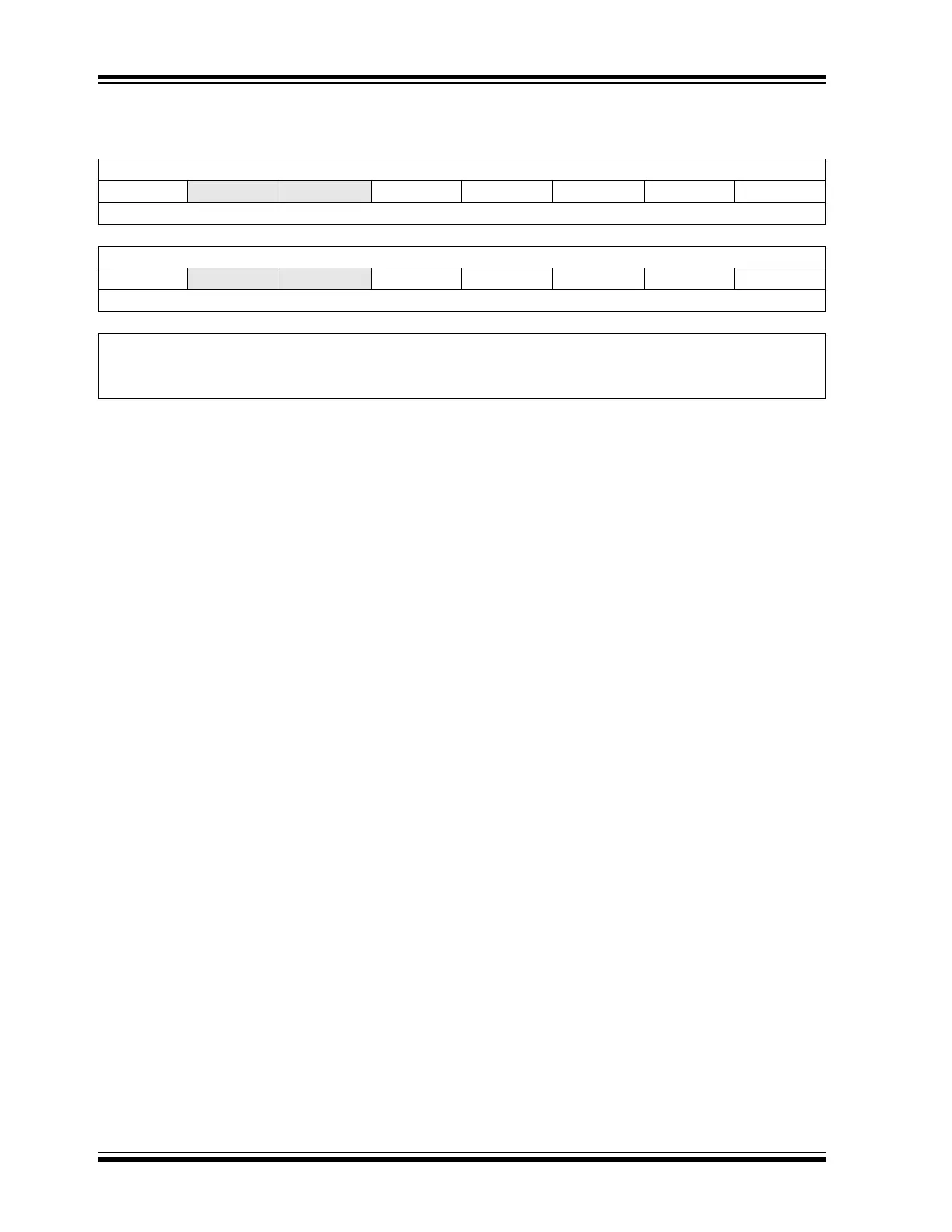

Register 3-51: C1FLTCONxL: CAN Filter Control Register x Low (x = 0 to 7; a = 0, 4, 8, 12, 16, 20, 24, 28;

b = 1, 5, 9, 13, 17, 21, 25, 29)

R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

FLTENb

— — FbBP4 FbBP3 FbBP2 FbBP1 FbBP0

bit 15 bit 8

R/W-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

FLTENa

— — FaBP4 FaBP3 FaBP2 FaBP1 FaBP0

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

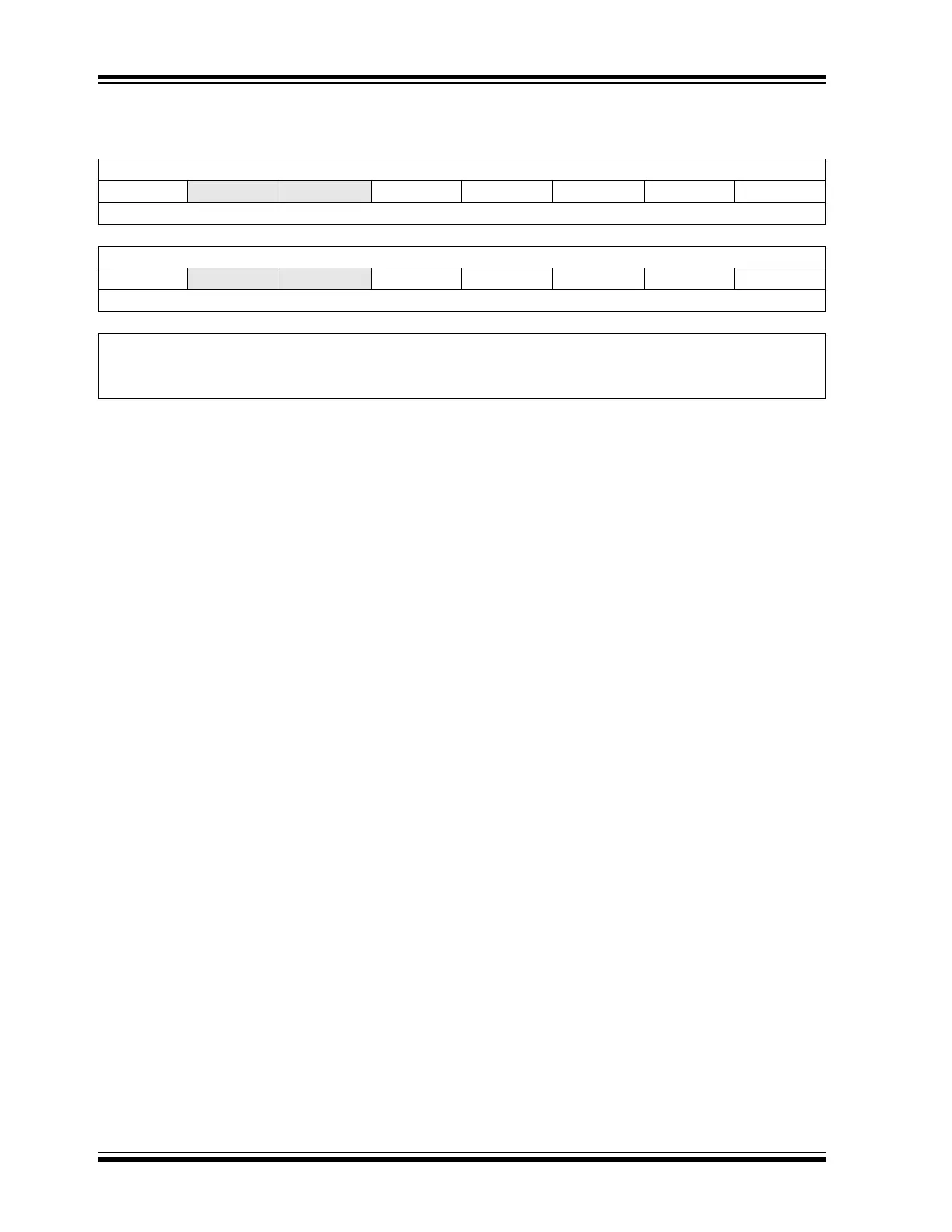

bit 15 FLTENb: Enable Filter b to Accept Messages bit

1 = Filter is enabled

0 = Filter is disabled

bit 14-13 Unimplemented: Read as ‘0’

bit 12-8 FbBP<4:0>: Pointer to Object When Filter b Hits bits

11111 = Message matching filter is stored in Object 31

11110 = Message matching filter is stored in Object 30

...

00010 = Message matching filter is stored in Object 2

00001 = Message matching filter is stored in Object 1

00000 = Reserved; Object 0 is the TX Queue and cannot receive messages

bit 7 FLTENa: Enable Filter a to Accept Messages bit

1 = Filter is enabled

0 = Filter is disabled

bit 6-5 Unimplemented: Read as ‘0’

bit 4-0 FaBP<4:0>: Pointer to Object When Filter a Hits bits

11111 = Message matching filter is stored in Object 31

11110 = Message matching filter is stored in Object 30

...

00010 = Message matching filter is stored in Object 2

00001 = Message matching filter is stored in Object 1

00000 = Reserved; Object 0 is the TX Queue and cannot receive messages

Loading...

Loading...