dsPIC33/PIC24 Family Reference Manual

DS70005340A-page 50 2018 Microchip Technology Inc.

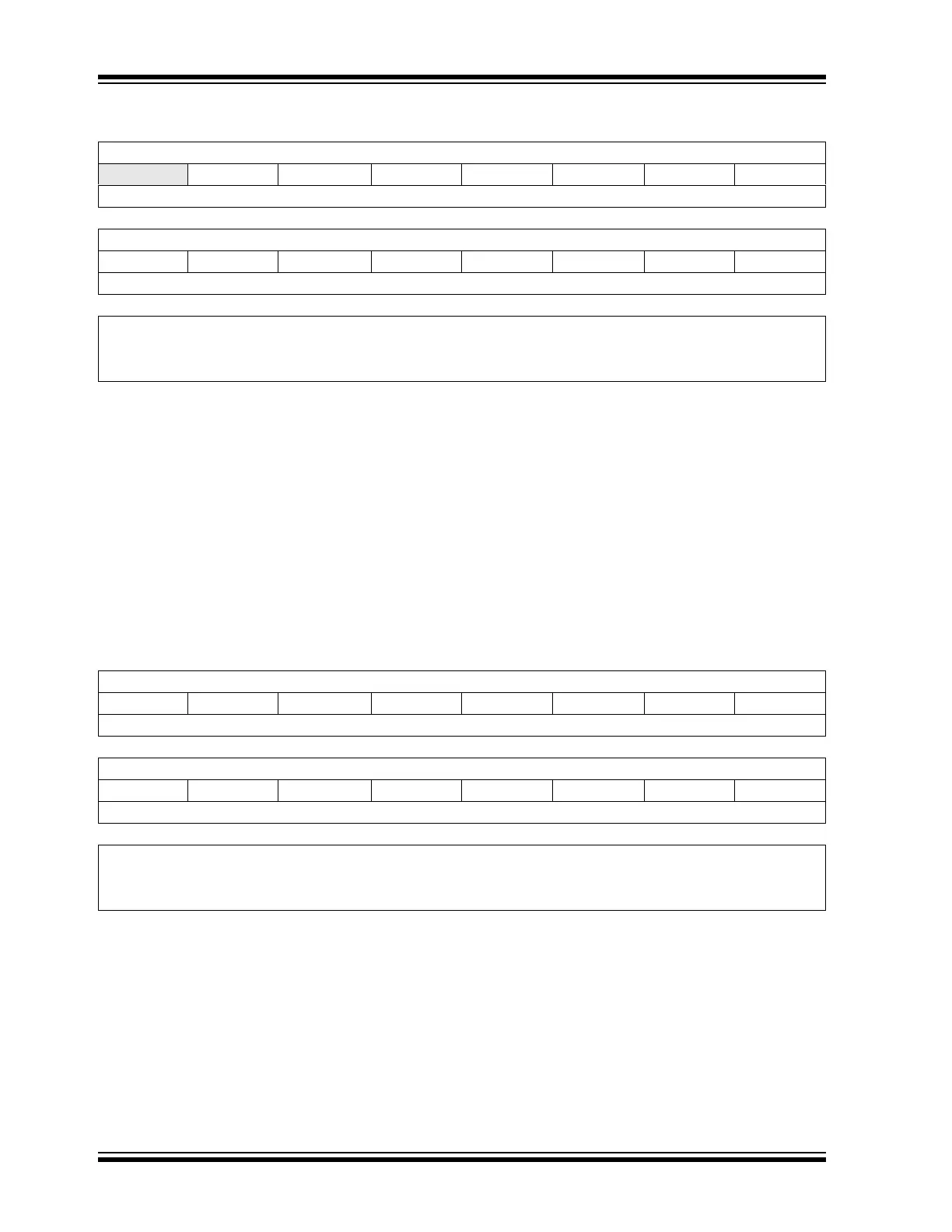

Register 3-54: C1MASKxH: CAN Mask Register x High (x = 0 to 31)

U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

— MIDE MSID11 MEID17 MEID16 MEID15 MEID14 MEID13

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

MEID12 MEID11 MEID10 MEID9 MEID8 MEID7 MEID6 MEID5

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as ‘0’

bit 14 MIDE: Identifier Receive Mode bit

1 = Matches only message types (standard or extended address) that correspond to the EXIDE bit in

the filter

0 = Matches either standard or extended address message if filters match

(i.e., if (Filter SID) = (Message SID) or if (Filter SID/EID) = (Message SID/EID))

bit 13 MSID11: Standard Identifier Mask bit

bit 12-0 MEID<17:5>: Extended Identifier Mask bits

In DeviceNet™ mode, these are the mask bits for the first 2 data bytes.

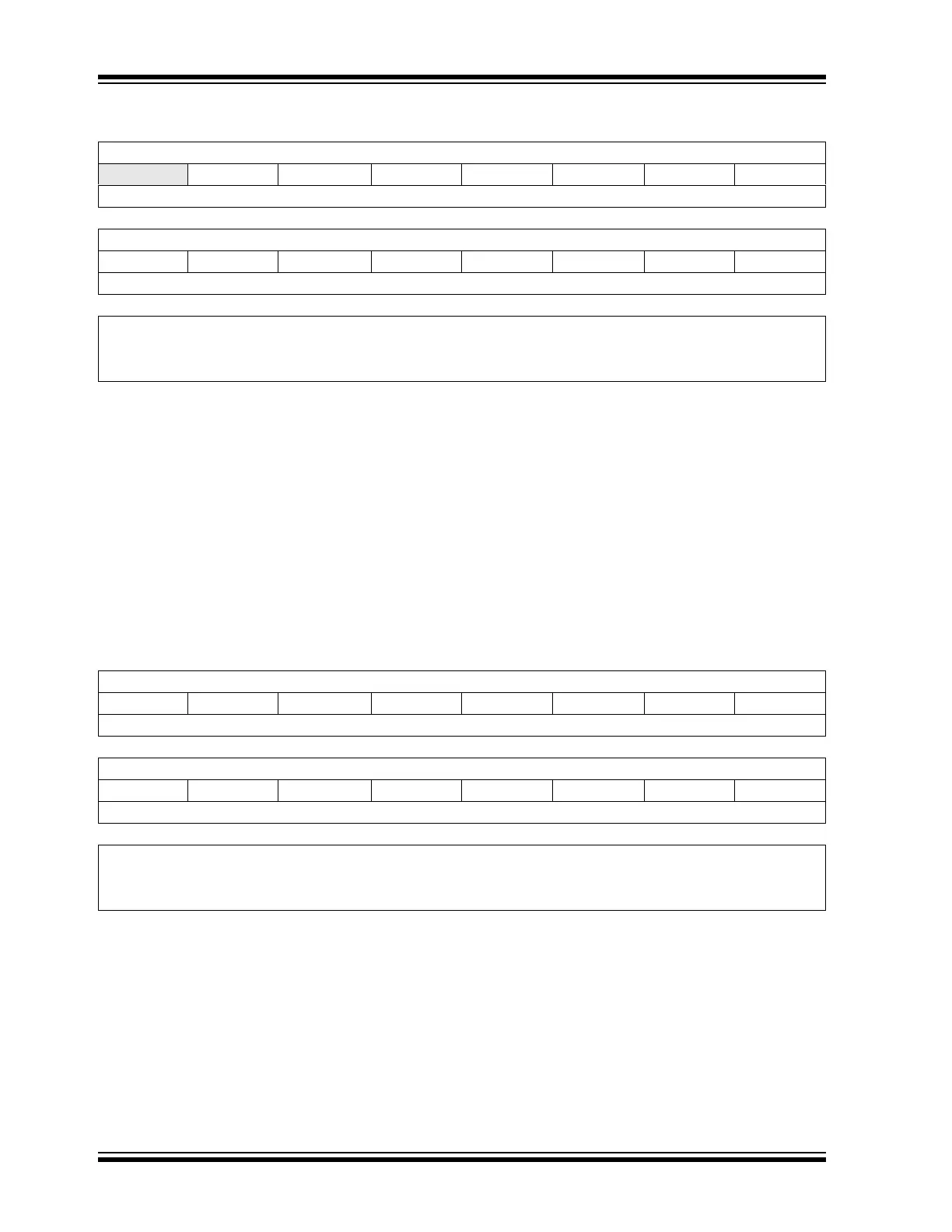

Register 3-55: C1MASKxL: CAN Mask Register x Low (x = 0 to 31)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

MEID4 MEID3 MEID2 MEID1 MEID0 MSID10 MSID9 MSID8

bit 15 bit 8

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

MSID7 MSID6 MSID5 MSID4 MSID3 MSID2 MSID1 MSID0

bit 7 bit 0

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as ‘0’

-n = Value at POR ‘1’ = Bit is set ‘0’ = Bit is cleared x = Bit is unknown

bit 15-11 MEID<4:0>: Extended Identifier Mask bits

In DeviceNet™ mode, these are the mask bits for the first 2 data bytes.

bit 10-0 MSID<10:0>: Standard Identifier Mask bits

Loading...

Loading...