15

(Continued)

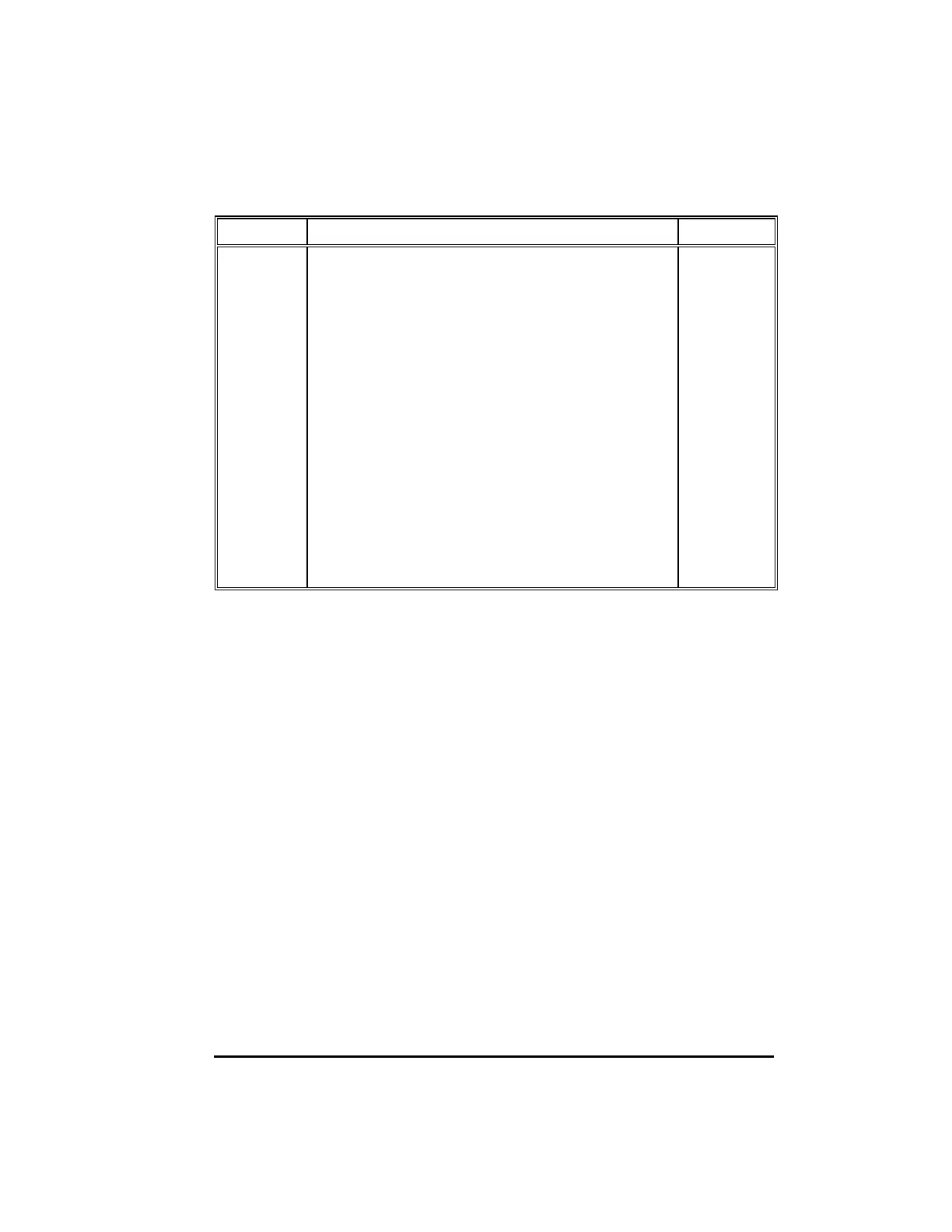

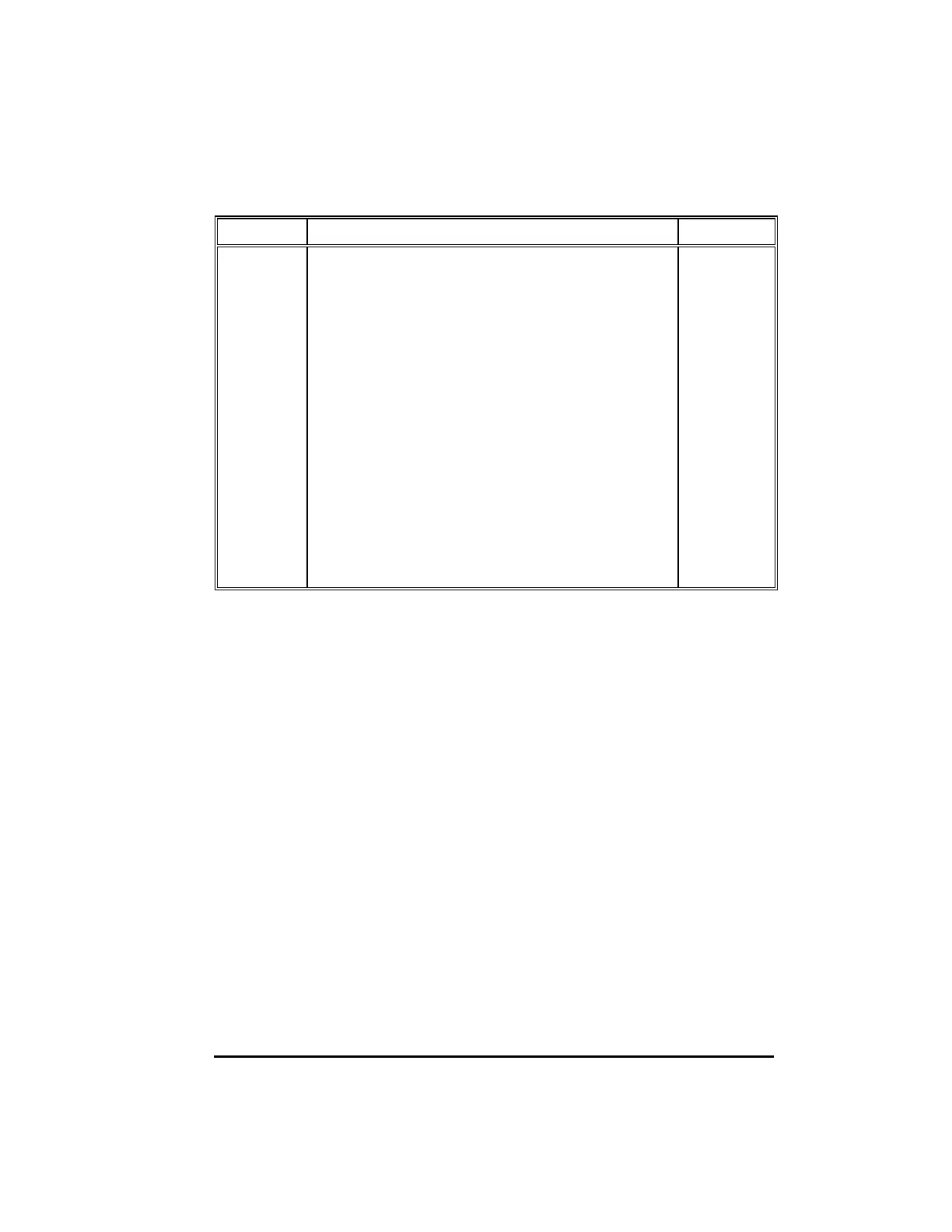

Reference Description Name

Socket 7 AMD K6 processor features:

•

Advanced 6 issue RISC86 superscalar

microarchitecture

- ten parallel specialized execution units

- multiple x86 to RISC86 instruction decoders

- advanced two-level branch prediction

- speculative execution

- out of order execution

- register renaming and data forwarding

- issues up to six RISC86 instructions per clock

•

Large on-chip split 64K Level-one (L1) cache

- 32K instruction cache with additional 20K of

predecode cache

- 32K writeback dual-ported data cache

- MESI protocol support

•

High-performance IEEE 754-compatible and 854-

compatible floating-point unit

•

High-performance industry-standard MMX

instructions

•

AMD-3D technology

CPU

Table 2-1. Major Components Description

Loading...

Loading...