Transmitter Power Amplifier (PA) 40W 2-3

2.4 Low Intermediate Frequency (IF) and Receiver Back End

The 44.85 MHz first IF signal from the second IF amplifier feeds the IF IC (U3101) at pin1. Within the

IF IC the 44.85 MHz high IF signal mixes with the 44.395 MHz second local oscillator to produce a

low IF signal of 455 kHz. The second LO frequency is determined by crystal Y3101. The second IF

signal is amplified and filtered by an external pair of 455 kHz ceramic filters (FL3112 and FL3114) for

20/25 kHz channel spacing, or FL3111 and FL3113/F3115 for 12.5 kHz channel spacing. These

pairs are selectable via BWSELECT. The filtered output from the ceramic filters is applied to the

limiter input pin of the IF IC (pin 14).

The IF IC contains a quadrature detector using a ceramic phase-shift element (Y3102) to provide

audio detection. Internal amplification provides an audio output level of 120 mV rms (at 60%

deviation) from U3103, pin 8 (DISCAUDIO) which is fed to ASFIC_CMP U0221, pin 2 (part of the

controller circuits).

A received signal strength indicator (RSSI) signal is available at U3101, pin 5, which has a dynamic

range of 70 dB. The RSSI signal is interpreted by the µP (U0101, pin 63) and is available at

accessory connector J0501-15.

3.0 Transmitter Power Amplifier (PA) 40W

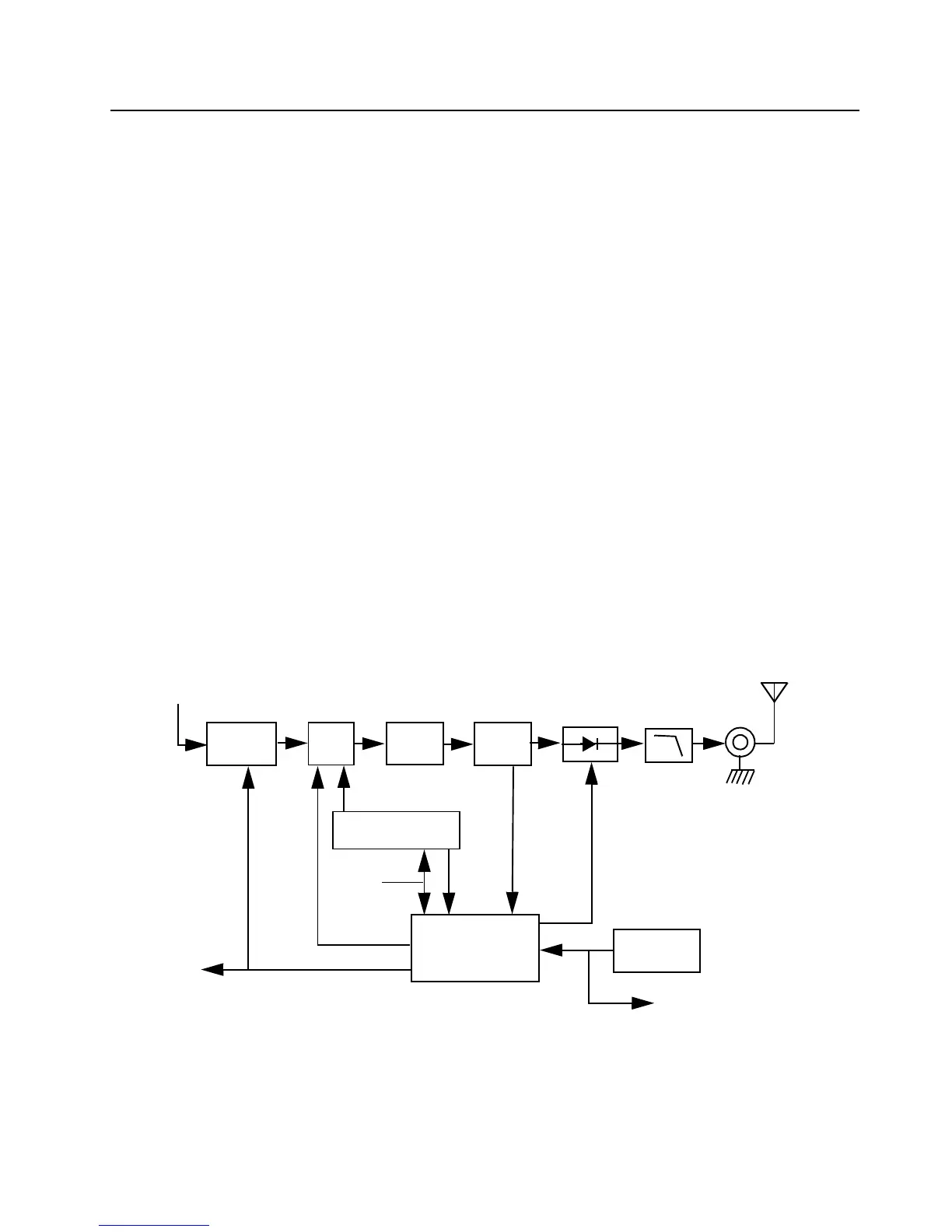

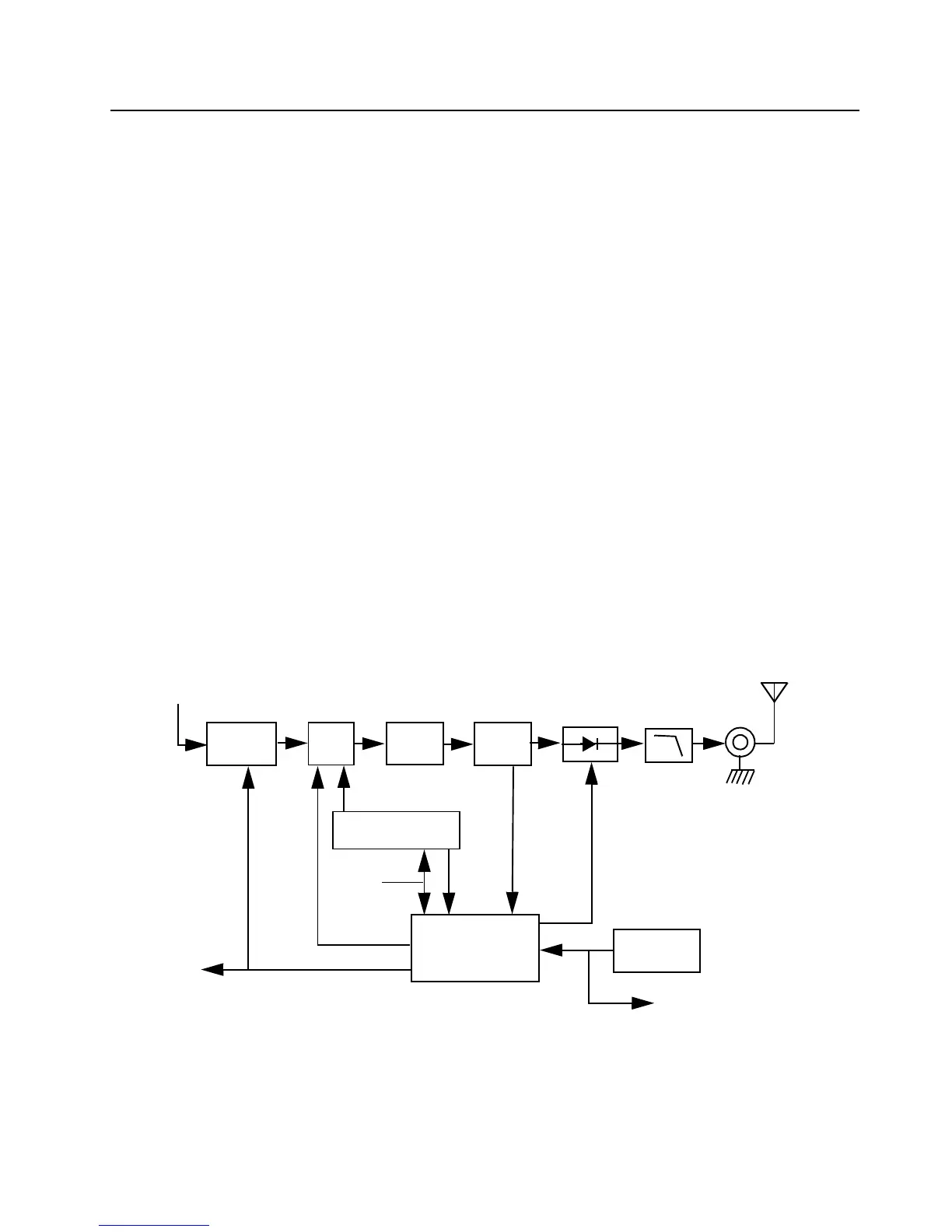

The radio’s 40W power amplifier (PA), shown in Figure 2-2, is a four-stage amplifier used to amplify

the output from the VCOBIC to the radio transmit level. The first stage is an LDMOS predriver

(U5401) controlled by pin 4 of PCIC (U5501) via Q5473 (CNTLVLTG). This stage is followed by

another LDMOS stage (Q5421), LDMOS stage Q5431, and a bipolar final stage (Q5441). Device

Q5401 is surface mounted and Q5421, Q5431, and Q5441 are directly attached to the heat sink.

Figure 2-2 UHF Transmitter Block Diagram

PCIC

Pin Diode

Antenna

Switch

RF Jack

Antenna

Harmonic

Filter

Power

Sense

PA-Final

Stage

PA

Driver

From VCO

Controlled

Stage

Vcontrol

Bias 1

Bias 2

To Microprocessor

Temperature

Sense

SPI BUS

ASFIC_CMP

PA

PWR

SET

To Microprocessor

Loading...

Loading...