B. Digital Architecture

The Motorola microprocessor, in conjunction with

the SLIC, performs the functions of controlling the inter-

nal workings of the radio, as well as interfacing with the

outside world. The microprocessor has 1K of RAM and

512 bytes of EEPROM on the chip. In some versions

the controller board enhances the capabilities of the

microprocessor chip by providing 256K or 512K of

FLASH memory, 32K static RAM, and 8K or 32K of

EEPROM. Other versions use masked programmed

ROM.

The “FLASH” open controller is flexible and capable

of firmware being reprogrammed to support future fea-

tures. The controller, through communication busses,

programs all applicable ICs in the radio (including those

on the transceiver board) for proper operation in the

designated frequency band.

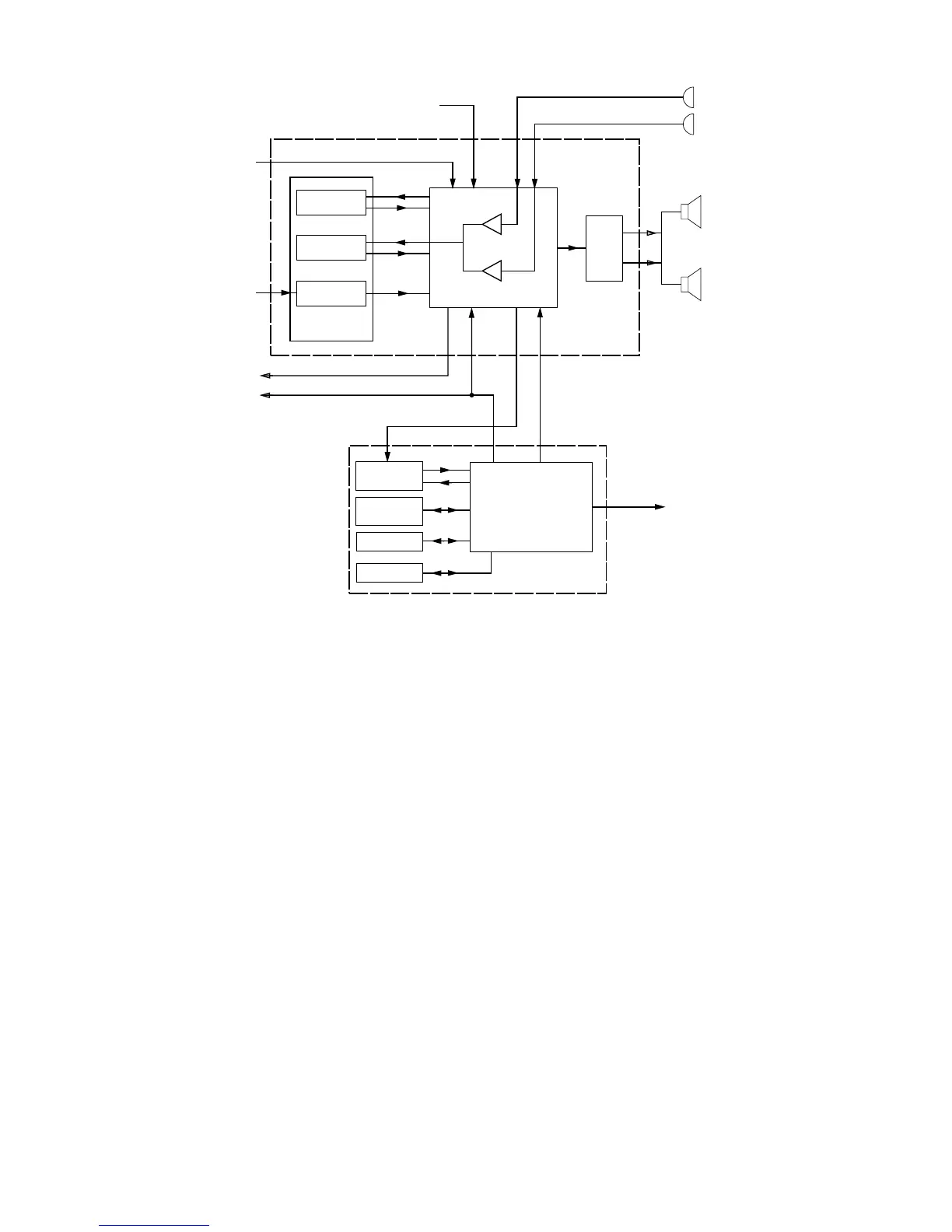

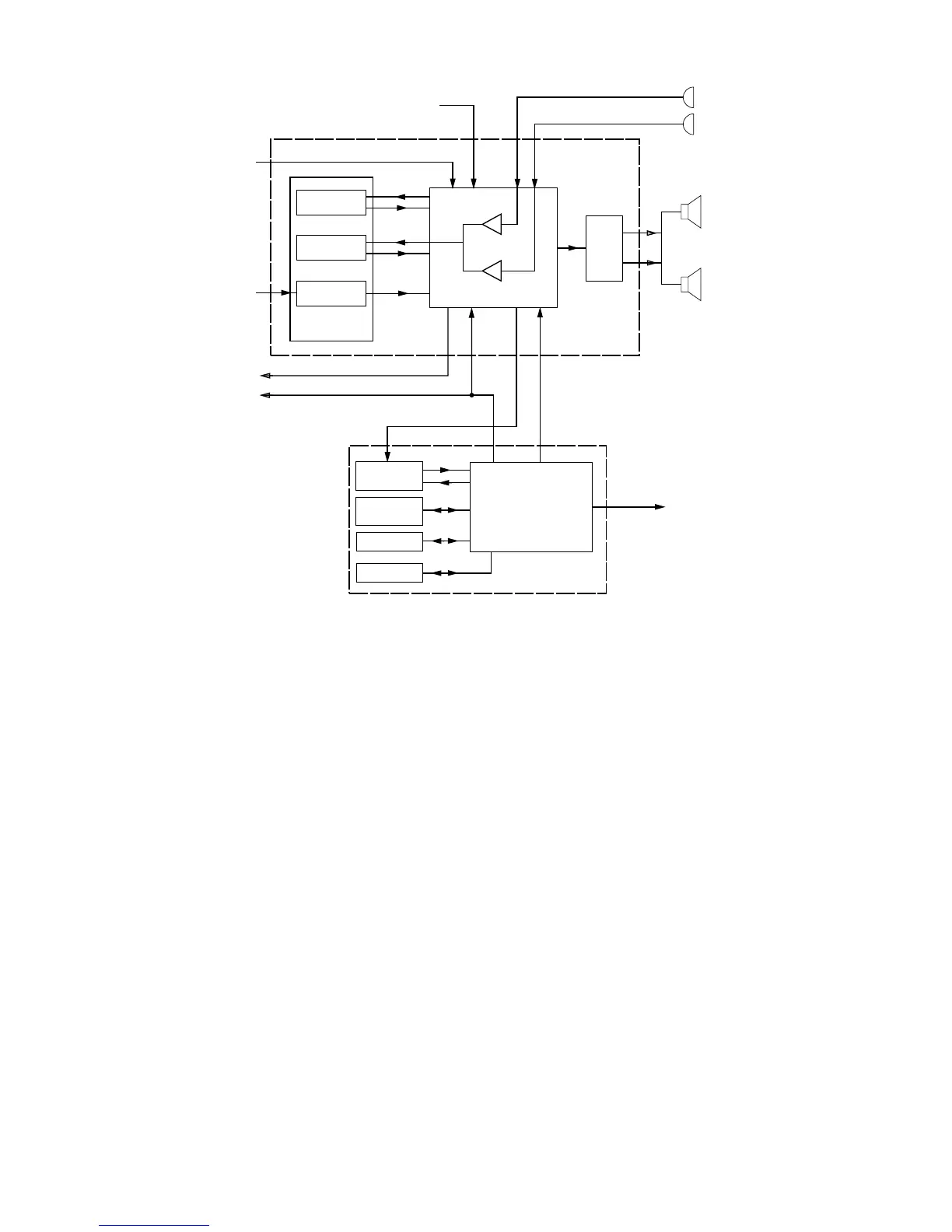

C. Audio Signalling Architecture

The Motorola custom integrated circuit, ASF IC, per-

forms audio signal shaping and filtering. The ASF IC

also encodes and decodes Private-Line (PL), Digital Pri-

vate-Line (DPL), and Motorola Digital Communication

(MDC) signals, as well as decoding trunking signals.

In the transmit mode, the ASF IC amplifies and

shapes the modulating signal on its way to the modulat-

ing port of the FGU. In the receive mode, the ASF IC

amplifies and filters the demodulated signal and applies

it to the audio PA, which drives the internal or external

radio speaker. The ASF IC not only performs pre-

emphasis and de-emphasis, but also performs the

squelch functions and provides the microprocessor with

a clock signal.

9

Loading...

Loading...