2-2 | ni.com

Chapter 2 DAQ System Overview

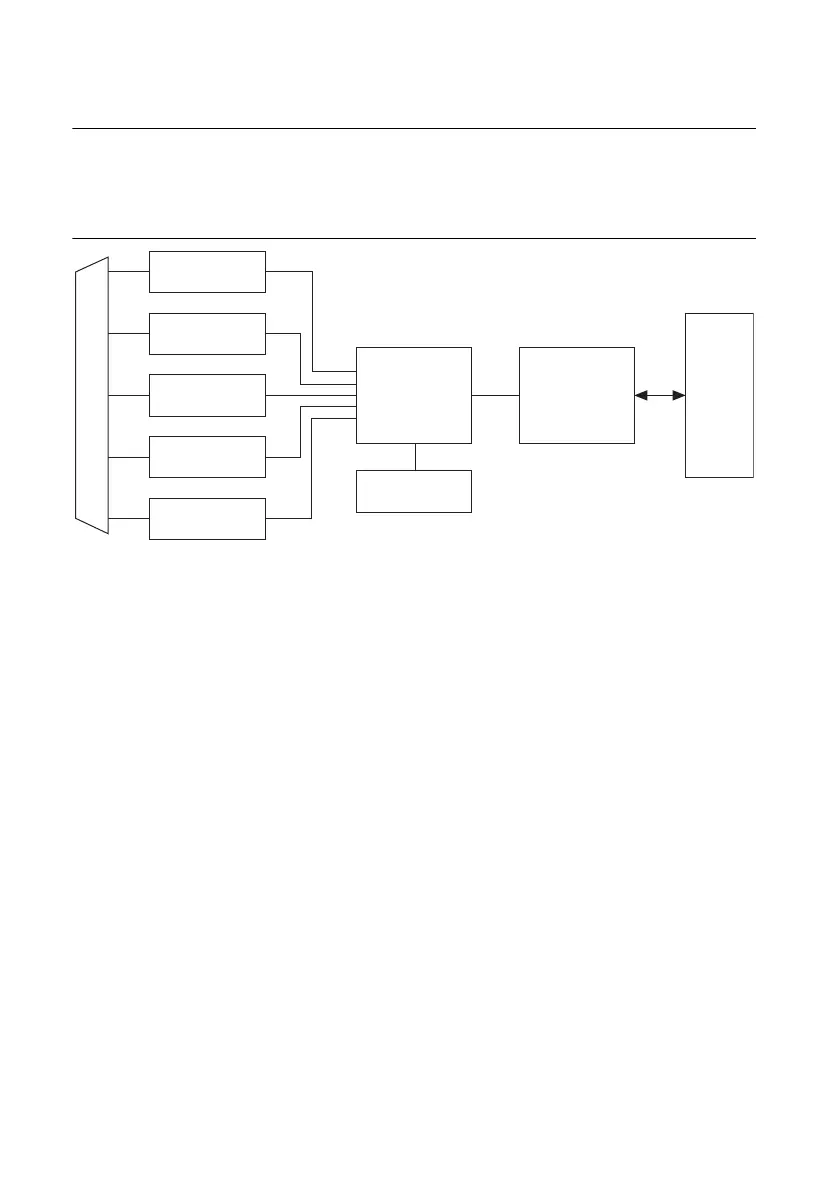

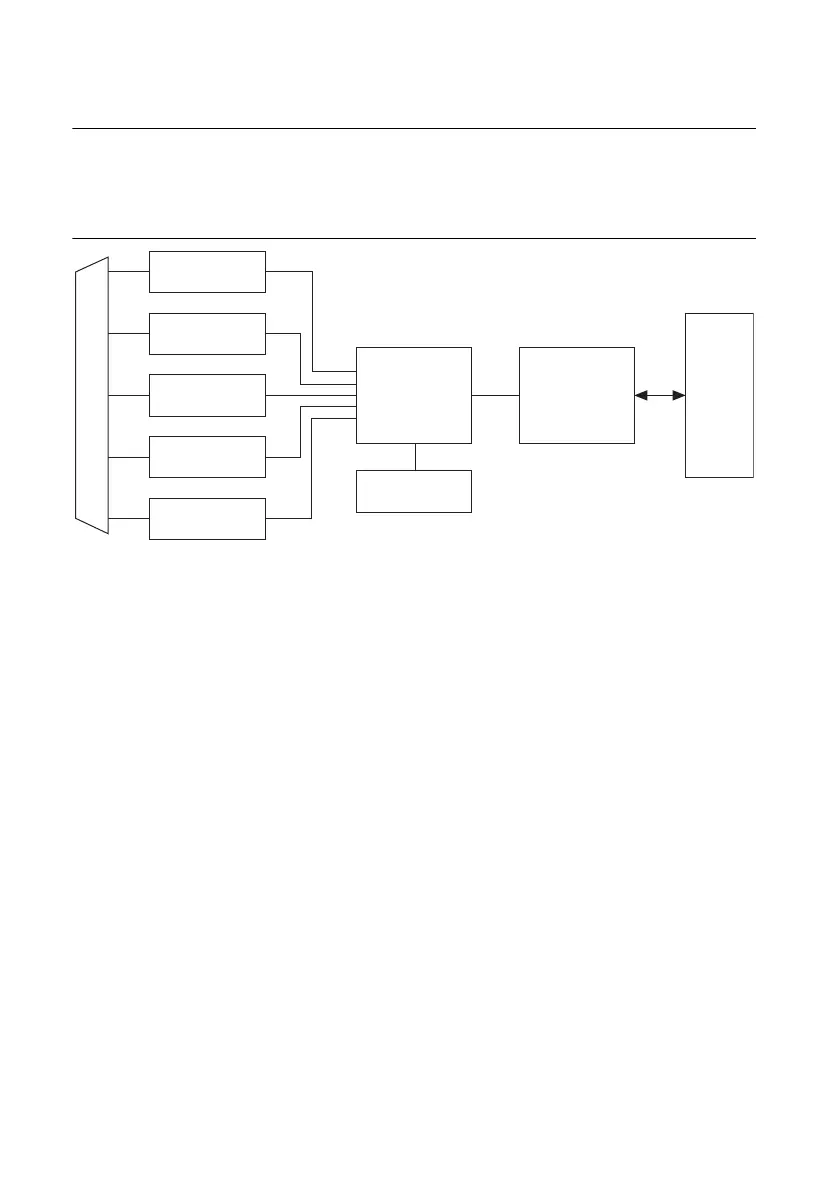

DAQ Hardware

DAQ hardware digitizes signals, performs D/A conversions to generate analog output signals,

and measures and controls digital I/O signals. Figure 2-2 features components common to all

X Series devices.

Figure 2-2. General X Series Block Diagram

DAQ-STC3

The DAQ-STC3 and DAQ-6202 implement a high-performance digital engine for X Series data

acquisition hardware. Some key features of this engine include the following:

• Flexible AI and AO sample and convert timing

• Many triggering modes

• Independent AI, AO, DI, DO, and counter FIFOs

• Generation and routing of RTSI signals for multi-device synchronization

• Generation and routing of internal and external timing signals

• Four flexible 32-bit counter/timer modules with hardware gating

• Digital waveform acquisition and generation

• Static DIO signals

• True 5 V high current drive DO

• DI change detection

• DO watchdog timers

• PLL for clock synchronization

• Seamless interface to signal conditioning accessories

• PCI Express/PXI Express interface

• Independent scatter-gather DMA controllers for all acquisition and generation functions

Analog Output

Digital I/O

Analog Input

Counters

PFI

Digital

Routing

and Clock

Generation

Bus

Interface

Bus

I/O Connector

RTSI

Loading...

Loading...