Copyright © 2011 NEXCOM International Co., Ltd. All Rights Reserved.

62

Chapter 4: BIOS Setup

DNA 1120/1120A User Manual

Chipset

This section is used to configure the system based on the specific features

of the chipset.

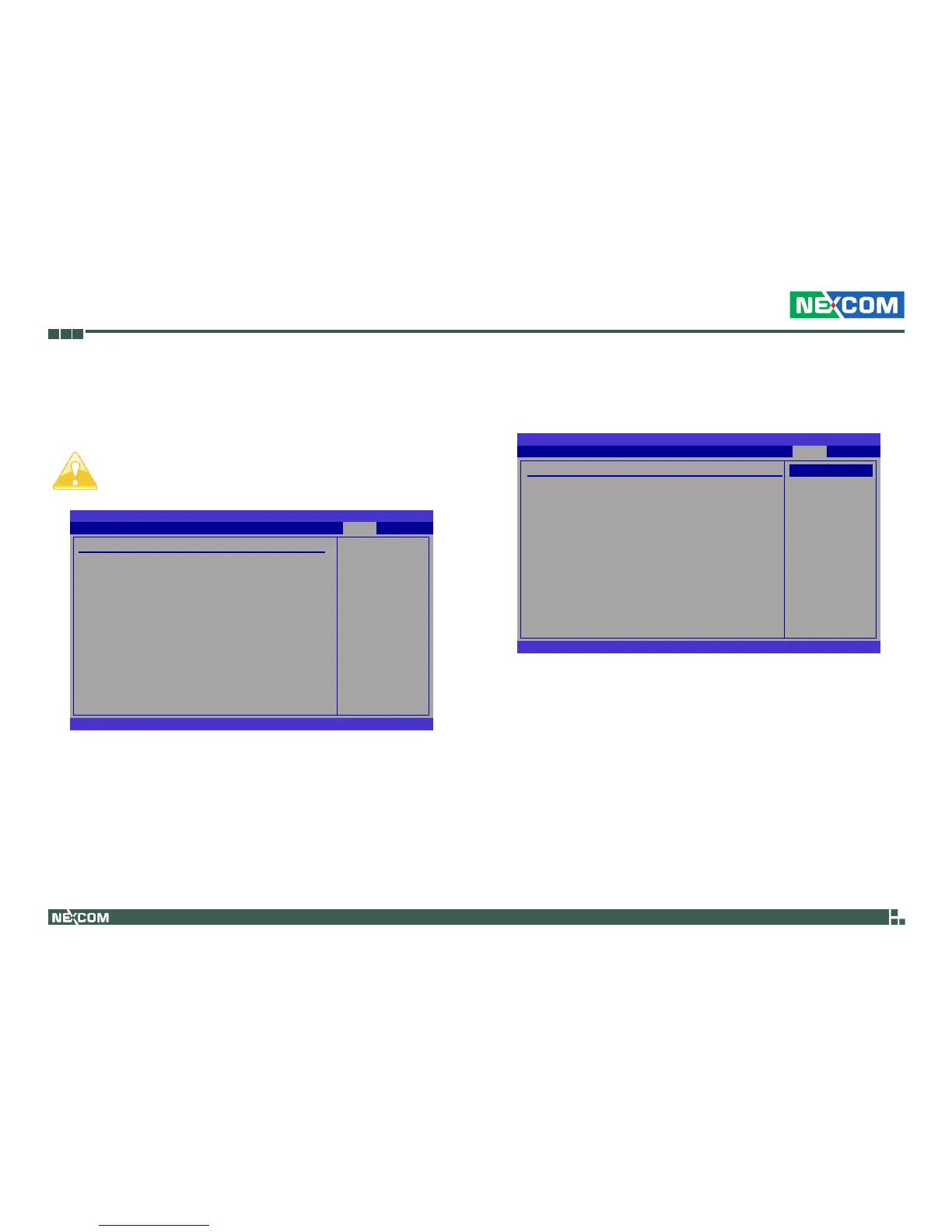

Setting incorrect field values may cause the system to malfunc-

tion.

BIOS SETUP UTILITY

Exit

v02.61 (C)Copyright 1985-2006, American Megatrends, Inc.

← → Select Screen

↑↓ Select Item

Enter Go to Sub Screen

F1 General Help

F10 Save and Exit

ESC Exit

Boot SecurityMain Advanced PCIPnP Chipset

Congure North Bridge

features.

Advanced Chipset Settings

WARNING: Setting wrong values in below sections

may cause system to malfunction.

u

North Bridge Conguration

u

South Bridge Conguration

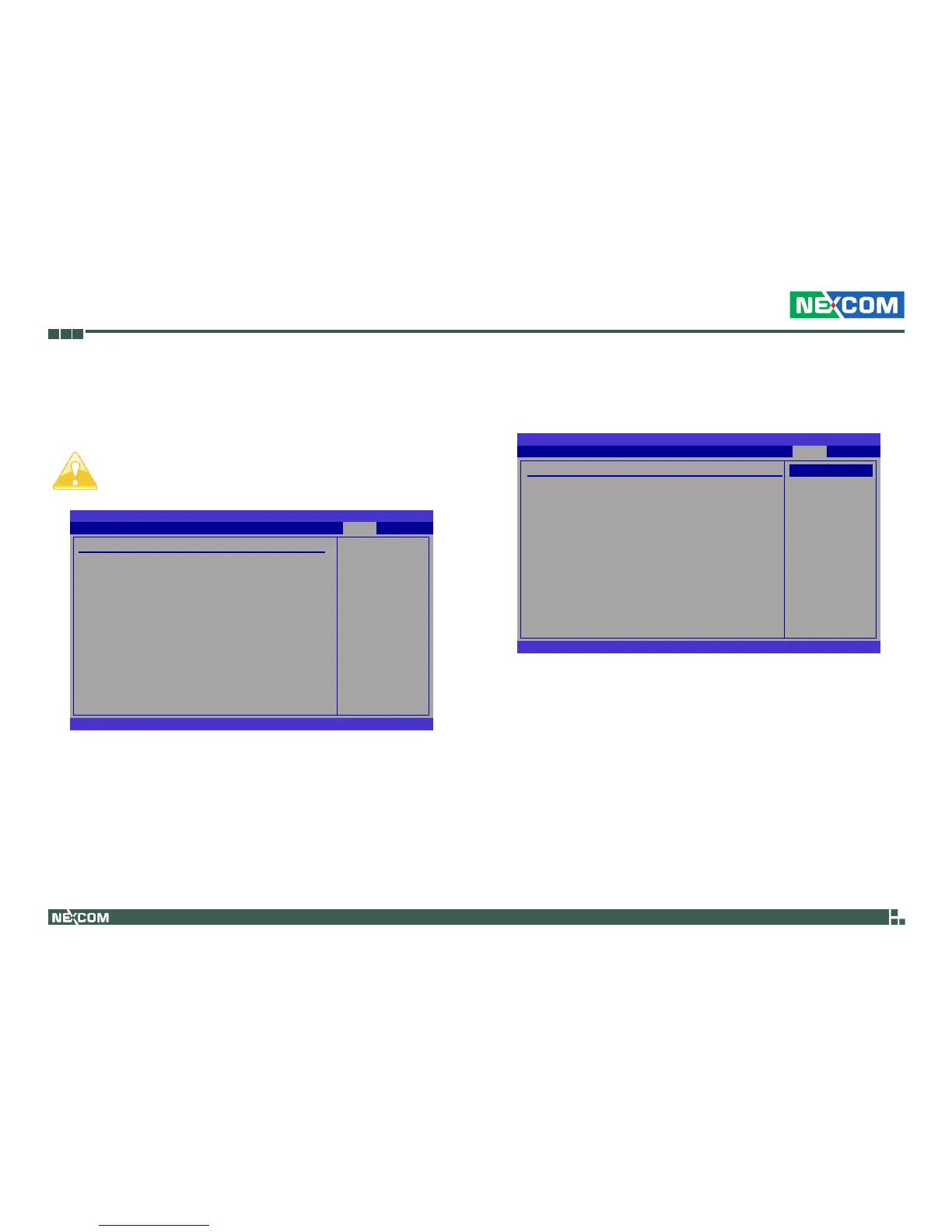

North Bridge Configuration

This section is used to configure the north bridge features.

BIOS SETUP UTILITY

v02.61 (C)Copyright 1985-2006, American Megatrends, Inc.

← → Select Screen

↑↓ Select Item

+

-

Change Option

F1 General Help

F10 Save and Exit

ESC Exit

North Bridge Chipset Conguration

PCI MMIO Allocation: 4GB to 3072MB

DRAM Frequency [Auto]

Congure DRAM Timing by SPD [Enabled]

Initiate Graphic Adapter [IGD]

Internal Graphics Mode Select [Enabled, 4MB]

PEG Port Conguration

u

Video Function Conguration

DRAM Frequency

Selects the frequency of the DRAM.

Configure DRAM Timing by SPD

The EEPROM on a PC SDRAM DIMM that has SPD (Serial Presence Detect)

data structure stores information about the module such as the memory

type, memory size, memory speed, etc. When this field is enabled, the

system will run according to the information in the EEPROM.

Auto

Max MHz

Options

Chipset

Loading...

Loading...