5 I/O Memory

5-18

CP2E CPU Unit Software User’s Manual(W614)

z Index Register Initialization

The Index Registers will be cleared in the following cases:

• The operating mode is changed from PROGRAM mode to RUN/MONITOR mode or vice-versa

and the IOM Hold Bit is OFF.

• The PLC’s power supply is cycled and the IOM Hold Bit is OFF or not set to be held in the PLC

Setup.

• A fatal error occurs (except for one created with FALS).

Note If the IOM Hold Bit (A500.12) is ON, the Index Registers will not be cleared when a FALS

error occurs or the operating mode is changed from PROGRAM mode to RUN/MONITOR

mode or vice-versa.

Precautions for Correct UsePrecautions for Correct Use

Precaution for Indirect Register Addressing with Index Registers

Do not use indirect register addressing to access areas outside of the I/O memory or areas

reserved by the system.

An Illegal Access Error will occur if access is attempted. Refer to A-5 Memory Map for details on

the limits of PLC memory addresses.

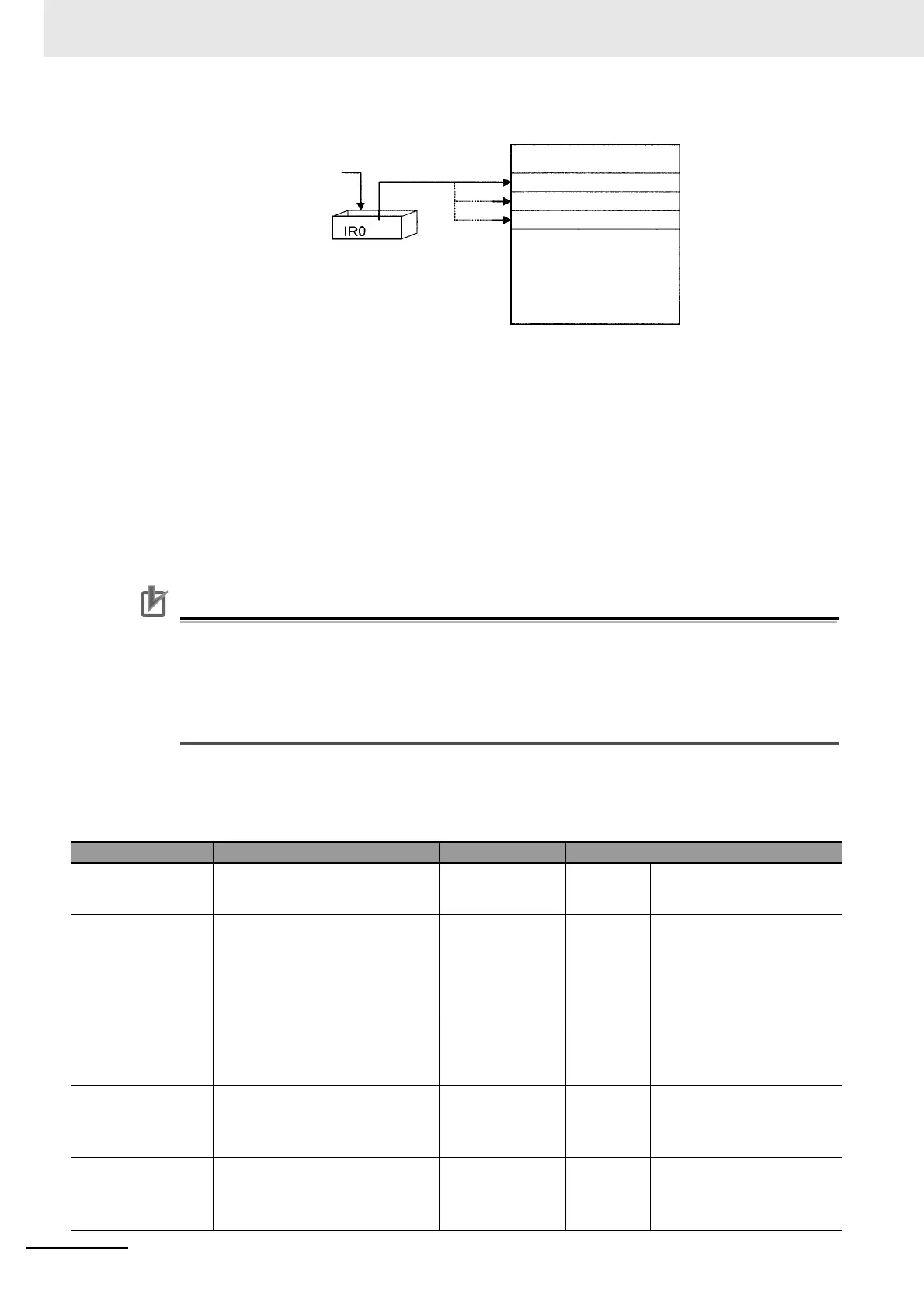

z Indirect Addressing Variations

The following table shows the variations available when indirectly addressing I/O memory with Index

Registers. (IR@ represents an Index Register from IR0 to IR15.)

Variation Function Syntax Example

Indirect addressing The content of IR@ is treated as

the PLC memory address of a bit

or word.

,IR@ LD ,IR0 Loads the bit at the PLC

memory address contained

in IR0.

Indirect addressing

with constant offset

The constant prefix is added to the

content of IR@ and the result is

treated as the PLC memory

address of a bit or word.

The constant may be any integer

from –2,048 to 2,047.

Constant ,IR@

(Include a + or – in

the constant.)

LD +5,IR0 Adds 5 to the contents of IR0

and loads the bit at that PLC

memory address.

Indirect addressing

with DR offset

The content of the Data Register is

added to the content of IR@ and

the result is treated as the PLC

memory address of a bit or word.

DR@,IR@ LD

DR0,IR0

Adds the contents of DR0 to

the contents of IR0 and loads

the bit at that PLC memory

address.

Indirect addressing

with auto-increment

After referencing the content of

IR@ as the PLC memory address

of a bit or word, the content is

incremented by 1 or 2.

Increment by 1:

,IR@+

Increment by 2:

,IR@++

LD , IR0++ Loads the bit at the PLC

memory address contained

in IR0 and then increments

the content of IR0 by 2.

Indirect addressing

with auto-decrement

The content of IR@ is decremented

by 1 or 2 and the result is treated

as the PLC memory address of a

bit or word.

Decrement by 1:

,–IR@

Decrement by 2:

,– –IR@

LD , – –IR0 Decrements the content of

IR0 by 2 and then loads the

bit at that PLC memory

address.

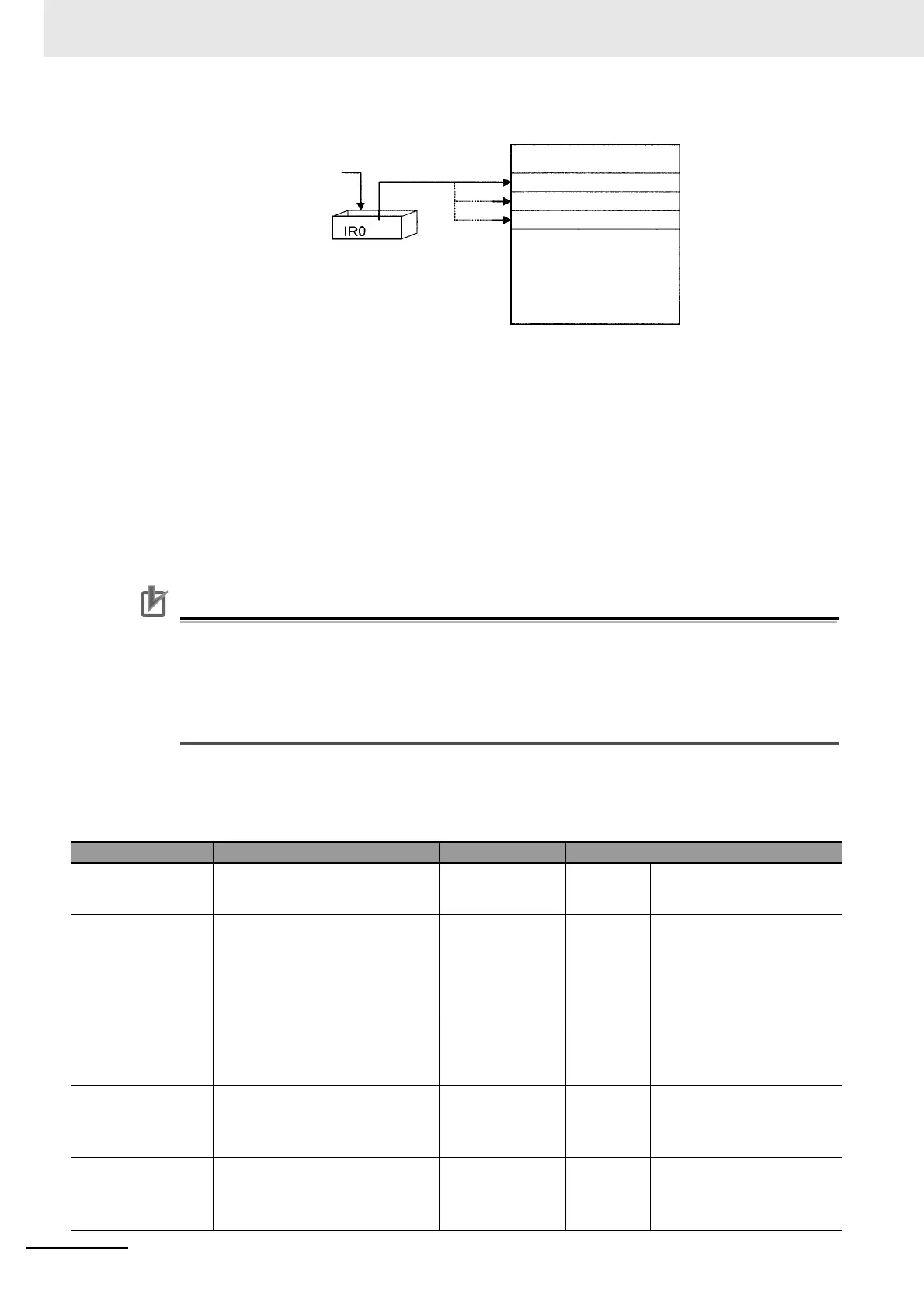

I/O Memory

Pointer

Set to a base value

with MOVR(560) or

MOVRW(561).

Loading...

Loading...