IC Data Sheets

EN 29TCM3.2L LA 8.

2009-Jun-19

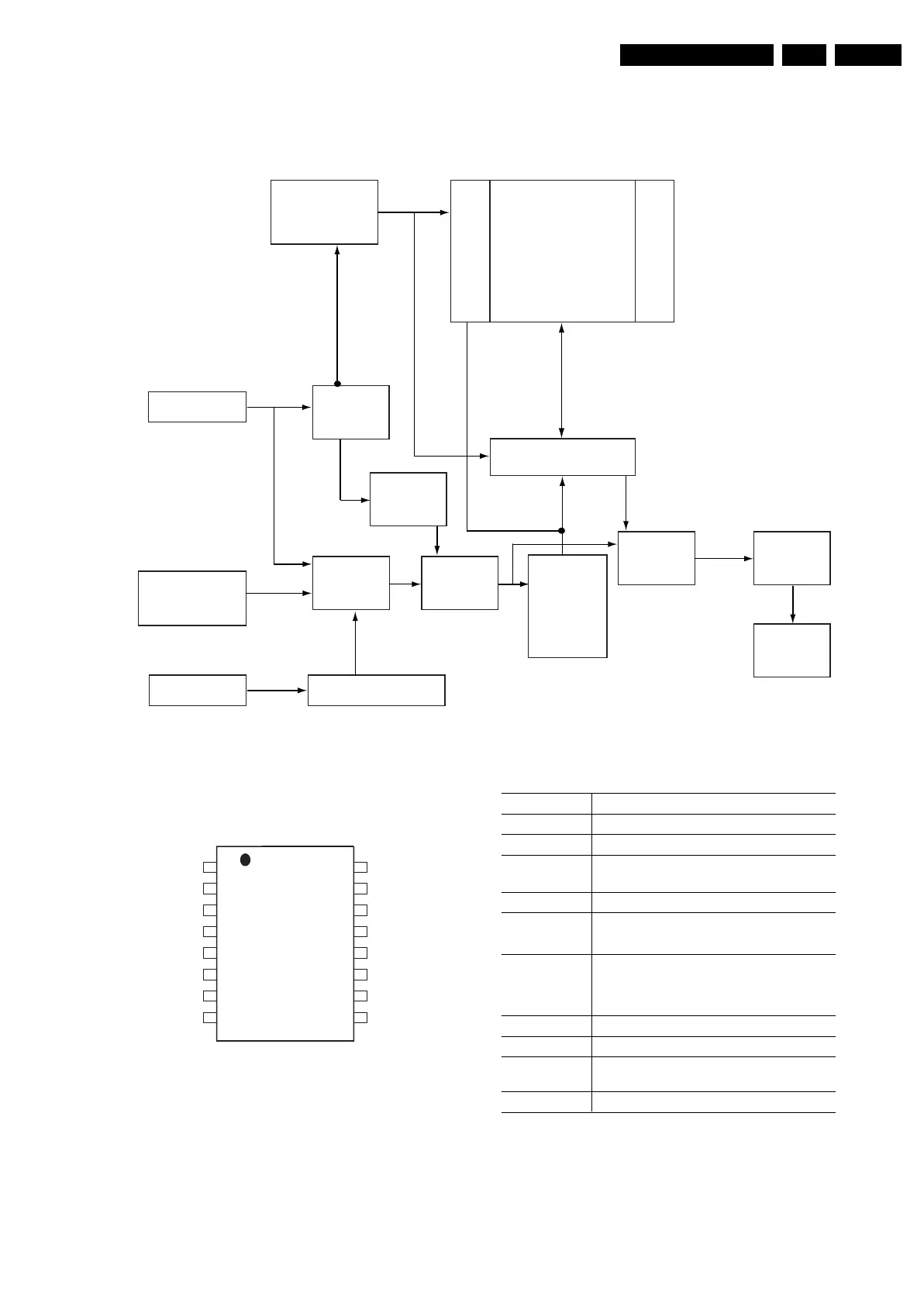

8.5 Diagram B02, MX25L3205 (IC U10)

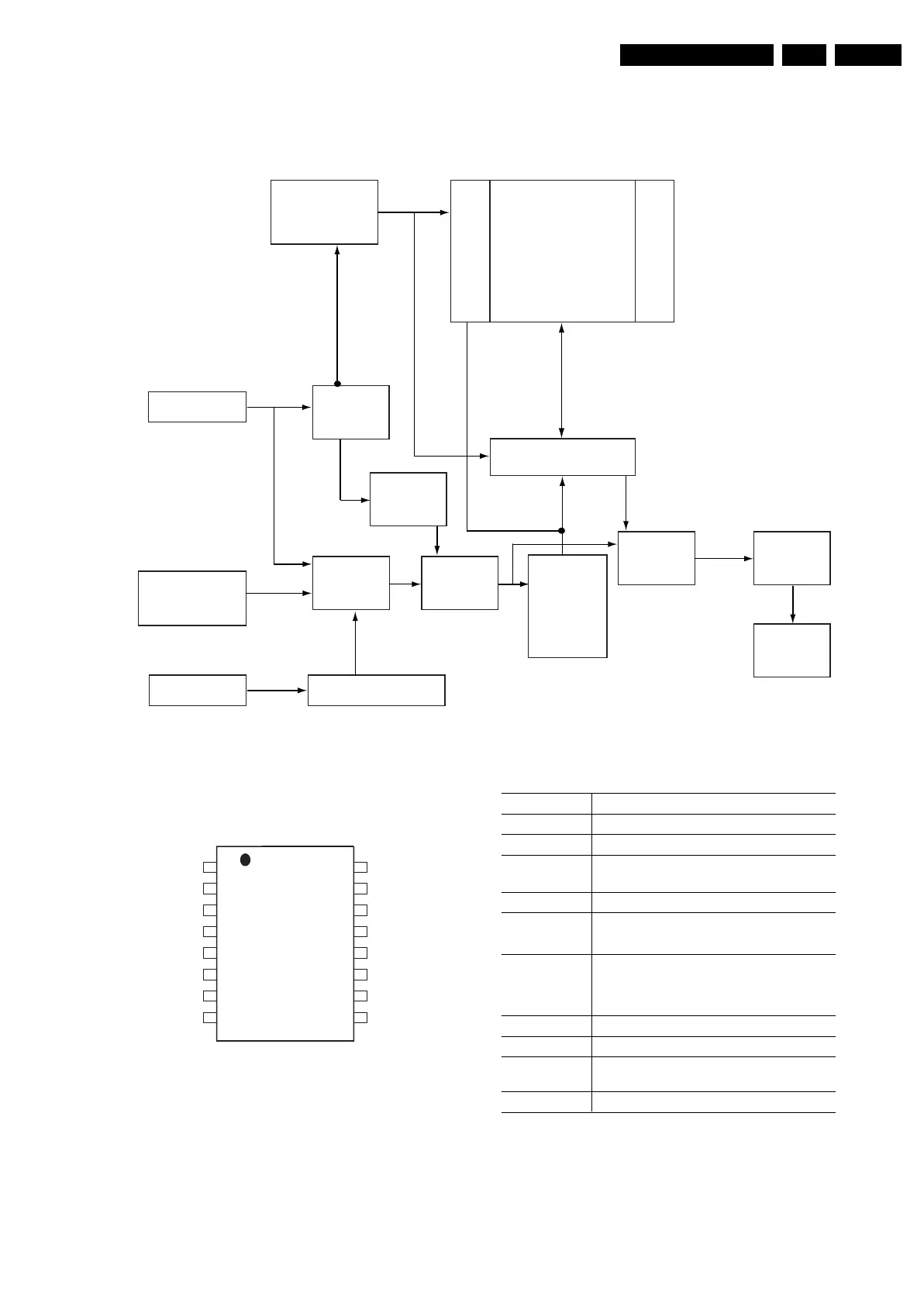

Figure 8-5 Internal block diagram and pin configuration

Block Diagram

Pin Configuration

18520_308_090325.eps

090325

SYMBOL DESCRIPTION

CS# Chip Select

SI Serial Data Input

SO/PO7(1) Serial Data Output or Parallel Data

output/input

SCLK Clock Input

HOLD#(2) Hold, to pause the serial communication

(HOLD# is not for parallel mode)

WP#/ACC Write Protection: connect to GND;

12V for program/erase acceleration:

connect to 12V

VCC + 3.3V Power Supply

GND Ground

PO0~PO6 Parallel data output/input (PO0~PO6 can

be connected to NC in serial mode)

NC No Internal Connection

PIN DESCRIPTION

16-PIN SOP (300 mil)

Note:

1. PO0~PO7 are not provided on 8-LAND SON package.

2. HOLD# is recommended to connect to VCC during

parallel mode.

1

2

3

4

5

6

7

8

HOLD#

VCC

NC

PO2

PO1

PO0

CS#

SO/PO7

16

15

14

13

12

11

10

9

SCLK

SI

PO6

PO5

PO4

PO3

GND

WP#/ACC

Address

Generator

Memory Array

Y-Decoder

X-Decoder

additional 4Kb

Data

Register

SRAM

Buffer

SI

CS#, ACC,

WP#,HOLD#

SCLK Clock Generator

State

Machine

Mode

Logic

Sense

Amplifier

HV

Generator

Output

Buffer

SO

Loading...

Loading...