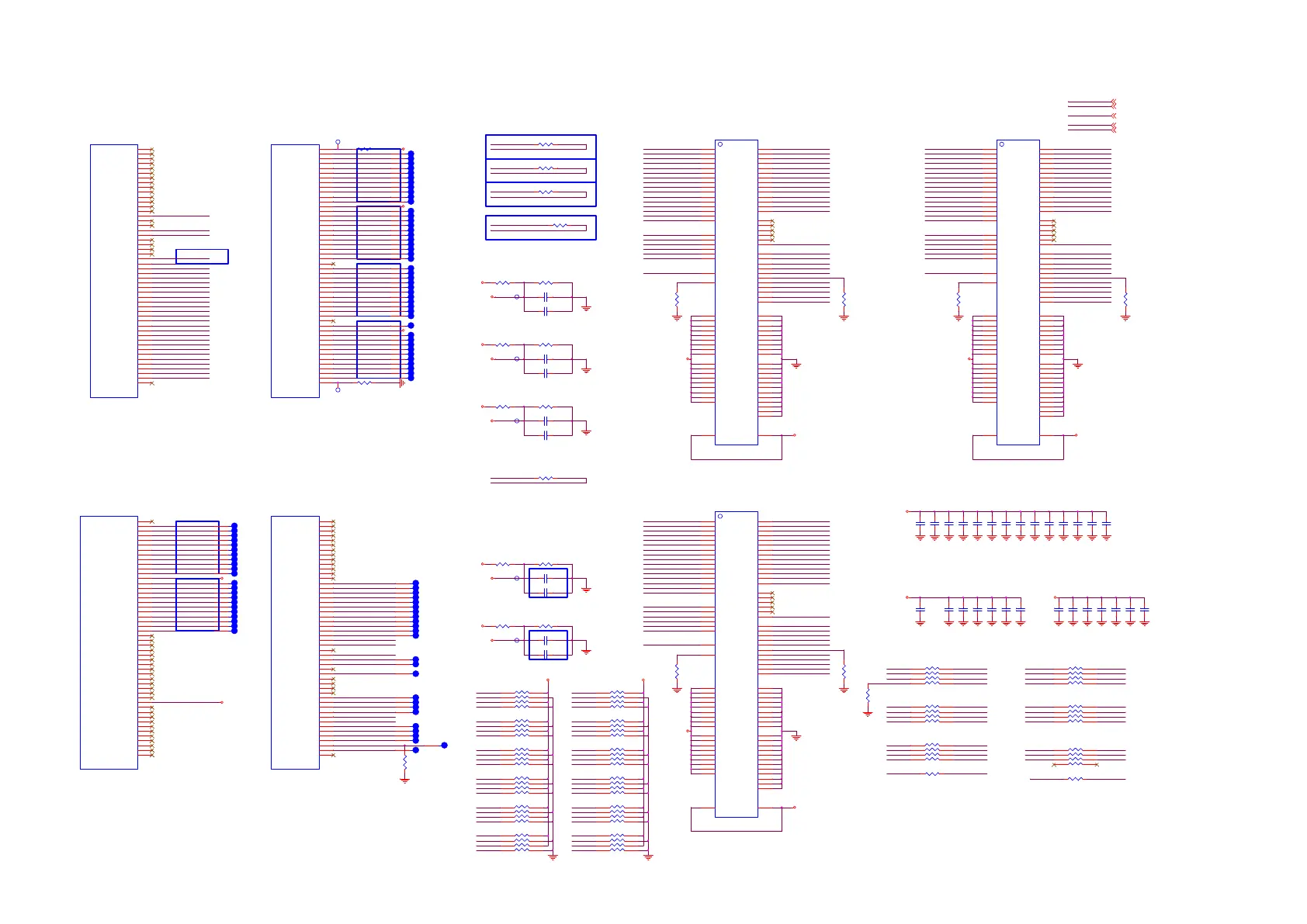

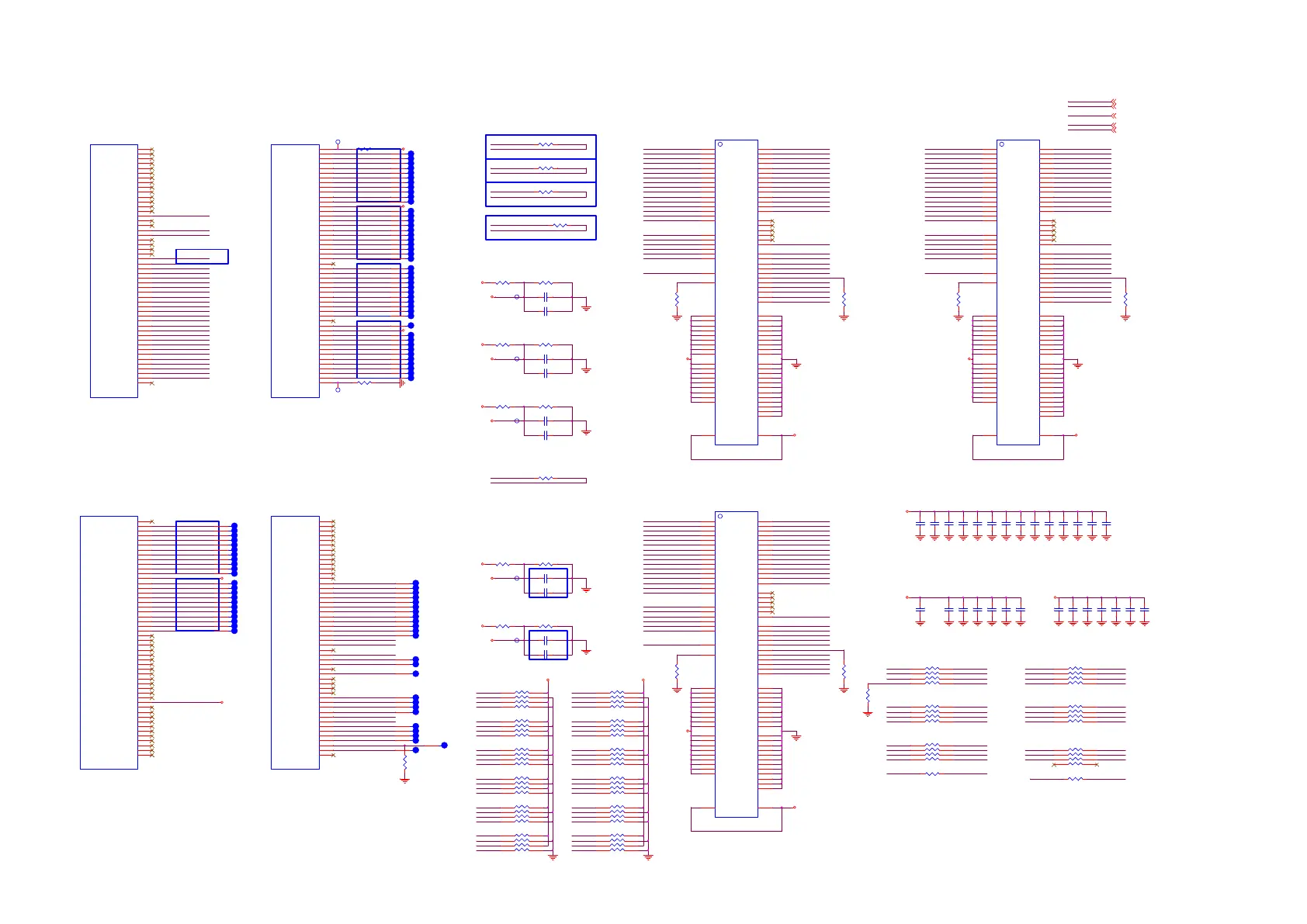

9-5-9 FPGAd_DDR

C0-DQ23

C0-MCLKn

C0-MCLKp

C1-DQ11

R3014

100R 1%

C1-DQ14

C1-A11

C0-A10

TP4025

1

C1-DQ2 C1-A2

C0-A1

TP4056

1

C0-A13

C1-A7

C0-DQ17

R4513

22 OHM

TP3996

1

C0-R-A5

C0-R-RASn

C0-R-A4

C0-R-A0

C0-R-BA0

C0-R-A8

C0-R-A9

C0-A5

C0-R-A1

C0-R-A14

C0-R-A11

C0-R-A13

C0-R-A10

C0-R-A2C0-RASn

C0-A6

C0-A3

C0-A8C0-RESETn

C0-ODT

C0-CKE

C0-CSn

C0-R-A12

C0-BA2

C0-R-WEn

C0-A9

C0-A0

C0-BA0

RP4422

22R

1

2

3

4

8

7

6

5

RP4423

22R

1

2

3

4

8

7

6

5

RP4424

22R

1

2

3

4

8

7

6

5

U3700-6

XC7K160T-2FBG676I4397

IO_0_VRN_33

U9

IO_L1P_T0_33

V11

IO_L1N_T0_33

W11

IO_L2P_T0_33

V8

IO_L2N_T0_33

V7

IO_L3P_T0_DQS_33

W10

IO_L3N_T0_DQS_33

W9

IO_L4P_T0_33

Y8

IO_L4N_T0_33

Y7

IO_L5P_T0_33

Y11

IO_L5N_T0_33

Y10

IO_L6P_T0_33

V9

IO_L6N_T0_VREF_33

W8

IO_L7P_T1_33

AE7

IO_L7N_T1_33

AF7

IO_L8P_T1_33

AA8

IO_L8N_T1_33

AA7

IO_L9P_T1_DQS_33

AC8

IO_L9N_T1_DQS_33

AD8

IO_L10P_T1_33

AB7

IO_L10N_T1_33

AC7

IO_L11P_T1_SRCC_33

AA9

IO_L11N_T1_SRCC_33

AB9

IO_L12P_T1_MRCC_33

AC9

IO_L12N_T1_MRCC_33

AD9

IO_L13P_T2_MRCC_33

AB11

IO_L13N_T2_MRCC_33

AC11

IO_L14P_T2_SRCC_33

AA10

IO_L14N_T2_SRCC_33

AB10

IO_L15P_T2_DQS_33

AB12

IO_L15N_T2_DQS_33

AC12

IO_L16P_T2_33

AA13

IO_L16N_T2_33

AA12

IO_L17P_T2_33

AC13

IO_L17N_T2_33

AD13

IO_L18P_T2_33

Y13

IO_L18N_T2_33

Y12

IO_L19P_T3_33

AD11

IO_L19N_T3_VREF_33

AE11

IO_L20P_T3_33

AD10

IO_L20N_T3_33

AE10

IO_L21P_T3_DQS_33

AE12

IO_L21N_T3_DQS_33

AF12

IO_L22P_T3_33

AE8

IO_L22N_T3_33

AF8

IO_L23P_T3_33

AE13

IO_L23N_T3_33

AF13

IO_L24P_T3_33

AF10

IO_L24N_T3_33

AF9

IO_25_VRP_33

V12

C

L

K

t

e

r

m

i

n

a

t

i

o

n

RP4412

22R

1

2

3

4

8

7

6

5

RP4420

22R

1

2

3

4

8

7

6

5

C0-A4

C0-DQ9

RP4421

22R

1

2

3

4

8

7

6

5

C0-A7

C0-R-BA1

C0-R-CASn

C0-R-BA2

C0-R-RESETn

C0-R-ODT

C0-R-CKE

C0-R-CSn

C0-R-A7

C0-A11

C0-A13

C0-A1

C0-A14

C0-WEn

C0-A4

C0-BA1

R3001

100R 1%

C0-R-A3

C0-A10

C0-A2

C0-A12

C0-CASn

R4512

22 OHM

C0-R-A6

C1-DQ7

TP4026

1

C0-DQ25

TP4057

1

TP3997

1

SSC-SEL0 8

C1-DQ12

C1-DQ15

C0-DQ17

C1-A12

C0-A11

TP4027

1

TP3955

1

C1-DQ3 C1-A3

C0-A2

D

e

c

o

u

p

l

i

n

g

a

d

d

e

d

a

t

t

h

e

b

o

r

d

e

r

o

f

t

h

e

+1V5-FPGA plane (bottom) at the double DDR

V

R

E

F

v

o

l

t

a

g

e

d

i

v

i

d

e

r

s

TP4058

1

TP3937

1

C0-R-CASn

C0-R-RASn

C0-R-BA0

C0-R-BA1

C0-R-A14

C0-R-A11

C0-R-A12

C0-R-RESETn

C0-R-A13

C0-R-WEn

C0-DQ18

C1-A8

C0-R-A7

C0-R-A8

C0-R-A10

C0-R-A9

C0-MCLKn

C0-MCLKp

C0-R-A2

C0-R-A3

C0-R-A5

C0-R-A4

C0-R-A6

C0-R-BA2

C0-R-A0

C0-R-A1

TP3998

1

C0-A5

C0-DQ10

TP3956

1

TP4028

1

C0-DQ26

R3024

100R 1%

C0-DDR-SYS-CLKn

C0-DDR-SYS-CLKp

TP3938

1

TP4059

1

TP3999

1

C1-DQ13

C0-DQ18

C1-A13

C0-A12

TP3957

1

C1-DQ4

TP4029

1

C1-A4

C0-A3

R3000

100R 1%

RP4414 47R

1

2

3

4

8

7

6

5

C1-RASn

C1-BA2

C1-WEn

C1-WEn

C1-RASn

RP4415 47R

1

2

3

4

8

7

6

5

C1-A9

C1-BA2

RP4416 47R

1

2

3

4

8

7

6

5

C1-A9

RP4417 47R

1

2

3

4

8

7

6

5

RP4418 47R

1

2

3

4

8

7

6

5

TP3939

1

C1-A12

C1-A13

RP4419 47R

1

2

3

4

8

7

6

5

C1-A13

C1-A9

TP4060

1

C1-A12

C1-BA0

C1-BA0

C1-A3

C1-A3

C1-BA1

+1V5-FPGA

C1-A8

C1-A8

C1-BA1

C1-A6

C1-CSn

C1-CSn

C1-A6

RP4413 47R

1

2

3

4

8

7

6

5

L

a

y

o

u

t

:

100Ohm differential - keep trace short

C1-CASn

TP4001

1

TP4000

1

C1-A1

C1-A11

C1-A11

C1-CASn

TP4003

1

RP4407 47R

1

2

3

4

8

7

6

5

TP4002

1

C1-A1

RP4408 47R

1

2

3

4

8

7

6

5

C1-A0

C0-A6

RP4409 47R

1

2

3

4

8

7

6

5

C1-A0

C0-DQ11

RP4410 47R

1

2

3

4

8

7

6

5

C1-A2

R3023

NC/4.7K 1/16W

C1-CKE

RP4411 47R

1

2

3

4

8

7

6

5

C1-A2

C1-A10

C1-CKE

C1-A4

C1-A10

C1-A5

C1-A5

C1-A7

C1-A7

U3700-7

XC7K160T-2FBG676I4397

IO_0_VRN_34

U4

IO_L1P_T0_34

U6

IO_L1N_T0_34

U5

IO_L2P_T0_34

U2

IO_L2N_T0_34

U1

IO_L3P_T0_DQS_34

W6

IO_L3N_T0_DQS_34

W5

IO_L4P_T0_34

V3

IO_L4N_T0_34

W3

IO_L5P_T0_34

U7

IO_L5N_T0_34

V6

IO_L6P_T0_34

V4

IO_L6N_T0_VREF _34

W4

IO_L7P_T1_34

Y3

IO_L7N_T1_34

Y2

IO_L8P_T1_34

V2

IO_L8N_T1_34

V1

IO_L9P_T1_DQS_34

AB1

IO_L9N_T1_DQS_34

AC1

IO_L10P_T1_34

W1

IO_L10N_T1_34

Y1

IO_L11P_T1_SRCC_34

AB2

IO_L11N_T1_SRCC_34

AC2

IO_L12P_T1_MRCC_34

AA3

IO_L12N_T1_MRCC_34

AA2

IO_L13P_T2_MRCC_34

AA4

IO_L13N_T2_MRCC_34

AB4

IO_L14P_T2_SRCC_34

AC4

IO_L14N_T2_SRCC_34

AC3

IO_L15P_T2_DQS_34

AA5

IO_L15N_T2_DQS_34

AB5

IO_L16P_T2_34

AB6

IO_L16N_T2_34

AC6

IO_L17P_T2_34

Y6

IO_L17N_T2_34

Y5

IO_L18P_T2_34

AD6

IO_L18N_T2_34

AD5

IO_L19P_T3_34

AD4

IO_L19N_T3_VREF_34

AD3

IO_L20P_T3_34

AD1

IO_L20N_T3_34

AE1

IO_L21P_T3_DQS_34

AF5

IO_L21N_T3_DQS_34

AF4

IO_L22P_T3_34

AE3

IO_L22N_T3_34

AE2

IO_L23P_T3_34

AE6

IO_L23N_T3_34

AE5

IO_L24P_T3_34

AF3

IO_L24N_T3_34

AF2

IO_25_VRP_34

T7

+1V5-FPGA

C1-A4

C1-ODT

C1-A14

C1-A14

C1-ODT

C0-DQ27

TP3958

1

TP4030

1

C0-DQ2

TP3940

1

SSC-SEL1 8

SSC-SEL1

TP4061

1

C0-DQ26

C0-DQ27

C0-DQ1

TP4004

1

TP4006

1

TP4005

1

TP4007

1

C0-DQ19

C0-A13

C1-DQ9

C1-DQ5 C1-A5

TP3959

1

C0-A4

TP4031

1

SSC-SEL0

TP3941

1

TP4062

1

C0-A7

C1-A1

C0-DQ12

TP4008

1

TP4010

1

TP4009

1

TP4011

1

C0-DQ28

TP3960

1

C0-R-CSn

C0-R-ODT

C0-R-CKE

C0-DQ3

TP4033

1

TP4032

1

C1-DQ1

C0-DQ19

C0-DDR-SYS-CLKn 8

C0-DDR-SYS-CLKn

TP3942

1

C1-A10

C0-DDR-SYS-CLKn

C0-DQ29

C0-DQ28

L

a

y

o

u

t

:

P

l

a

c

e

a

t

F

P

G

A

p

i

n

s

TP4063

1

D

e

c

o

u

p

l

i

n

g

f

o

r

(

d

u

a

l

)

D

D

R

d

e

v

i

c

e

s

(FPGA decoupling on another sheet)

TP4013

1

TP4012

1

C0-MCLKp

TP4014

1

R3013

100R 1%

TP4015

1

C0-MCLKn

C1-DQ10

U3001

W631GG6MB-12

VDD_0

B2

NC_0

J1

VSS_0

A9

VSSQ_0

B1

UDQS#

B7

VDDQ_0

A1

DQU6

B8

VSSQ_1

B9

UDM

D3

UDQS

C7

VSSQ_2

D1

DQU7

A3

VDDQ_1

A8

DQU1

C3

VDDQ_2

C1

VDDQ_3

C9

DQU0

D7

VDDQ_4

D2

DQU4

A7

VSSQ_3

D8

DQU3

C2

DQU2

C8

VSSQ_4

E2

DQU5

A2

VDD_1

D9

NC_1

J9

VSS_1

B3

VSSQ_5

E8

LDQS#

G3

VDDQ_5

E9

DQL6

G2

VSSQ_6

F9

LDM

E7

LDQS

F3

VSSQ_7

G1

DQL7

H7

VDDQ_6

F1

DQL1

F7

VDDQ_7

H2

DQL0

E3

VDDQ_8

H9

DQL4

H3

VSSQ_8

G9

DQL3

F8

DQL2

F2

BA2

M3

DQL5

H8

VDD_5

N1

VREFDQ

H1

VSS_2

E1

VSS_5

J8

CK

J7

VDD_2

G7

CKE

K9

WE#

L3

RAS#

J3

CK#

K7

ODT

K1

RESET#

T2

BA0

M2

BA1

N8

CAS#

K3

CS#

L2

A10/AP

L7

A1

P7

A2

P3

A0

N3

VDD_3

K2

VSS_3

G8

A3

N2

A5

P2

A6

R8

A4

P8

A7

R2

A9

R3

A11

R7

A8

T8

VSS_4

J2

VDD_4

K8

A12/BC#

N7

NC_3

L9

ZQ

L8

NC_2

L1

VREFCA

M8

NC_4

M7

NC

T3

NC_6

T7

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VDD_6

N9

VDD_7

R1

VDD_8

R9

C1-DQ6

C0-RESETn

+1V5-FPGA

C1-A6

+C1-VREF-M

C0-BA1

C0-A5

+C0-VREF-L

TP4034

1

TP4036

1

TP4035

1

TP4037

1

C1-RESETn

C1-BA1

R3005

240R 1%

+1V5-FPGA

+C1-VREF

TP3943

1

R3020

240R 1%

TP4064

1

U3700-4

XC7K160T-2FBG676I4397

IO_0_15

K15

IO_L1P_T0_AD0P_15

C16

IO_L1N_T0_AD0N_15

B16

IO_L2P_T0_AD8P_15

A18

IO_L2N_T0_AD8N_15

A19

IO_L3P_T0_DQS_AD1P_15

B17

IO_L3N_T0_DQS_AD1N_15

A17

IO_L4P_T0_AD9P_15

C19

IO_L4N_T0_AD9N_15

B19

IO_L5P_T0_AD2P_15

C17

IO_L5N_T0_AD2N_15

C18

IO_L6P_T0_15

D15

IO_L6N_T0_VREF_15

D16

IO_L7P_T1_AD10P_15

H16

IO_L7N_T1_AD10N_15

G16

IO_L8P_T1_AD3P_15

G15

IO_L8N_T1_AD3N_15

F15

IO_L9P_T1_DQS_AD11P_15

J15

IO_L9N_T1_DQS_AD11N_15

J16

IO_L10P_T1_AD4P_15

E15

IO_L10N_T1_AD4N_15

E16

IO_L11P_T1_SRCC_AD12P_15

G17

IO_L11N_T1_SRCC_AD12N_15

F18

IO_L12P_T1_MRCC_AD5P_15

F17

IO_L12N_T1_MRCC_AD5N_15

E17

IO_L13P_T2_MRCC_15

E18

IO_L13N_T2_MRCC_15

D18

IO_L14P_T2_SRCC_15

H17

IO_L14N_T2_SRCC_15

H18

IO_L15P_T2_DQS_15

D19

IO_L15N_T2_DQS_ADV_B_15

D20

IO_L16P_T2_A28_15

G19

IO_L16N_T2_A27_15

F20

IO_L17P_T2_A26_15

F19

IO_L17N_T2_A25_15

E20

IO_L18P_T2_A24_15

H19

IO_L18N_T2_A23_15

G20

IO_L19P_T3_A22_15

K20

IO_L19N_T3_A21_VREF_15

J20

IO_L20P_T3_A20_15

J18

IO_L20N_T3_A19_15

J19

IO_L21P_T3_DQS_15

L19

IO_L21N_T3_DQS_A18_15

L20

IO_L22P_T3_A17_15

K16

IO_L22N_T3_A16_15

K17

IO_L23P_T3_FOE_B_15

M17

IO_L23N_T3_FW E_B_15

L18

IO_L24P_T3_RS1_15

L17

IO_L24N_T3_RS0_15

K18

IO_25_15

M16

C0-CSn

R3006

NC/300R 1%

C0-A8

C1-DQ14

C1-A2

R3021

NC/300R 1%

C0-DQ13

C1-CSn

C0-ODT

C1-ODT

C0-A14

C1-BA0

C1-MCLKp

C1-DQM1

C1-RASn

C1-WEn

C1-MCLKn

C1-CKE

C1-A0

C1-DQS1p

C1-DQS1n

C1-DQ0

TP4016

1

C1-DQS0n

C1-DQS0p C1-A14

C1-CASn

C1-BA2

C1-DQM0

C0-DQ29

C0-DQ4

U3002

W631GG6MB-12

VDD_0

B2

NC_0

J1

VSS_0

A9

VSSQ_0

B1

UDQS#

B7

VDDQ_0

A1

DQU6

B8

VSSQ_1

B9

UDM

D3

UDQS

C7

VSSQ_2

D1

DQU7

A3

VDDQ_1

A8

DQU1

C3

VDDQ_2

C1

VDDQ_3

C9

DQU0

D7

VDDQ_4

D2

DQU4

A7

VSSQ_3

D8

DQU3

C2

DQU2

C8

VSSQ_4

E2

DQU5

A2

VDD_1

D9

NC_1

J9

VSS_1

B3

VSSQ_5

E8

LDQS#

G3

VDDQ_5

E9

DQL6

G2

VSSQ_6

F9

LDM

E7

LDQS

F3

VSSQ_7

G1

DQL7

H7

VDDQ_6

F1

DQL1

F7

VDDQ_7

H2

DQL0

E3

VDDQ_8

H9

DQL4

H3

VSSQ_8

G9

DQL3

F8

DQL2

F2

BA2

M3

DQL5

H8

VDD_5

N1

VREFDQ

H1

VSS_2

E1

VSS_5

J8

CK

J7

VDD_2

G7

CKE

K9

WE#

L3

RAS#

J3

CK#

K7

ODT

K1

RESET#

T2

BA0

M2

BA1

N8

CAS#

K3

CS#

L2

A10/AP

L7

A1

P7

A2

P3

A0

N3

VDD_3

K2

VSS_3

G8

A3

N2

A5

P2

A6

R8

A4

P8

A7

R2

A9

R3

A11

R7

A8

T8

VSS_4

J2

VDD_4

K8

A12/BC#

N7

NC_3

L9

ZQ

L8

NC_2

L1

VREFCA

M8

NC_4

M7

NC

T3

NC_6

T7

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VDD_6

N9

VDD_7

R1

VDD_8

R9

C1-DQ2

C0-RESETn

+1V5-FPGA

C0-BA1

+C0-VREF-U

TP4038

1

TP4039

1

TP4041

1

R3007

240R 1%

TP4040

1

C0-DQ20

TP3944

1

R3008

NC/300R 1%

C1-A11

C0-CSn

C0-ODT

C0-BA0

+VCCO34

C0-BA0

C0-DQ31

C0-DQ30

C0-DQM3

C0-RASn

C0-WEn

C0-MCLKn

C0-MCLKp

C0-CKE

C0-DQS3p

C0-DQS3n

+C1-VREF

C0-A0

TP4065

1

R3019

1K OHM 1%

C0-DQ16

C0-DQS2p C0-A14

R3018

1K OHM 1%

R3026

NC/4.7K 1/16W

+1V5-FPGA

C0-DQS2n

C3022

100NF 16V

TP3006

C0-BA2

C0-DQM2

C0-CASn

C3023

100NF 16V

+C1-VREF-M

C0-DQM0

C1-DQS0n

C1-DQS0p

C0-DQ3

C0-DQ2

C1-DQM0

C0-RASn

C0-DQ1

C0-DQ0

F

P

G

A

E

M

E

R

A

L

D

D

D

R

1

6

b

C0-DQM1

C0-DQ4

C0-DQ8

C0-DQM1

C0-DQ7

C0-DQ6

C0-DQ5

C0-MCLKn

C0-MCLKp

C0-DQ10

C0-DQ9

R3002

NC/100R 1/16W 1%

C0-DQS3n

TP4017

1

C1-DQ0

C0-MCLKp

C0-MCLKn

C0-DQ12

C0-DQ11

C0-DQS3p

C1-DQ7

C0-DQ13

C0-DQS0n

C0-DQS0p

SSC-SEL1

C1-A7

C0-DQ15

C0-DQ14

C0-WEn

C0-A6

C0-DQ16

TP3798

C0-DQM2

TP3961

1

+C1-VREF-M

R3017

1K OHM 1%

R3016

1K OHM 1%

TP3005

C3009

100NF 16V

+1V5-FPGA

C3008

100NF 16V

+C0-VREF-L

R3010

1K OHM 1%

R3009

1K OHM 1%

+1V5-FPGA

C3002

100NF 16V

TP3002

C3003

100NF 16V

TP4043

1

TP4042

1

TP4045

1

TP4044

1

R3004

1K OHM 1%

+C0-VREF-M

R3003

1K OHM 1%

C3000

100NF 16V

TP3001

C3001

100NF 16V

+1V5-FPGA

C0-CKE

L

a

y

o

u

t

:

- The 4 Cx-DQ../Cx-DQM/Cx-DQS groups can be swapped for a better layout.

- Within each Cx-DQ../Cx-DQM/Cx-DQS group,

the Cx-DQ.. pins can be swapped for a better layout.

(DQS pins have a fixed location in each group)

C0-DQ24

C1-DQM1

C0-DQM3

C1-DQ11

C1-DQ8

+C0-VREF-U

C0-DQ25

R3012

1K OHM 1%

R3011

1K OHM 1%

C3004

100NF 16V

TP3003

+1V5-FPGA

C3005

100NF 16V

C0-DQS1n

TP4066

1

C0-DQS1p

C0-DQS1n C0-DQS1p

TP3004

C1-DQS1n

C1-DQS1p

U3003

W631GG6MB-12

VDD_0

B2

NC_0

J1

VSS_0

A9

VSSQ_0

B1

UDQS#

B7

VDDQ_0

A1

DQU6

B8

VSSQ_1

B9

UDM

D3

UDQS

C7

VSSQ_2

D1

DQU7

A3

VDDQ_1

A8

DQU1

C3

VDDQ_2

C1

VDDQ_3

C9

DQU0

D7

VDDQ_4

D2

DQU4

A7

VSSQ_3

D8

DQU3

C2

DQU2

C8

VSSQ_4

E2

DQU5

A2

VDD_1

D9

NC_1

J9

VSS_1

B3

VSSQ_5

E8

LDQS#

G3

VDDQ_5

E9

DQL6

G2

VSSQ_6

F9

LDM

E7

LDQS

F3

VSSQ_7

G1

DQL7

H7

VDDQ_6

F1

DQL1

F7

VDDQ_7

H2

DQL0

E3

VDDQ_8

H9

DQL4

H3

VSSQ_8

G9

DQL3

F8

DQL2

F2

BA2

M3

DQL5

H8

VDD_5

N1

VREFDQ

H1

VSS_2

E1

VSS_5

J8

CK

J7

VDD_2

G7

CKE

K9

WE#

L3

RAS#

J3

CK#

K7

ODT

K1

RESET#

T2

BA0

M2

BA1

N8

CAS#

K3

CS#

L2

A10/AP

L7

A1

P7

A2

P3

A0

N3

VDD_3

K2

VSS_3

G8

A3

N2

A5

P2

A6

R8

A4

P8

A7

R2

A9

R3

A11

R7

A8

T8

VSS_4

J2

VDD_4

K8

A12/BC#

N7

NC_3

L9

ZQ

L8

NC_2

L1

VREFCA

M8

NC_4

M7

NC

T3

NC_6

T7

VSS_6

M1

VSS_7

M9

VSS_8

P1

VSS_9

P9

VSS_10

T1

VSS_11

T9

VDD_6

N9

VDD_7

R1

VDD_8

R9

C0-A9

C1-DQ15

C0-DDR-SYS-CLKp 8

C1-A3

C0-DDR-SYS-CLKp

PQ-CLK-SYS-SS

C0-A0

L

a

y

o

u

t

:

- The 2 Cx-DQ../Cx-DQM/Cx-DQS groups can be swapped for a better layout.

- Within each Cx-DQ../Cx-DQM/Cx-DQS group,

the Cx-DQ../Cx-DQM pins can be swapped for a better layout.

(DQS pins have a fixed location in each group)

PQ-CLK-SY S-SS 8

C0-DQ14

C0-DQ20

TP3936

1

F

P

G

A

E

M

E

R

A

L

D

D

D

R

3

2

b

C1-BA1

C1-BA2

C1-A14

C1-WEn

C1-CASn

C1-RASn

C1-BA0

C1-MCLKn

C1-MCLKp

+C0-VREF-M

C1-A0

+C0-VREF-M

C1-MCLKp

C0-DQ0

R3015

100R 1%

C1-MCLKn

TP4018

1

D

e

c

o

u

p

l

i

n

g

f

o

r

(

s

i

n

g

l

e

)

D

D

R

d

e

v

i

c

e

(FPGA decoupling on another sheet)

C0-DQ30

C0-DQ5

TP3962

1

C1-DQ3

C3029

100NF 16V

C3026

100NF 16V

C0-DQS0p

C0-DQS0n

C3025

100NF 16V

C3027

100NF 16V

C3030

100NF 16V

C3028

100NF 16V

C1-CKE

C1-ODT

+1V5-FPGA

C0-DQ21

TP4046

1

TP4048

1

TP4047

1

C0-CASn

TP4049

1

C1-A12

C3015

100NF 16V

C3018

100NF 16V

C3021

100NF 16V

C3010

22uF 6.3V

TP4067

1

C3007

100NF 16V

C0-DQM0

C3019

100NF 16V

C3006

100NF 16V

C3011

22uF 6.3V

C3012

100NF 16V

C3016

100NF 16V

C3013

100NF 16V

C0-DDR-SYS-CLKp

C3014

100NF 16V

C3017

100NF 16V

C3031

100NF 16V

C3032

100NF 16V

C3020

100NF 16V

C3033

100NF 16V

C3034

100NF 16V

C3035

100NF 16V

C3036

100NF 16V

C3037

100NF 16V

+1V5-FPGA

PQ-CLK-SYS-SS

C0-BA2

C1-CSn

C0-DQS2p

C0-DQS2n

C1-DQ8

TP4019

1

C1-A8

C0-A7

C3024

22uF 6.3V

L

a

y

o

u

t

:

P

l

a

c

e

a

1

0

0

N

o

n

e

a

c

h

D

D

R

p

i

n

TP4050

1

C0-A10

C1-A4

C0-DQ21

C0-DQ15

U3700-5

XC7K160T-2FBG676I4397

IO_0_16

J8

IO_L1P_T0_16

H9

IO_L1N_T0_16

H8

IO_L2P_T0_16

G10

IO_L2N_T0_16

G9

IO_L3P_T0_DQS_16

J13

IO_L3N_T0_DQS_16

H13

IO_L4P_T0_16

J11

IO_L4N_T0_16

J10

IO_L5P_T0_16

H14

IO_L5N_T0_16

G14

IO_L6P_T0_16

H12

IO_L6N_T0_VREF _16

H11

IO_L7P_T1_16

F9

IO_L7N_T1_16

F8

IO_L8P_T1_16

D9

IO_L8N_T1_16

D8

IO_L9P_T1_DQS_16

A9

IO_L9N_T1_DQS_16

A8

IO_L10P_T1_16

C9

IO_L10N_T1_16

B9

IO_L11P_T1_SRCC_16

G11

IO_L11N_T1_SRCC_16

F10

IO_L12P_T1_MRCC_16

E10

IO_L12N_T1_MRCC_16

D10

IO_L13P_T2_MRCC_16

C12

IO_L13N_T2_MRCC_16

C11

IO_L14P_T2_SRCC_16

E11

IO_L14N_T2_SRCC_16

D11

IO_L15P_T2_DQS_16

F14

IO_L15N_T2_DQS_16

F13

IO_L16P_T2_16

G12

IO_L16N_T2_16

F12

IO_L17P_T2_16

D14

IO_L17N_T2_16

D13

IO_L18P_T2_16

E13

IO_L18N_T2_16

E12

IO_L19P_T3_16

C14

IO_L19N_T3_VREF_16

C13

IO_L20P_T3_16

B12

IO_L20N_T3_16

B11

IO_L21P_T3_DQS_16

B14

IO_L21N_T3_DQS_16

A14

IO_L22P_T3_16

B10

IO_L22N_T3_16

A10

IO_L23P_T3_16

B15

IO_L23N_T3_16

A15

IO_L24P_T3_16

A13

IO_L24N_T3_16

A12

IO_25_16

J14

TP4020

1

C0-DQ31

C0-DQ6

C0-A1

C1-DQ4

C0-DQ22

TP4051

1

C1-A13

C1-DQ9

C1-RESETn

C1-DQ12

C1-A9

C0-A8

TP4021

1

TP3953

1

TP4052

1

+1V5-FPGA

C0-A11

C1-A5

C0-DQ22

C0-A2

C0-DQ7

TP4022

1

C1-DQ5

TP3954

1

C0-DQ23

TP4053

1

L

a

y

o

u

t

:

P

l

a

c

e

a

t

D

D

R

p

i

n

s

SSC-SEL0

C1-DQ10

C1-DQ13

C1-A10

C0-A9

TP4023

1

C1-A1C1-DQ1

TP4054

1

C0-A12

C1-A6

C0-A3

C0-DQ8

TP4024

1

C1-DQ6

C0-DQ24

V

R

E

F

v

o

l

t

a

g

e

d

i

v

i

d

e

r

s

TP4055

1

Loading...

Loading...