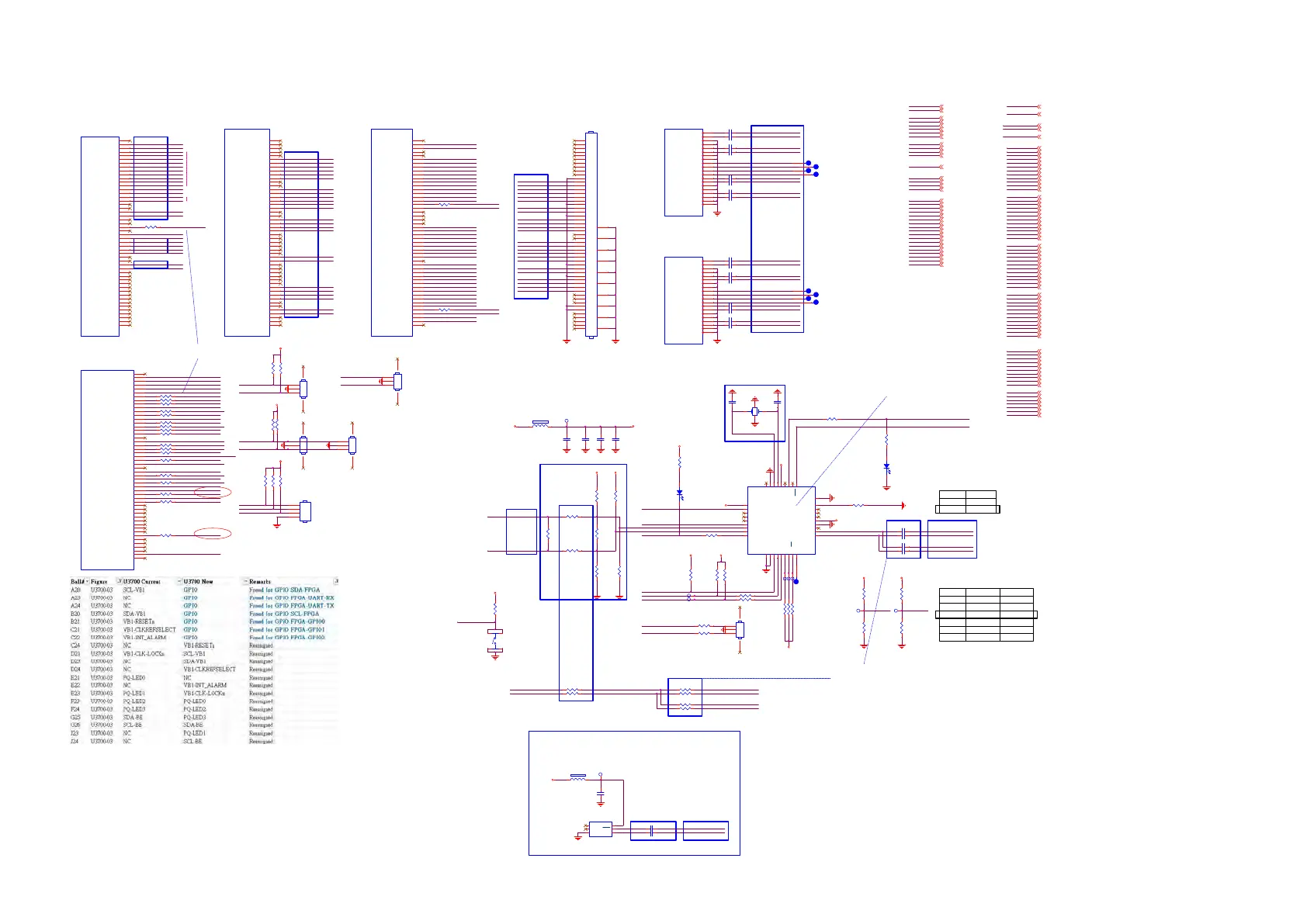

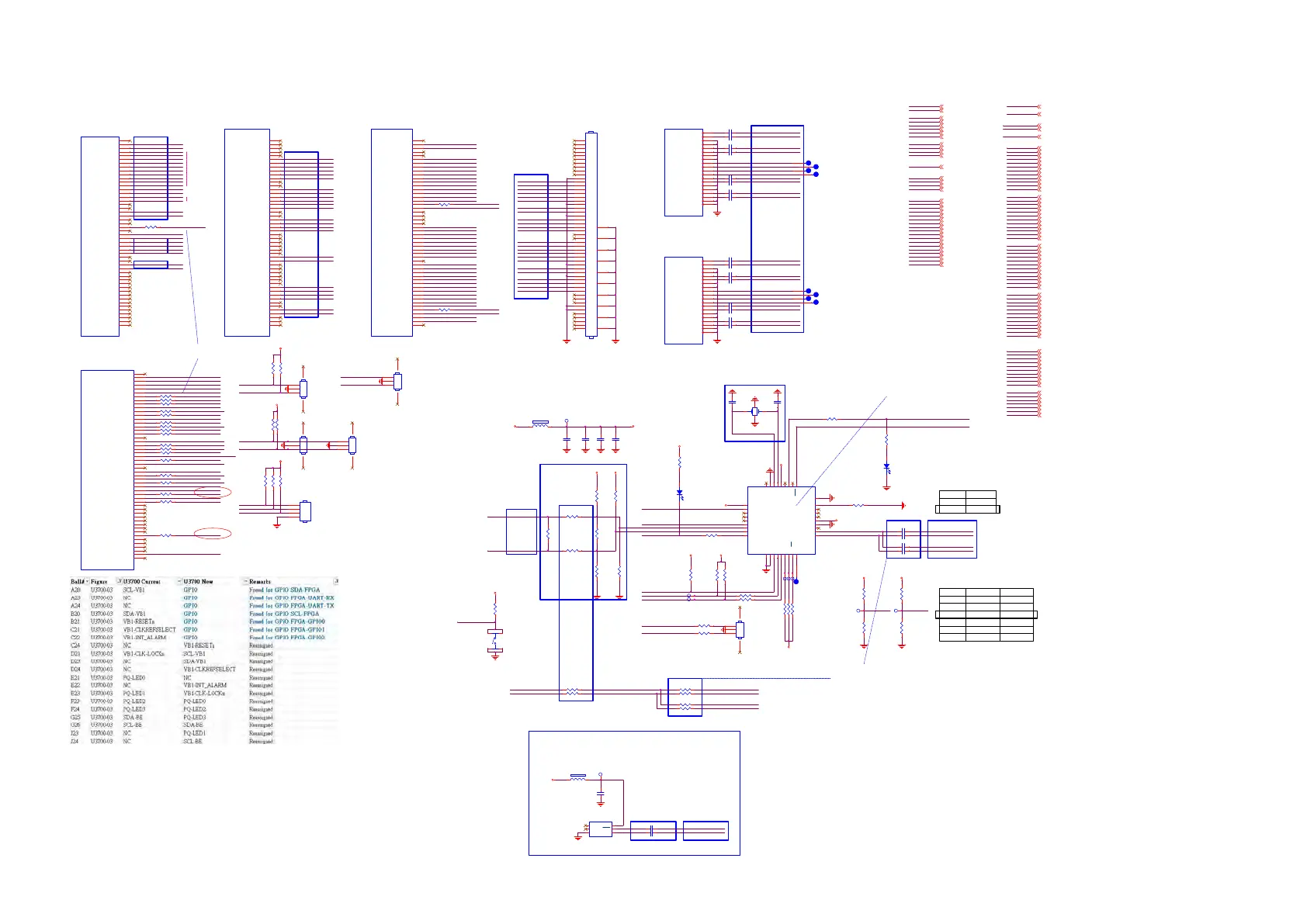

9-5-8 FPGAc_GPIO

PQ-VB1-TX6n

PQ-VB1-TX7n

PQ-VB1-TX6p

PQ-VB1-TX7p

TP3933

PQ-LED0

SDA-VB1

PQ-RESET-SYSn

L

a

y

o

u

t

:

- capacitors towards IC (4 upper ones) on top layer

- resistors (4 at the left) on bottom layer,

just underneath the 4 capacitors

PQ-LED1

TP3935

TP3918

1

PQ-CLK-SYS

R3907 0.05R

PQ-LED3

PQ-LED2

3

7

.

.

4

1

M

h

z

f

u

n

d

a

m

e

n

t

a

l

L

:

L

-

H

:

H

n

o

c

l

o

c

k

C3913 100NF 16V

LED3900

NC/GPTS06033GC1-PB

12

TP3924

C3912 100NF 16V

R3903

NC/470R

R3912 NC/0R05 OHM

R3928 NC/1K 1/16W

FB3900

NC/ 120R

1 2

C3900

NC/ 12pF 50V

X3900

NC/ 114.285MHz

1

2 4

3

C3901

NC/12pF 50V

VB1-CLKREF CLEAN0p

VB1-CLKREF CLEAN1p

VB1-CLKREF CLEAN0n

VB1-RESETn

C3907 NC/ 100N16V

R3929 NC/1K 1/16W

+3V3-VB1

+3V3

R3930 NC/1K 1/16W

C3924 100NF 16V

C3925 100NF 16V

C3909 NC/ 100NF 16V

+3V3-VB1

RATE0

RATE1

U3700-8

XC7K160T-2FBG676I4397

MGTXTXP3_115

H2

MGTXTXN3_115

H1

MGTXRXP3_115

J4

MGTXRXN3_115

J3

MGTXTXP2_115

K2

MGTXTXN2_115

K1

MGTXRXP2_115

L4

MGTXRXN2_115

L3

MGTREFCLK1P_115

K6

MGTREFCLK1N_115

K5

MGTREFCLK0P_115

H6

MGTREFCLK0N_115

H5

MGTXTXP1_115

M2

MGTXTXN1_115

M1

MGTXRXP1_115

N4

MGTXRXN1_115

N3

MGTXTXP0_115

P2

MGTXTXN0_115

P1

MGTXRXP0_115

R4

MGTXRXN0_115

R3

U3901

NC/SI5319-C -GM

RST

1

NC

2

INT _CB

3

NC

4

VDD

5

XA

6

XB

7

GND

8

NC

9

VDD

10

RATE0

11

NC

12

NC

13

NC

14

RATE1

15

CKIN1+

16

CKIN1-

17

LOL

18

GND

19

GND

20

CS

21

SCL

22

SDA_SDO

23

A0

24

A1

25

A2_SS

26

SDI

27

CKOUT+

28

CKOUT-

29

NC

30

GND

31

VDD

32

NC

33

NC

34

NC

35

CMODE

36

E-PAD

37

C3906 NC/ 100N16V

S

P

I

+3V3-VB1

RATE1

R3924

NC/ 1K 1/16W

R3916

NC/ 100OHM1/ 16W

K7-D03

R3910

NC/ 82R 1/16W 5%

K7-FCS-B

K7-D00

K7-D01

K7-D02

R3920

NC/82R 1/16W 5%

R3921

NC/120 OHM 1/16W

+3V3-VB1

R3911

NC/ 120 OHM 1/16W

+3V3-VB1

R3917

NC/ 100 OHM

I

2

C

R3915

NC/0R05 OHM

R3919

NC/0R05 OHM

L

a

y

o

u

t

:

Resistors next to eachother (near FPGA)

Keep signal as much as possible on TOP layer

Shield signal with GND-trace

S

E

L

E

C

T

I

O

N

+3V3

R3901 NC /10 OHM

C3902

NC/ 4.7UF 10% 10V

+3V3-VB1

R3931

NC/ 1K 1/16W

R3918NC/10 OHM

C

M

O

D

E

RATE0

R3926

NC/ 1K 1/16W

+3V3-VB1

R3932

NC/ 1K 1/16W

L

O

W

H

I

G

H

e

x

t

e

r

n

a

l

c

l

o

c

k

T

Y

P

E

3

r

d

o

v

e

r

t

o

n

e

R

A

T

E

[

1

:

0

]

M

:

M

M

:

H

VB1-CLKREFn

VB1-CLKREFp

R3935 NC/0R05 OHM

L

a

y

o

u

t

:

100Ohm diff + TOP layer

R3933 NC/0R05 OHM

1

0

9

.

.

1

2

5

M

h

z

R

A

N

G

E

1

1

4

M

h

z

E

M

E

R

A

L

D

V

x

1

T

x

C

L

O

C

K

-

C

L

E

A

N

E

R

(debug only)

+3V3

R3936 NC /0R05 OHM

VB1-INT_ALARM

R3934 NC /0R05 OHM

D

B

G

D

B

G

VB1-CLKREFCLEAN0p

VB1-CLKREFCLEAN0n

e

x

t

e

r

n

a

l

c

l

o

c

k

R3927 NC /10 OHM

PQ-TX1-CLKn

5

5

.

.

6

1

M

h

z

M

:

L

L

:

M

PQ-TX1-CLKp

R3925 NC /10 OHM

R3937 NC /0R05 OHM

R3938 NC /0R05 OHM

VB1-CLKREFCLEAN1p

VB1-CLKREFCLEAN1n

D

B

G

R3906

NC/ 470R

U3700-10

XC7K160T-2FBG676I4397

MGTXTXP3_116

A4

MGTXTXN3_116

A3

MGTXRXP3_116

B6

MGTXRXN3_116

B5

MGTXTXP2_116

B2

MGTXTXN2_116

B1

MGTXRXP2_116

C4

MGTXRXN2_116

C3

MGTREFCLK1P_116

F6

MGTREFCLK1N_116

F5

MGTREFCLK0P_116

D6

MGTREFCLK0N_116

D5

MGTXTXP1_116

D2

MGTXTXN1_116

D1

MGTXRXP1_116

E4

MGTXRXN1_116

E3

MGTXTXP0_116

F2

MGTXTXN0_116

F1

MGTXRXP0_116

G4

MGTXRXN0_116

G3

3

7

.

.

4

1

M

h

z

e

x

t

e

r

n

a

l

c

l

o

c

k

D

B

G

PQ-VB1-TX1p

PQ-VB1-TX0p

+3V3

PQ-TX13n

PQ-TX13p

FPGA-UART-TX

SDA-FPGA

SCL-FPGA

FPGA-UART-RX

FPGA-GPIO0

R3952 0.05R

FPGA-GPIO0

R3960

4.7K

U3700-3

XC7K160T-2FBG676I4397

IO_0_14

K21

IO_L1P_T0_D00_MOSI_14

B24

IO_L1N_T0_D01_DIN_14

A25

IO_L2P_T0_D02_14

B22

IO_L2N_T0_D03_14

A22

IO_L3P_T0_DQS_PUDC _B_14

B25

IO_L3N_T0_DQS_EMCCLK_14

B26

IO_L4P_T0_D04_14

A23

IO_L4N_T0_D05_14

A24

IO_L5P_T0_D06_14

D26

IO_L5N_T0_D07_14

C26

IO_L6P_T0_FCS_B_14

C23

IO_L6N_T0_D08_VREF _14

C24

IO_L7P_T1_D09_14

D21

IO_L7N_T1_D10_14

C22

IO_L8P_T1_D11_14

B20

IO_L8N_T1_D12_14

A20

IO_L9P_T1_DQS_14

E21

IO_L9N_T1_DQS_D13_14

E22

IO_L10P_T1_D14_14

C21

IO_L10N_T1_D15_14

B21

IO_L11P_T1_SRCC_14

D23

IO_L11N_T1_SRCC_14

D24

IO_L12P_T1_MRCC_14

F22

IO_L12N_T1_MRCC_14

E23

IO_L13P_T2_MRCC_14

G22

IO_L13N_T2_MRCC_14

F23

IO_L14P_T2_SRCC_14

G24

IO_L14N_T2_SRCC_14

F24

IO_L15P_T2_DQS_RDW R_B_14

E25

IO_L15N_T2_DQS_DOU T_CSO_B_14

D25

IO_L16P_T2_CSI_B_14

G25

IO_L16N_T2_A15_D31_14

G26

IO_L17P_T2_A14_D30_14

F25

IO_L17N_T2_A13_D29_14

E26

IO_L18P_T2_A12_D28_14

J26

IO_L18N_T2_A11_D27_14

H26

IO_L19P_T3_A10_D26_14

H21

IO_L19N_T3_A09_D25_VREF_14

G21

IO_L20P_T3_A08_D24_14

H23

IO_L20N_T3_A07_D23_14

H24

IO_L21P_T3_DQS_14

J21

IO_L21N_T3_DQS_A06_D22_14

H22

IO_L22P_T3_A05_D21_14

J24

IO_L22N_T3_A04_D20_14

J25

IO_L23P_T3_A03_D19_14

L22

IO_L23N_T3_A02_D18_14

K22

IO_L24P_T3_A01_D17_14

K23

IO_L24N_T3_A00_D16_14

J23

IO_25_14

L23

C3914 100NF 16V

C3915 100NF 16V

R3909 NC/0.05R

HS1-PRBS

HS0-DGLOCK

HS1-DGLOCK

HS0-PRBS

HS-MON-EN

HS0-BETOUT

HS-BET-SEL1

HS-BET-SEL0

R3943 100 OHM

HS1-BETOUT

R3944 100 OHM

HS-MODE2

HS-MODE0

HS-MODE1

HS0-OE

HS1-OE

HS0-BET-LAT

HS1-BET-LAT

HS-RS

K7-PUDC -B

R

e

v

e

r

s

e

d

L

a

y

o

u

t

:

Place this IC in the area above the FPGA

(there will not be that much in that area)

CN1900

CONN 3P

1

2

3

45

SCL-VB1

SDA-VB1

R394147 OHM

A

d

d

t

e

x

t

R394247 OHM

I2C-VB1

R3949 0.05R

R3951 0.05R

PQ-TX0-CLKn

PQ-TX0-CLKp

TP3963

R3939

NC/ 1K 1/16W

VB1-FIXEDCLKREF0p

VB1-FIXEDCLKREF0n

CN1902

CONN 3P

1

2

3

45

R3958

4.7K

C3910 100NF 16V

CN1903

CONN 3P

1

2

3

45

R3953

4.7K

VB1-FIXEDCLKR EF0p

VB1-FIXEDCLKR EF0n

Layout :

If possible, place on TOP layer

Close to IC

GND trace around circuit

R3959

4.7K

FPGA-SPI-MISO

R3961 0.05R

CN1901

CONN

1

2

3

4

R3954

4.7K

PQ-TX02p

PQ-TX02n

Layout:

LVDS pairs are 100 Ohm differential

GND-trace + GND-vias (every+/-5mm)..

..around complete bus

VB1-CLKREF n

VB1-CLKREF p

SCL-FPGA

CN1904

CONN 3P

1

2

3

45

Layout:

Vx1 pairs are 100 Ohm differential

GND-trace + GND-vias (every+/-5mm) around complete bus

FPGA-GPIO2

TP3904

BEAD_PROBE_5X25_X_SML-OA

1

TP3905

BEAD_PROBE_5X25_X_SML-OA

1

PQ-TX11p

PQ-TX11n

VB1-CLKREFSELECT

R3955

4.7K

R3956

4.7K

C3916 100NF 16V

C3917 100NF 16V

+3V3

HS0-DGLOC K 6

HS1-OE 6

HS0-OE 6

HS-MODE0 6

HS-MODE2 6

HS-MODE1 6

HS1-DGLOC K 6

HS-TX21p 6

HS-TX21n 6

HS-TX2-CLKp 6

HS-TX2-CLKn 6

HS-TX24p 6

HS-TX24n 6

HS-TX22p 6

HS-TX22n 6

HS-TX23p 6

HS-TX23n 6

HS-TX20p 6

HS-TX20n 6

+3V3

HS-TX02p 6

HS-TX02n 6

HS-TX01p 6

HS-TX0-CLKp 6

HS-TX01n 6

HS-TX00p 6

HS-TX00n 6

HS-TX0-CLKn 6

HS-TX12p 6

HS-TX04p 6

HS-TX04n 6

HS-TX03p 6

HS-TX10p 6

HS-TX03n 6

HS-TX1-CLKp 6

HS-TX1-CLKn 6

HS-TX13p 6

HS-TX12n 6

HS-TX11p 6

HS-TX11n 6

HS-TX13n 6

HS-TX10n 6

HS-TX14p 6

HS-TX14n 6

HS-TX3-CLKp 6

HS-TX3-CLKn 6

HS-TX32p 6

HS-MON-EN 6

HS-TX30p 6

HS-TX31p 6

HS-TX31n 6

HS-TX32n 6

HS-RS 6

HS-TX30n 6

HS-TX33n

HS-TX33p

SW3800

1 2

3 4

HS-TX2-CLKp

HS-TX34n

HS-TX20p

HS-TX3-CLKp

HS-TX3-CLKn

HS-TX31n

DBG

HS-TX32p

HS-TX31p

HS-TX22p

HS-TX22n

HS-TX2-CLKn

HS-TX24n

HS-TX34p

HS-TX21p

HS-TX20n

HS-TX32n

R3950 0.05R

HS-TX34p 6

HS-TX1-CLKn

HS-TX23p

HS-TX23n

HS-TX24p

HS-TX13p

HS-TX13n

HS-TX0-CLKp

HS-TX21n

HS-TX30p

HS-TX30n

PQ-TX12n

PQ-TX12p

X3901

133.333MHz

OE

1

NC

2

GND

3

OUT

4

OUT

5

VDD

6

HS-TX02n

HS-TX02p

HS-TX11n

HS-TX11p

HS-TX1-CLKp

HS-TX12n

HS-TX00n

HS-TX00p

HS-TX14n

HS-TX0-CLKn

HS-TX04n

HS-TX04p

HS-TX03n

HS-TX03p

HS-TX10n

HS-TX12p

HS-TX34n 6

HS-TX10p

HS-TX01n

HS-TX01p

HS-TX14p

HS-TX33p 6

HS-TX33n 6

HS0-PRBS

HS-MON-EN

HS-BET-SEL1

HS-BET-SEL0

HS0-BETOUT

HS1-BETOUT

HS-MODE2

HS1-PRBS

HS-MODE0

HS1-BET-LAT

HS0-BET-LAT

HS1-OE

HS0-OE

HS-RS

HS1-DGLOCK

HS-MODE1

HS1-BETOUT 6

HS0-BETOUT 6

HS0-DGLOCK

HS1-BET-LAT 6

HS0-BET-LAT 6

HS0-PRBS 6

HS1-PRBS 6

SOC-SDA-FPGA 6,12

SOC-SCL-FPGA 6,12

HS-BET-SEL1 6

HS-BET-SEL0 6

SOC-SCL-FPGA

SOC-SDA-FPGA

SDA-FPGA

Upda ted o n 2019 /7/29

Upda ted on 2019/7/29

VB1-CLK-LOCKn

FPGA-UART-TX

+3V3

Layout :

LED on TOP layer (not underneath heatsink)

PQ-TX00p

PQ-TX00n

EMERALD Vx1 133.333MHZ

REFERENCE CLOCK

DB G

U3700-28

XC7K160T-2FBG676I4397

IO_L22P_T3_12

AE23

IO_L20P_T3_12

AF24

IO_0_12

U21

IO_L24P_T3_12

AE22

IO_L1P_T0_12

U22

IO_L1N_T0_12

V22

IO_L2P_T0_12

U24

IO_L2N_T0_12

U25

IO_L3P_T0_DQS_12

V23

IO_L21P_T3_DQS_12

AD26

IO_L3N_T0_DQS_12

V24

IO_L23P_T3_12

AD25

IO_L4P_T0_12

U26

IO_25_12

Y2 0

IO_L4N_T0_12

V26

IO_L5P_T0_12

W25

IO_L5N_T0_12

W26

IO_L6P_T0_12

V21

IO_L6N_T0_VREF_12

W21

IO_L7P_T1_12

AA25

IO_L7N_T1_12

AB25

IO_L8P_T1_12

W23

IO_L8N_T1_12

W24

IO_L20N_T3_12

AF25

IO_L9P_T1_DQS_12

AB26

IO_L21N_T3_DQS_12

AE26

IO_L9N_T1_DQS_12

AC26

IO_L22N_T3_12

AF23

IO_L10P_T1_12

Y2 5

IO_L23N_T3_12

AE25

IO_L10N_T1_12

Y2 6

IO_L24N_T3_12

AF22

IO_L11N_T1_SRCC_12

AB24

IO_L12P_T1_MRC C_12

Y2 3

IO_L12N_T1_MRCC_12

AA24

IO_L13P_T2_MRC C_12

Y2 2

IO_L13N_T2_MRCC_12

AA22

IO_L14P_T2_SRCC_12

AC23

IO_L14N_T2_SRCC_12

AC24

IO_L15P_T2_DQS_12

W20

IO_L15N_T2_DQS_12

Y2 1

IO_L16P_T2_12

AD23

IO_L16N_T2_12

AD24

IO_L17P_T2_12

AB22

IO_L17N_T2_12

AC22

IO_L18P_T2_12

AB21

IO_L18N_T2_12

AC21

IO_L19P_T3_12

AD21

IO_L19N_T3_VREF_12

AE21

IO_L11P_T1_SRCC_12

AA23

Reversed

DBG

C3927 100NF 16V

C3928 100NF 16V

FPGA-GPIO1

K7-PUDC -B 8

K7-PUDC -B

R

e

v

e

r

s

e

d

C0-DDR-SY S-CLKn 8, 10

C0-DDR-SY S-CLKn

VB1-CLKREFn

VB1-CLKREFp

R3908 0.05R

L

a

y

o

u

t

:

Place close to X3901

PQ-TX14p

PQ-TX14n

Reversed

FPGA-GPIO2

PQ-TX04n

PQ-RESET-SYSn

PQ-TX04p

DBG

HS-TX33p

HS-TX20p

HS-TX3-CLKp

HS-TX3-CLKn

HS-TX31n

HS-TX33n

HS-TX31p

HS-TX22p

HS-TX22n

HS-TX2-CLKn

HS-TX2-CLKp

HS-TX34n

HS-TX34p

HS-TX21p

HS-TX20n

HS-TX32n

HS-TX32p

HS-TX1-CLKn

HS-TX23p

HS-TX23n

HS-TX24p

HS-TX24n

HS-TX13p

HS-TX13n

HS-TX0-CLKp

HS-TX21n

HS-TX30p

HS-TX30n

R3947 10 OHM

HS-TX02n

HS-TX02p

HS-TX11n

HS-TX11p

HS-TX1-CLKp

HS-TX12n

HS-TX00n

HS-TX00p

HS-TX14n

HS-TX0-CLKn

HS-TX04n

HS-TX04p

HS-TX03n

HS-TX03p

HS-TX10n

HS-TX12p

HS-TX10p

HS-TX01n

HS-TX01p

HS-TX14p

R3946 10 OHM

DBG

C3918 100NF 16V

C3919 100NF 16V

FPGA-SPI-CS

R3945 0.05R

PQ-TX03p

PQ-TX03n

U3700-29

XC7K160T-2FBG676I4397

IO_L5P_T0_32

AF19

IO_L21N_T3_DQS_32

W19

IO_L17N_T2_32

AD19

IO_L1P_T0_32

AE17

IO_L3P_T0_DQS_32

AE18

IO_L7P_T1_32

AA14

IO_L19N_T3_VREF_32

Y18

IO_L23N_T3_32

V19

IO_L2P_T0_32

AF14

IO_L4P_T0_32

AD15

IO_L6P_T0_32

AD16

IO_25_VRP_32

W13

IO_L18N_T2_32

AB20

IO_L20N_T3_32

V17

IO_L22N_T3_32

W16

IO_L24N_T3_32

W14

IO_L8P_T1_32

AC14

IO_0_VRN_32

V13

IO_L8N_T1_32

AD14

IO_L1N_T0_32

AF17

IO_L9N_T1_DQS_32

Y16

IO_L2N_T0_32

AF15

IO_L10N_T1_32

AB15

IO_L3N_T0_DQS_32

AF18

IO_L11N_T1_SRCC _32

AA18

IO_L4N_T0_32

AE15

IO_L12N_T1_MRCC_32

AC16

IO_L5N_T0_32

AF20

IO_L13N_T2_MRCC_32

AD18

IO_L6N_T0_VREF_32

AE16

IO_L14N_T2_SRCC _32

AC17

IO_L7N_T1_32

AA15

IO_L15N_T2_DQS_32

AE20

IO_L16N_T2_32

AA20

IO_L9P_T1_DQS_32

Y15

IO_L10P_T1_32

AB14

IO_L11P_T1_SRCC_32

AA17

IO_L12P_T1_MRCC _32

AB16

IO_L13P_T2_MRCC _32

AC18

IO_L14P_T2_SRCC_32

AB17

IO_L15P_T2_DQS_32

AD20

IO_L16P_T2_32

AA19

IO_L17P_T2_32

AC19

IO_L18P_T2_32

AB19

IO_L19P_T3_32

Y17

IO_L20P_T3_32

V16

IO_L21P_T3_DQS_32

W18

IO_L22P_T3_32

W15

IO_L23P_T3_32

V18

IO_L24P_T3_32

V14

Reversed

FPGA-SPI-MISO

Reversed

FPGA-SPI-CS 6

FPGA-SPI-MISO 6

FPGA-SPI-MOSI 6

FPGA-SPI-CLK 6

FPGA-SPI-CLK

FPGA-SPI-MOSI

FPGA-SPI-CS

C3920 100NF 16V

C3921 100NF 16V

PQ-CLK-SYS 8

PQ-CLK-SYS

R3957

4.7K

LED3901

NC/ GPTS06033GC1-PB

12

Layout:

100Ohm diff + TOP layer

Keep traces short

PQ-TX10p

PQ-TX10n

H

S

-

L

V

D

S

[

3

:

2

]

+3V3

R3948 0.05R

C3911 100NF 16V

FPGA-GPIO1

R3940 10 OHM

C3926

100NF 16V

HS-LVDS[1:0]

R3913 10 OHM

TP3919

1

SOC-SD A-FPGA

R3923

4.7K

PQ-VB1-TX1p 12

C3904

NC/0.22UF

PQ-VB1-TX1n 12

PQ-LED0 8

PQ-VB1-TX0n 12

PQ-VB1-TX0p 12

C3905

NC/ 0.22UF

PQ-VB1-TX2n 12

PQ-VB1-TX2p 12

C3903

NC/0.22UF

SOC-SC L-F PGA

R3914 10 OHM

PQ-VB1-TX3n 12

PQ-VB1-TX4p 12

PQ-VB1-TX6n 12

PQ-RX-LOCKn 6

PQ-VB1-TX3p 12

PQ-VB1-TX4n 12

PQ-VB1-TX7n 12

PQ-VB1-TX5n 12

PQ-VB1-TX5p 12

PQ-VB1-TX2n

PQ-VB1-TX6p 12

PQ-VB1-TX7p

PQ-VB1-TX3p

PQ-VB1-TX5p

PQ-VB1-TX4p

PQ-VB1-TX5n

PQ-VB1-TX4n

PQ-VB1-TX1p

PQ-VB1-TX7n

PQ-VB1-TX3n

PQ-VB1-TX6p

PQ-VB1-TX1n

PQ-VB1-TX0p

VB1-RESETn

PQ-VB1-TX6n

PQ-VB1-TX2p

PQ-VB1-TX0n

PQ-RX-LOCKn

PQ-VB1-TX7p 12

Layout:

100Ohm diff + TOP layer

PQ-HTPDn 8,12

PQ-LOCKn 8,12

PQ-HTPDn

PQ-LED2 8

PQ-LED1 8

K7-FCS-B 6,8

PQ-LOCKn

PQ-RESET-SYSn 8

PQ-LED3 8

K7-D01 6,8

K7-D00 6,8

K7-D00

PQ-RESET-SYSn

K7-D03 8

K7-D02 8

PQ-LED3

PQ-LED2

K7-D03

K7-D01

VB1-CLKREFSELECT

PQ-LED1

PQ-LED0

K7-FCS-B

K7-D02

C0-DDR-SY S-CLKp

PQ-CLK-SYS-SS

R3902 10 OHM

FPGA EMERALD Vx1 Rx/Tx

+3V3-VB1

VB1-CLK-LOCKn

VB1-INT_ALARM

U3700-2

XC7K160T-2FBG676I4397

IO_0_13

N16

IO_L1P_T0_13

K25

IO_L1N_T0_13

K26

IO_L2P_T0_13

R26

IO_L2N_T0_13

P26

IO_L3P_T0_DQS_13

M25

IO_L3N_T0_DQS_13

L25

IO_L4P_T0_13

P24

IO_L4N_T0_13

N24

IO_L5P_T0_13

N26

IO_L5N_T0_13

M26

IO_L6P_T0_13

R25

IO_L6N_T0_VREF_13

P25

IO_L7P_T1_13

N19

IO_L7N_T1_13

M20

IO_L8P_T1_13

M24

IO_L8N_T1_13

L24

IO_L9P_T1_DQS_13

P19

IO_L9N_T1_DQS_13

P20

IO_L10P_T1_13

M21

IO_L10N_T1_13

M22

IO_L11P_T1_SRCC_13

P23

IO_L11N_T1_SRCC _13

N23

IO_L12P_T1_MRCC _13

N21

IO_L12N_T1_MRCC_13

N22

IO_L13P_T2_MRCC _13

R21

IO_L13N_T2_MRCC_13

P21

IO_L14P_T2_SRCC_13

R22

IO_L14N_T2_SRCC _13

R23

IO_L15P_T2_DQS_13

T24

IO_L15N_T2_DQS_13

T25

IO_L16P_T2_13

T20

IO_L16N_T2_13

R20

IO_L17P_T2_13

T22

IO_L17N_T2_13

T23

IO_L18P_T2_13

U19

IO_L18N_T2_13

U20

IO_L19P_T3_13

T18

IO_L19N_T3_VREF_13

T19

IO_L20P_T3_13

P16

IO_L20N_T3_13

N17

IO_L21P_T3_DQS_13

R16

IO_L21N_T3_DQS_13

R17

IO_L22P_T3_13

N18

IO_L22N_T3_13

M19

IO_L23P_T3_13

U17

IO_L23N_T3_13

T17

IO_L24P_T3_13

R18

IO_L24N_T3_13

P18

IO_25_13

U16

PQ-CLK-SYS

PQ-TX01n

PQ-TX01p

Layout:

LVDS pairs are 100 Ohm differential

GND-trace + GND-vias (every+/-5mm)..

..around complete bus

EM ERALD Vx 1 Tx CLOCK-CLEAN ER BYPASS (default)

(debug only)

R3922

4.7K

TP3917

BEAD_PROBE_5X25_X_SML-OA

1

TP3916

BEAD_PROBE_5X25_X_SML-OA

1

VB1-CLKREFCLEAN1p

TP3906

BEAD_PROBE_5X25_X_SML-OA

1

VB1-CLKREFCLEAN0p

TP3907

BEAD_PROBE_5X25_X_SML-OA

1

PQ-TX03p

PQ-TX03n

PQ-TX04p

PQ-TX04n

PQ-TX01n

PQ-TX02p

PQ-TX02n

PQ-TX0-CLKp

PQ-TX0-CLKn

PQ-TX13n

PQ-TX13p

PQ-TX1-CLKn

PQ-TX00p

PQ-TX00n

PQ-TX01p

PQ-TX11n

PQ-TX11p

PQ-TX10n

PQ-TX14n

PQ-TX14p

C0-DDR-SY S-CLKp 8, 10

PQ-TX10p

PQ-TX1-CLKp

PQ-TX12n

PQ-TX12p

R3905 10 OHM

+3V3

SCL-VB1

R3900 0.05R

C3923 100NF 16V

C3922 100NF 16V

R3904 10 OHM

SDA-VB1

VX1-RX CONTROL

LVDS TX (DEBUG)

TP3928

TP3929

+3V3

PQ-RX-LOCKn

PQ-CLK-SYS-SS 8,10

VB1-CLKREF CLEAN1n

C3908 NC/ 100NF 16V

TP3930

LVDS pairs are 100 Ohm differential

GND-trace + GND-vias (every+/-5mm)..

..around complete bus

PQ-LOCKn

PQ-HTPDn

SCL-VB1

FPGA-UART-RX

Layout:

- resistors towards IC (2 upper ones) on top layer

- resistors not towards (2 lower ones) on bottom layer,

just underneath the other 2

CN1031

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

TP3931

1

Layout:

place close to IC (SI5319)

TP3934

C

N

1

0

3

1

E

M

E

R

A

L

D

LVDS TX (DEBUG)

VB1-CLKREFCLEAN0n

FPGA-SPI-MOSI

CN1905

1

2

3

45

TP3932

SOC-SCL-FPGA

VB1-CLKREFCLEAN1n

Add text

I2C-FPGA

SOC-SDA-FPGA

PQ-VB1-TX0n

PQ-VB1-TX1n

FPGA-SPI-CLK

PQ-VB1-TX2n

PQ-VB1-TX3p

PQ-VB1-TX3n

PQ-VB1-TX2p

FB3901

120R

1 2

PQ-VB1-TX5p

PQ-VB1-TX4n

PQ-VB1-TX4p

PQ-VB1-TX5n

Loading...

Loading...