Technical Specifications, Connections, and Chassis Overview

EN 14 SDI PDP1.

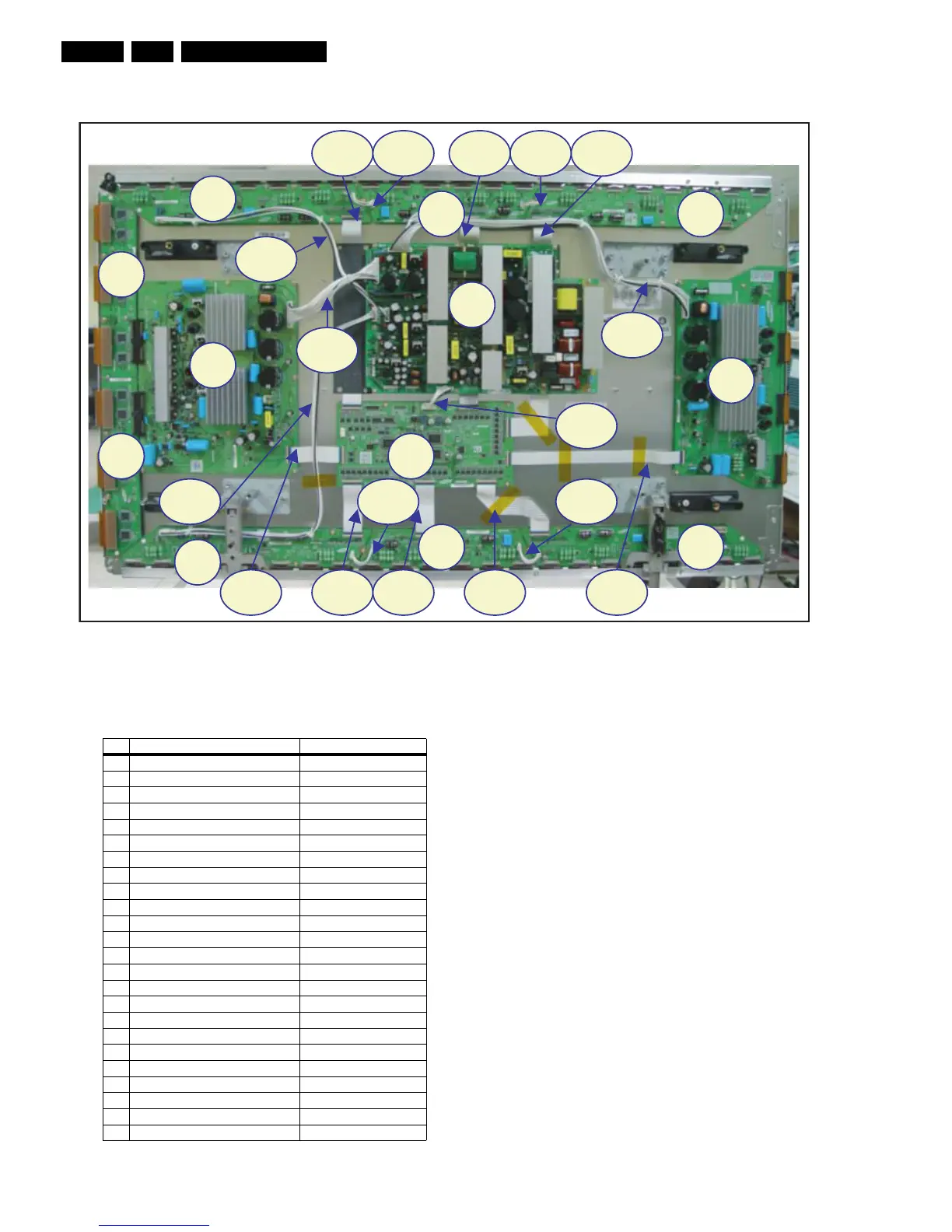

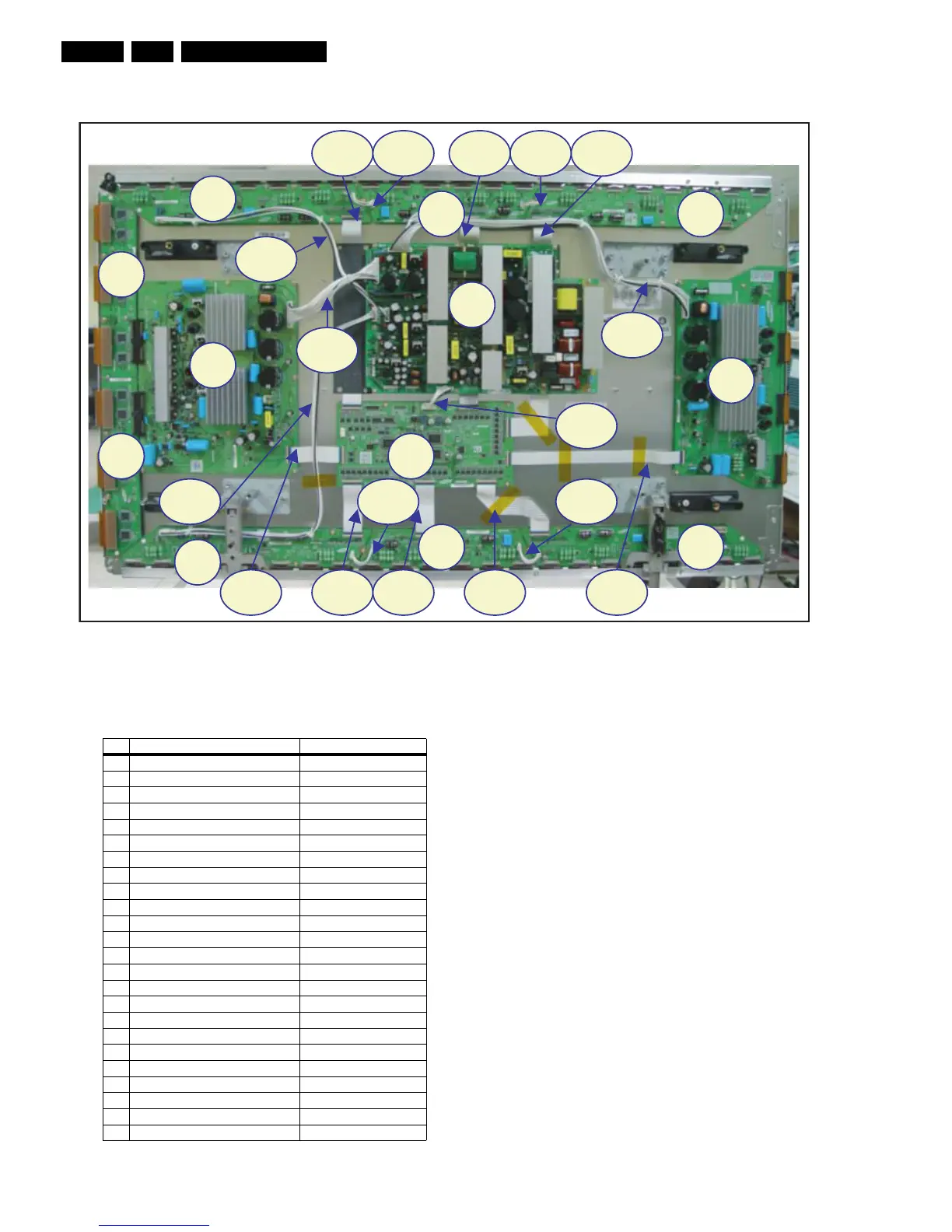

1.3.8 50” HD v4

Figure 1-26 PWB location (50” HD v4)

Table 1-10 PWB overview (50” HD v4)

F_14991_017.eps

030805

1

2

4

6

7

11

10 12 14

15 16

18

5

6

17

19

22

23

24

1918

21

20

13

7

8

3

9

5

No. Location Name

1 SMPS SMPS

2 LOGIC-MAIN Board Assy PWBLOGIC Main

3 X-MAIN Driving Board Assy PWBX Main

4 Y-MAIN Driving Board Assy PCBY Main

5 LOGIC E BUFFER Board Assy PWB Buffer

6 LOGIC F BUFFER Board Assy PWB Buffer

7 LOGIC G BUFFER Board Assy PWB Buffer

8 Y-BUFFER (Upper) Board Assy PWB Buffer

9 Y-BUFFER (Down) Board Assy PWB Buffer

10 LOGIC + Y-MAIN FFC Cable-flat

11 LOGIC + X-MAIN FFC Cable-flat

12 LOGIC + LOG. BUF(G: Down) FFC Cable-flat

13 LOGIC + LOG. BUF(F: Down) FFC Cable-flat

14 LOGIC + LOG. BUF(E: Down) FFC Cable-flat

15 LOGIC + LOG. BUF(E: Upper) FFC Cable-flat

16 LOGIC + LOG. BUF(F: Upper) FFC Cable-flat

17 LOGIC + LOG. BUF(G: Upper) FFC Cable-flat

18 LOGIC BUF(E) + LOG. BUF(F) Lead connector

19 LOGIC BUF(F) + LOG. BUF(G) Lead connector

20 SMPS + LOGIC BUF(G: Down) Lead connector

21 SMPS + LOGIC BUF(E: Upper) Lead connector

22 SMPS + LOGIC MAIN Lead connector

23 SMPS + Y-MAIN Lead connector

24 SMPS + X-MAIN Lead connector

Loading...

Loading...