Block Diagrams, Test Point Overview, and Waveforms

EN 40 SDI PDP6.

6. Block Diagrams, Test Point Overview, and Waveforms

Index of this chapter:

6.1 Block Diagram for Logic Circuit

6.2 PSU Board diagram

6.1 Block Diagram for Logic Circuit

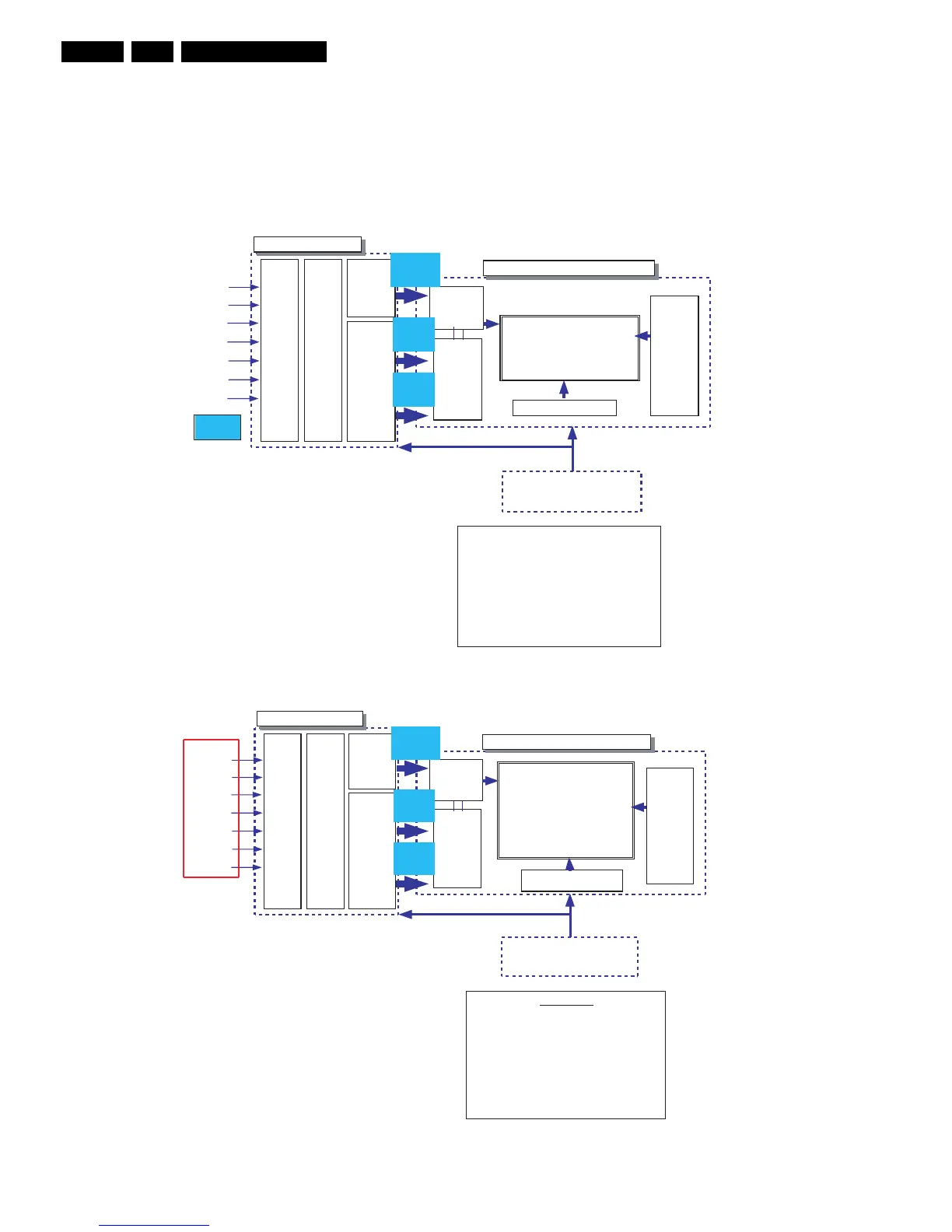

Figure 6-1 Block diagram (37" SD v4)

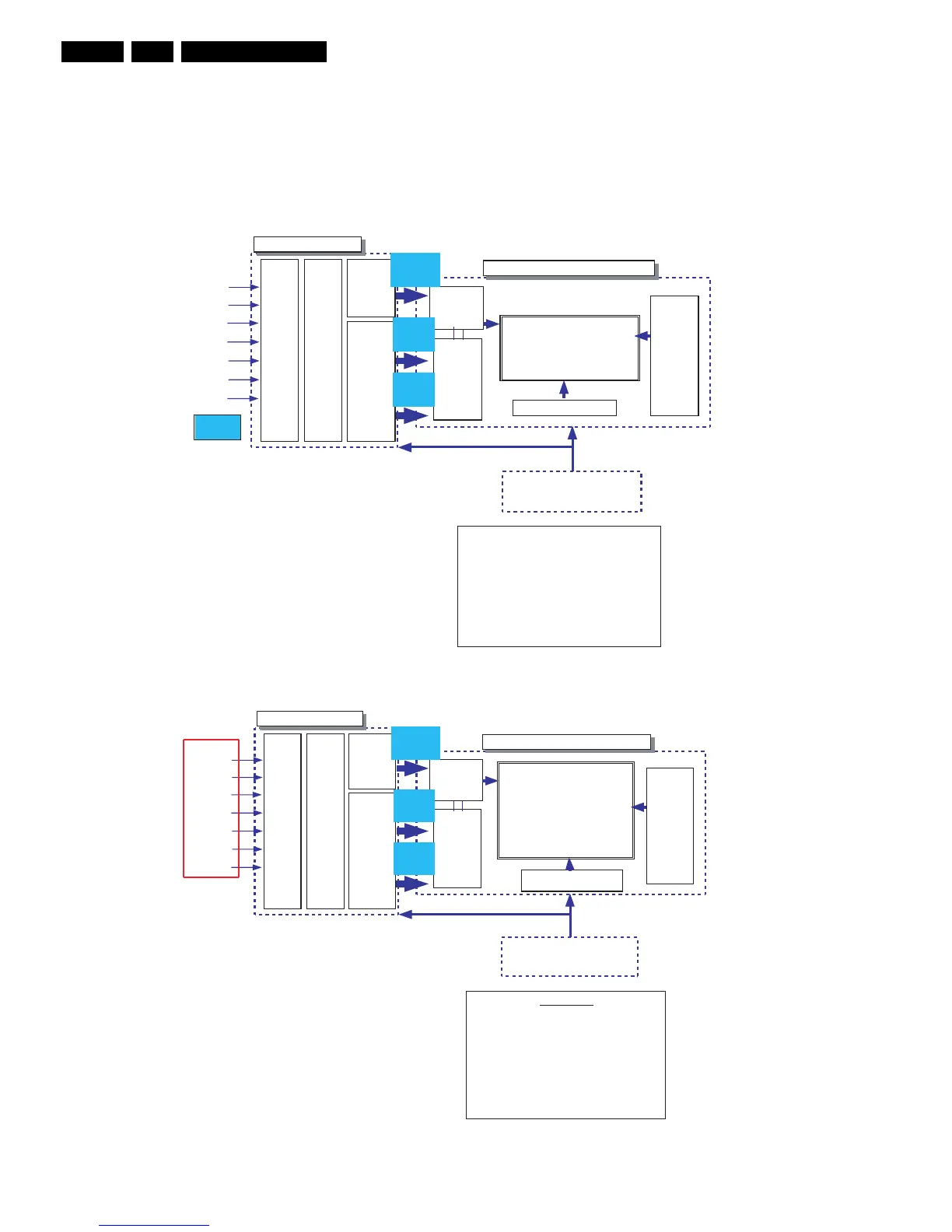

Figure 6-2 Block diagram (42" SD v2)

- Vcc : Voltage for Logic Control

- Vdd : Voltage for FET driver

- Va : Voltage for address pulse

- Vs : Voltage sustain pulse

- Vsc : Voltage for scan pulse

- Ve : Voltage for X ramp pulse

- Vset : Voltage for Y ramp pulse

Reference

VsVa

Vcc

Enable

Hsync

DCLK

Display

Data

Driver

Timing

Scan

Timing

Vdd

Vset Vsc

Ve

LVDS

Interface

Data Controller

Input Data Processor

Driver

Timing Controller

DRAM

Row

Driver

Y Pulse

Generator

852 x 480 Pixels

852 x 3 x 480 Cells

Column Driver

X Pulse

Generator

DRIVER CIRCUIT & PANEL

LOGIC CONTROL

DATA_R

8 Bits

DATA_G

8 Bits

DATA_B

8 Bits

Vsync

852× 480 Pixels

852× 3× 480 Cells

PY ulse

Ge tarenor

oRw

rD iver

VsVa

V5

Vs ync

Enable

Hsync

DCLK

ARDM

Display

Data

irDver

Timi gnCtnoroller

Driver

Timing

Scan

Timing

Vdd

DATA_R

8Bits

Column Driver

Reference

-V3.3 :

-V5 :

-Vdd :

-Va :

-Vs :

-Vsc :

-Ve :

-Vset :

LOGIC CONTROL

DRIVER CIRCUIT & PANEL

DATA_G

8Bits

DATA_B

8Bits

In tupDataProcsesor

aD taoCntor ller

PXulse

eGnerator

Vset Vsc

Ve V3.3

LVDS

Voltage for LOGIC Control

Voltage for COF driver

Voltage for FET driver

Voltage for address pulse

Voltage for sustain driver

Voltage for scan pulse

Voltage for X ramppulse

Voltage for Y ramppulse

Loading...

Loading...