SM-SX1/SX1W

– 37 –

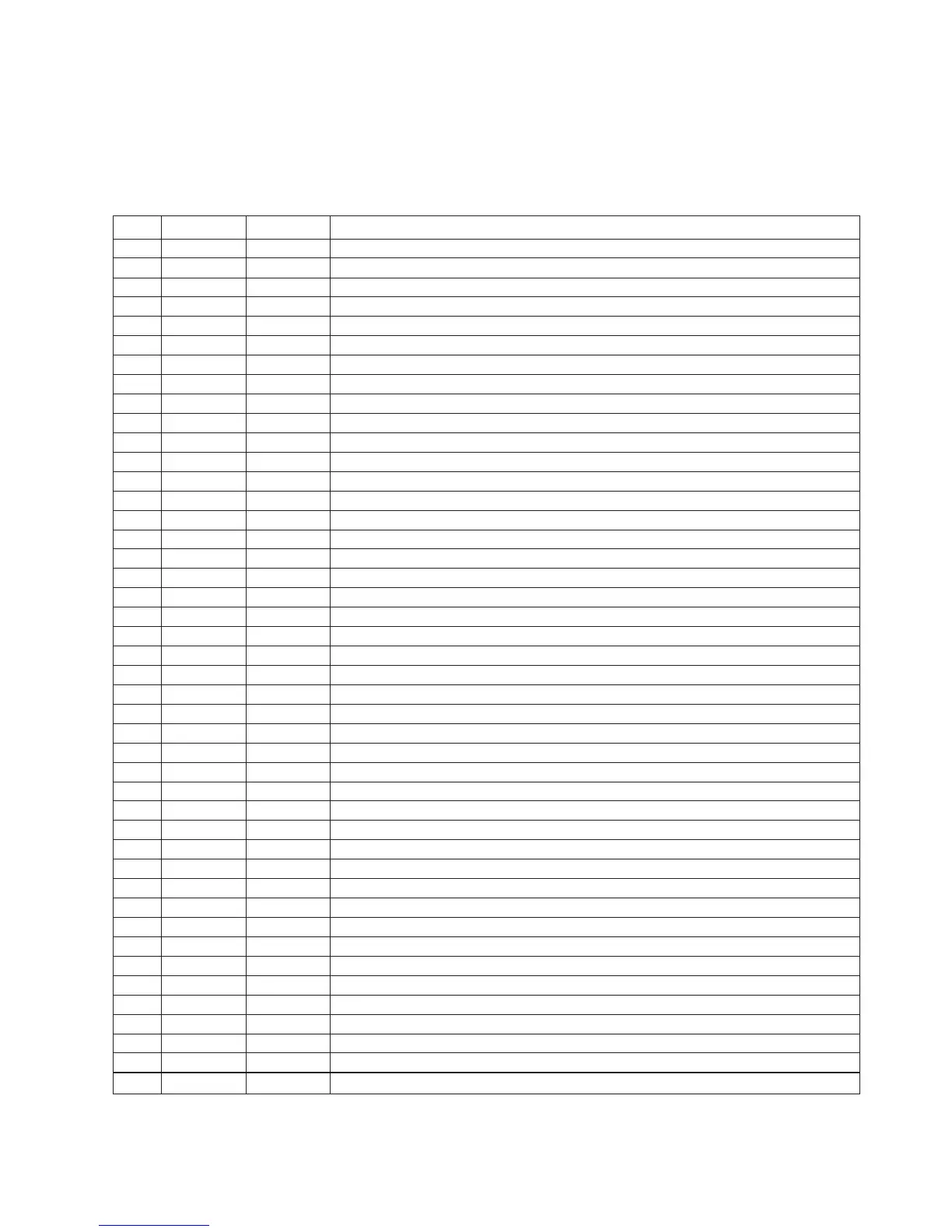

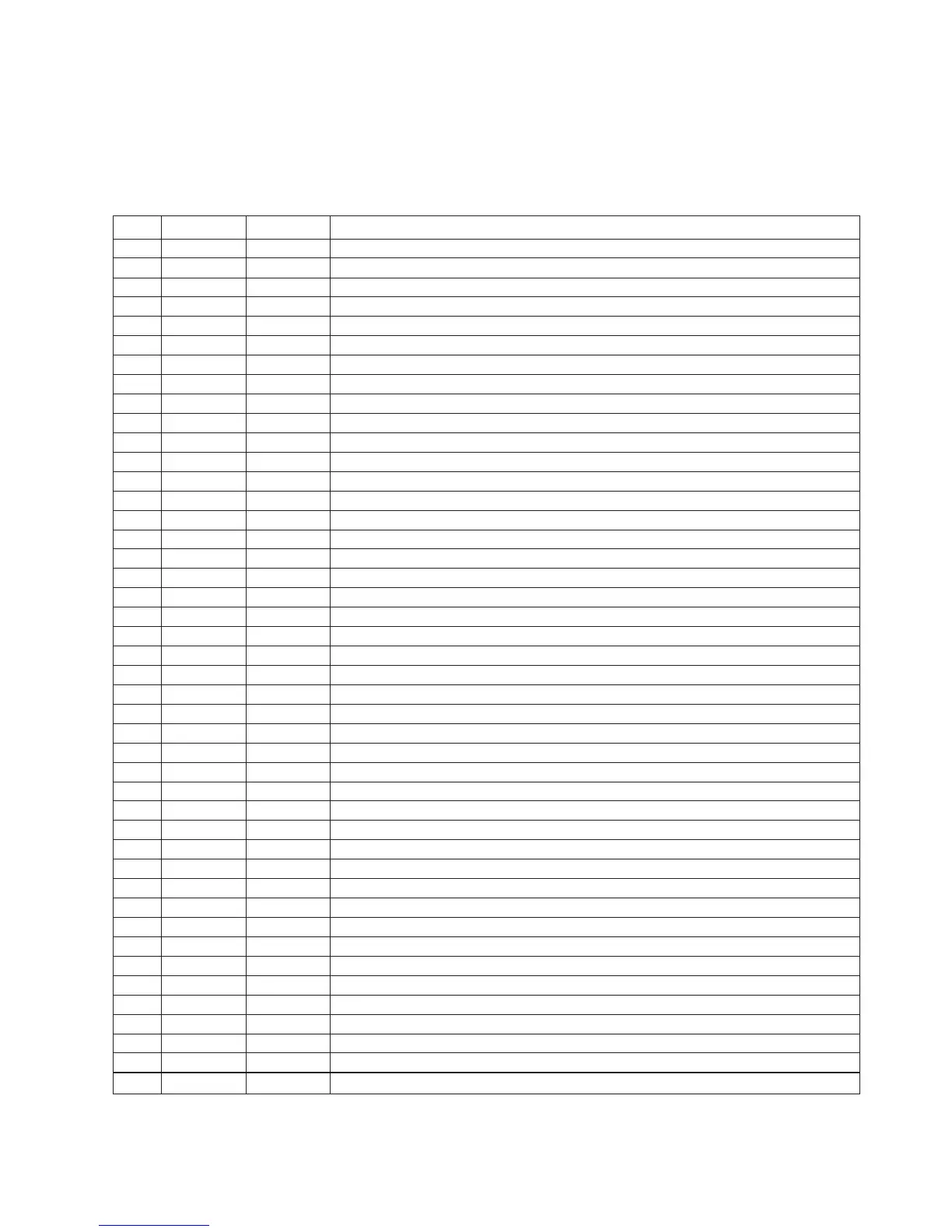

IC800 VHiYM3436D/-1: Digital Interface Receiver (YM3436D)

1 DAUX Input Audio data auxiliary input

2* HDLT Output Asynchronous buffer operation flag output

3 DOUT Output Audio data output

4* VFL Output Validity flag output

5* OPT Output Synchronous signal output (fs) for DAC

6* SYNC Output Synchronous signal output (fs) for DSP

7 MCC Output Bit clock output (64fs)

8 WC Output Word clock output (fs)

9* MCB Output Bit clock output (128fs)

10 MCA Output Bit clock output (256fs)

11 SKSY Input Clock synchronizing control input

12 XI Input Quartz oscillator connection, or external clock input (256fs)

13 XO Output Quartz oscillator connection

14* P256 Output VCO clock output (When clocked, 256fs)

15 LOCKN Output PLL lock flag output ('L': Clocked, 'H': Unlocked)

16 VSS — Grand (logic system)

17* TST2 Output LSI test terminal (As usual, don't connect it.)

18 DIM1 Input Data input mode selection 1

19 DIM0 Input Data input mode selection 0

20 DOM1 Input Data output mode selection 1

21 DOM0 Input Data output mode selection 0

22 KM1 Input Clock mode selection 1 ('H': PLL auto switch, 'L': XI fixed)

23 RSTN Input System reset input (active low)

24 VDDA — +5V power supply (VCO system. Externally connect it to VDD.)

25 CTLN Input VCO control input

26 PCO Output PLL phase comparative output

27* N.C. — Not used

28 CTLP Input VCO adjustment input (As usual, connect it to VSSA.)

29 VSSA — Grand (VCO system. Externally connect it to VSS.)

30* TSTN Input LSI test terminal (As usual, it is not connected.)

31 KM2 Input Clock mode selection 2 ('H": PLL synchronization, 'L': XI synchronization)

32 KM0 Input Clock mode selection 0 ('H': EXTW input, 'L': DDIN input)

33 FS1 Output Sampling frequency code output 1/channel status output

34 FS0 Output Sampling frequency code output 0/user data output

35 CSM Input Channel status, user data output method selection

36 EXTW Input External synchronizing auxiliary input, Word clock

37 DDIN Input EIAJ(AES/EBU) digital audio interface signal input

38* LR Output PLL word clock output (When locked, fs)

39 VDD — +5V power (logic system)

40 ERR Output Data error flag output

41 EMP Output Emphasis control code output/block start synchronizing signal output

42* CDO Output Microcomputer interface data output

43 CCK Input Microcomputer interface clock input

44 CLD Input Microcomputer interface load input

Pin No. Port Name

Input/Output

FUNCTION TABLE OF IC

In this unit, the terminal with asterisk mark (*) is (open) terminal which is not connected to the outside.

• Outline

YM3436D(DIR2) is a LSI which receives and demodulates the digital/audio/interface/format signals which comply with EIAJ CP-

340 and AES/EBU. Keeping the features of the existing YM3623B(DIR), it is designed to not only strengthen the external

synchronization, error process and other functions but also be more general for the channel status, user data output and other

general applications.

Function

Loading...

Loading...