Sinclair ZX Spectrum Service Manual

Spectrum For Everyone https://spectrumforeveryone.com/

16

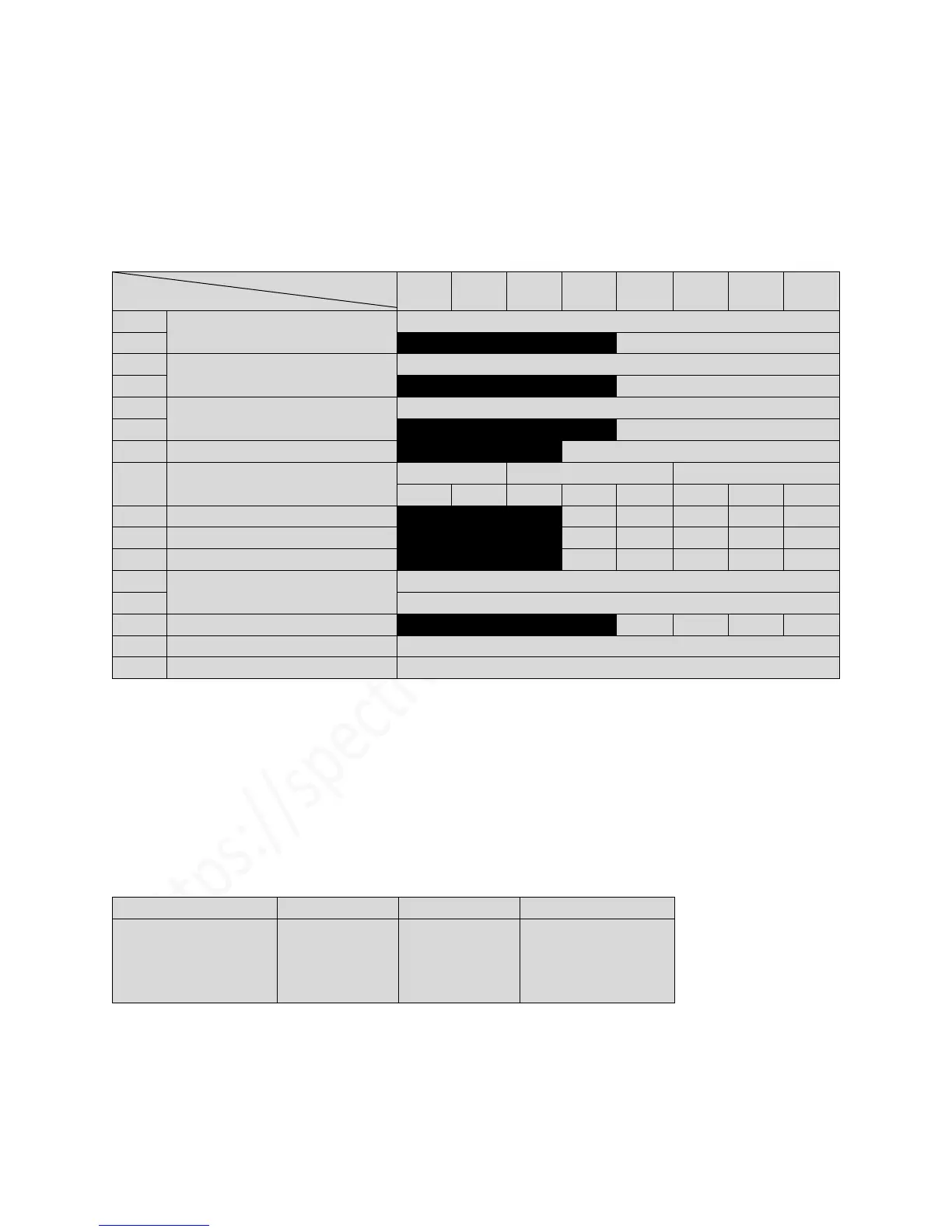

1.7 PROGRAMMABLE SOUND GENERATOR

The audio from the sound generator IC32 is derived from a master clock input supplied by the ULA,

controlled and shaped in accordance with instruction codes loaded by the Z80 into 14 internal byte wide

registers (see below).

8-bit Fine Tune Envelope Period

8-bit Coarse Tune Envelope Period

8-bit Parallel I/O on Port A*

8-bit Parallel I/O on Port B*

* RS232/MIDI interface (see below)

The Z80 specifies a register by loading the data bus while writing to address FFFD

H

in the I/O space. DA3-

DA0 supply the octal address between 0 and 15, DA7-DA4 should be all zero. (In the address mode, DA7-

DA4 with IC32 pin 17 strapped high externally, are decoded in IC32 to provide a ‘chip select’ signal). The

instruction code is then written to the register by writing to address BFFD

H

.

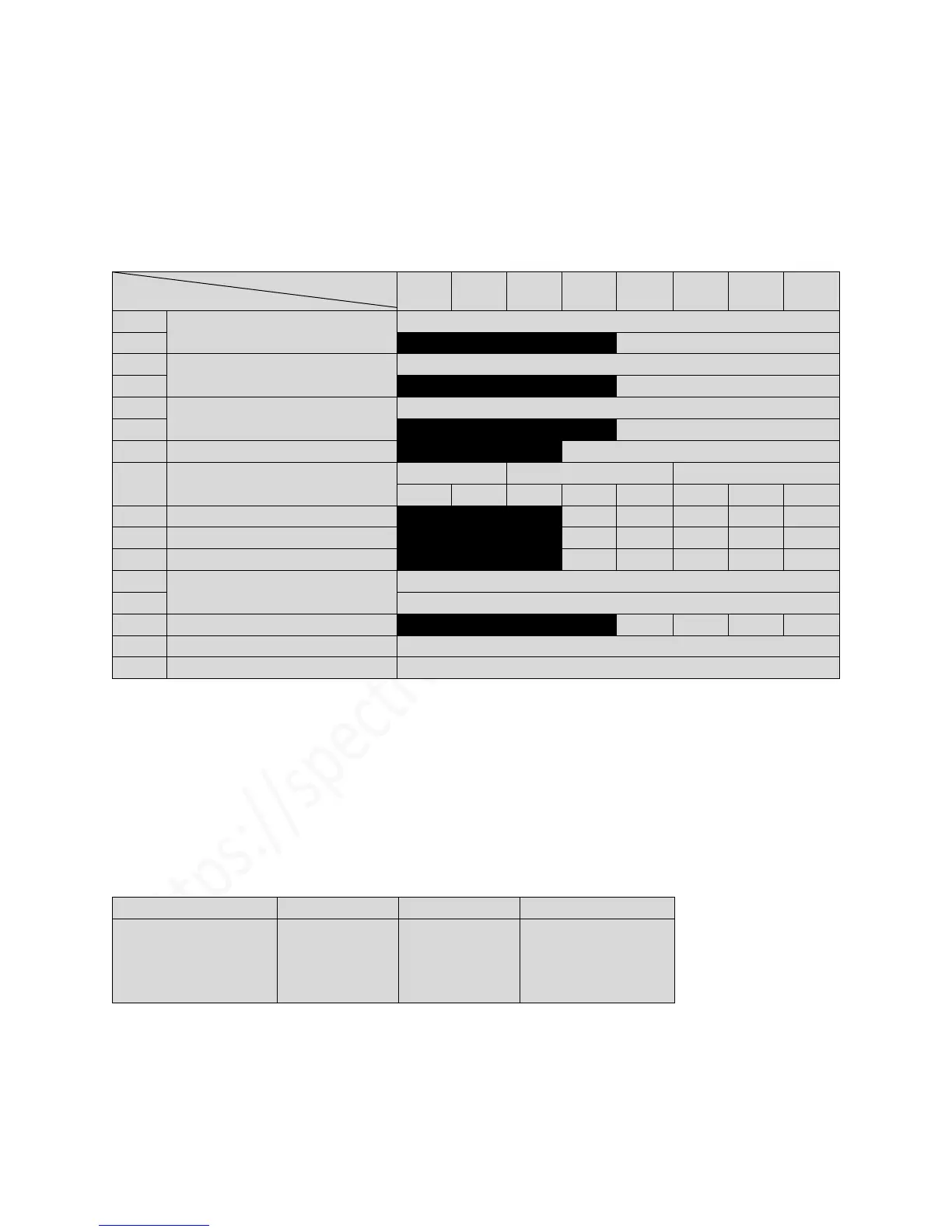

BC1 and BDIR, decoded in D26,27 from PSG, A14 and RDL, define the type of write operation for the

sound generator as follows:

* RS232C/MIDI interface (see below)

PSG is decoded in IC29 from /IORQ with /RD or /WR (I/O read/write cycle) and ZA1 = 0 and ZA15 = 1

(address FFFD

H

with A14 high; address BFFD

H

with A14 low).

Loading...

Loading...