Sinclair ZX Spectrum Service Manual

Spectrum For Everyone https://spectrumforeveryone.com/

7

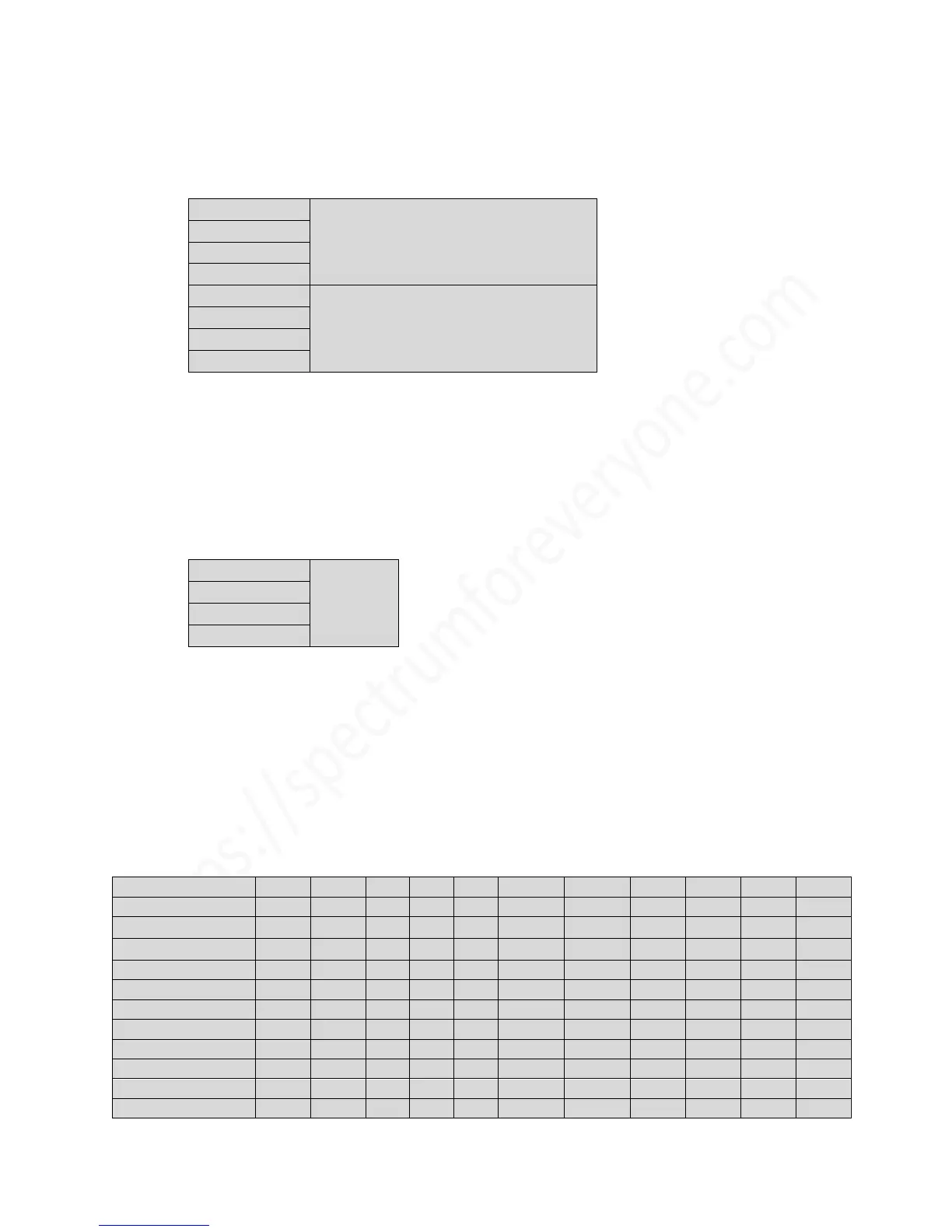

1.4 MEMORY ORGANISATION

The Spectrum 128 has 160K bytes of addressable memory - a 32K byte ROM (IC5) and 128K bytes of

dynamic RAM (IC6-IC22). The latter is organised as eight 16K byte pages as indicated below.

Contended video RAM (ICs 6-13)

Uncontended ‘upper’ RAM (ICs 15-22)

Pages 0-3 are uncontended and are accessed solely by the Z80. Pages 4-7 are contended in that the Z80

and ULA IC1 both require access to pages 5 and 7 in order to generate the memory mapped displays.

(Editor’s note – this is inaccurate. Pages 1,3,5 and 7 are contended and pages 0,2,4 and 6 are uncontended. This is due to an

error in the PAL (IC29) equations. This was not corrected until the arrival of the +2A and +3 models.)

The address of any page of RAM depends on where it appears in the address space of the Z80 which is

structured as follows:

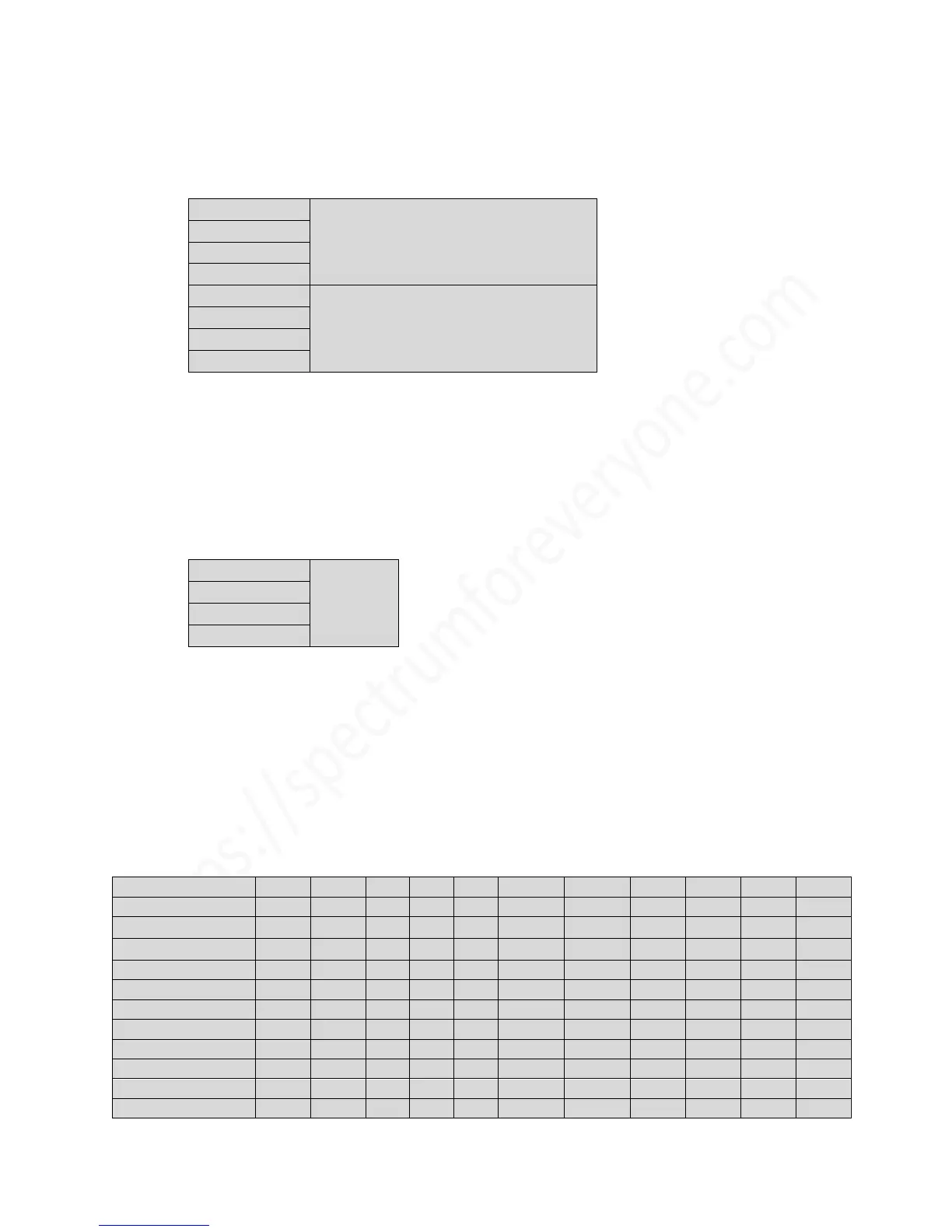

All memory accesses are controlled by the programmable logic array (PAL) IC29. It does this by decoding

the two most significant Z80 address bits Z15, Z14 with bits B2-B0 from the bank register to produce

three pairs of supplementary address lines. They are:

a) UA15, 14 specifying the page number in the uncontended RAM space

b) VA15, 14 specifying the page number in the contended RAM space

c) ULA15, 14 controlling bus arbitration and Z80 access to the ROM and contended RAM space.

The decodes are summarised below and described in the following paragraphs.

Loading...

Loading...