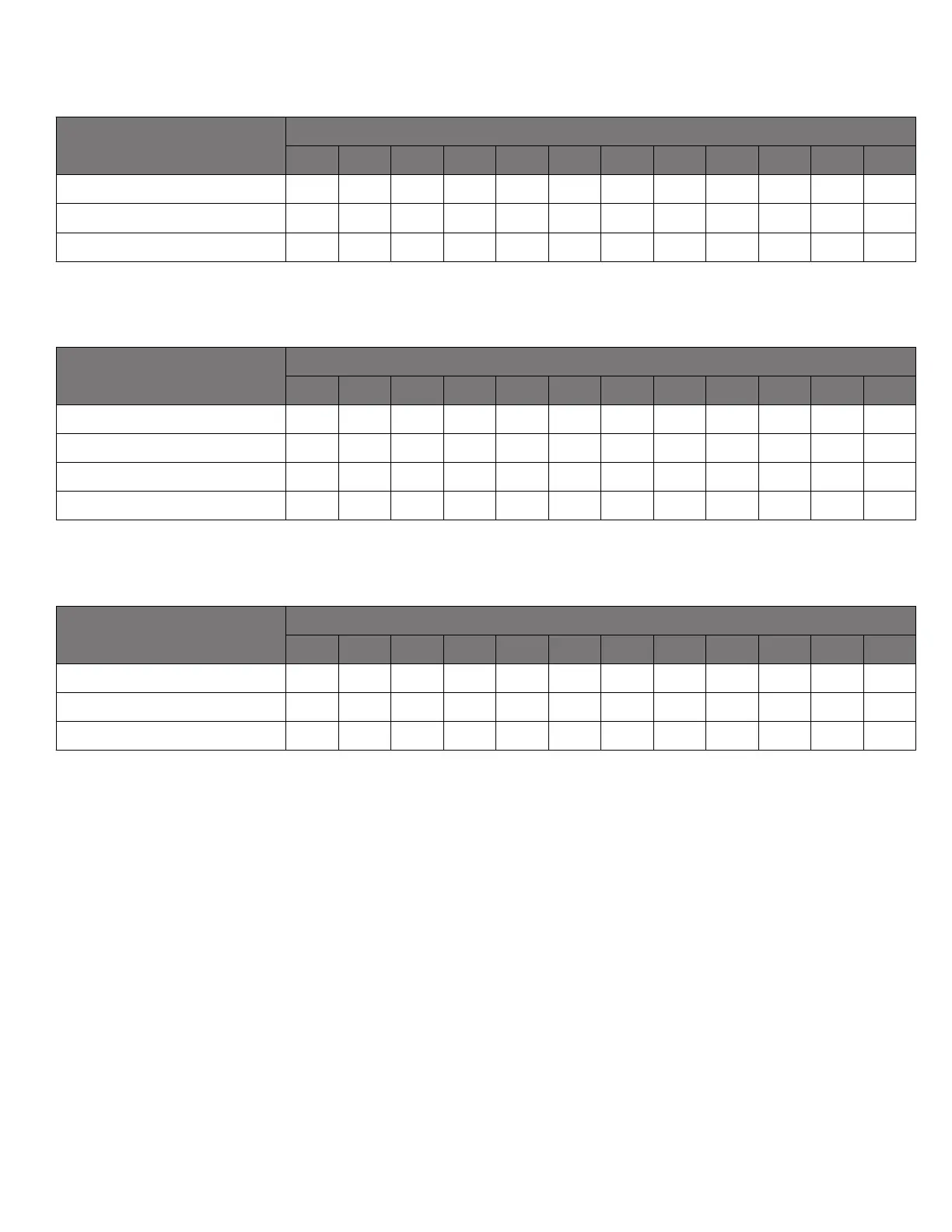

Table 2.2. Only Domain 1 and 2 Output Frequencies

Output Clock Frequencies Output Clock Location allowed?

0A 0 1 2 3 4 5 6 7 8 9 9A

125/156.25/312/625 yes yes yes yes yes yes yes no no no no no

25/125/200 no no no yes yes yes yes yes yes yes yes yes

50/100 no no no no yes yes yes yes yes yes yes yes

Table 2.3. Domain 1, 2, and 3 Output Frequencies

Output Clock Frequencies Output Clock Location allowed?

0A 0 1 2 3 4 5 6 7 8 9 9A

125/156.25/312/625 yes yes yes yes yes yes yes no no no no no

25/125/200 no no no yes yes yes yes yes yes yes yes yes

50/100 no no no no yes yes yes yes yes yes yes yes

322.265625/644.53125 no no no no no no no no yes yes yes yes

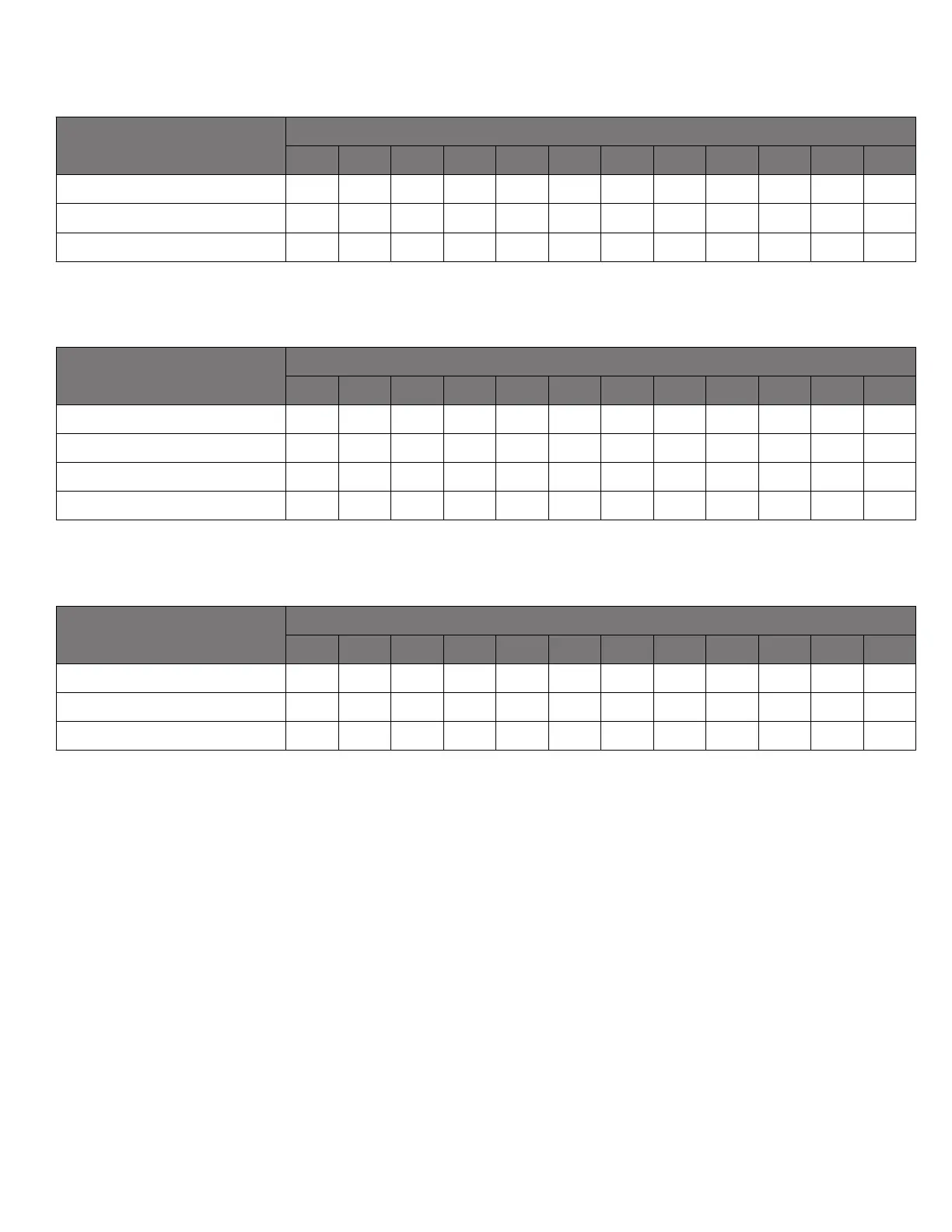

Table 2.4. Only Domain 1 and 3 Output Frequencies

Output Clock Frequencies Output Clock Location allowed?

0A 0 1 2 3 4 5 6 7 8 9 9A

156.25/312/625 yes yes yes yes no no no no no no no no

125 yes yes yes yes yes yes yes yes yes yes yes yes

322.265625/644.53125 no no no no no no no no yes yes yes yes

156.25MHz/312.5MHz/625MHz Separation Rules to Domain 2 and 3 Clocks:

Even though the Si5391P has minimal coupling between adjacent clocks, a domain 2 or 3 clock that is adjacent to 156.25/312.5/625

MHz may couple too much energy to allow these Domain 1 clocks to meet <100 fs clocks. Therefore domain 2 and 3 clocks must be

isolated from 156.25/312.5/625 MHz outputs. In addition to the tables above, ClockBuilder Pro enforces gaps between domain 1 and

domain 2 outputs. ClockBuilder Pro makes it simple to achieve 156.25/312.5/625 MHz outputs that are guaranteed to have <100 fs rms

jitter. Only when the output clock locations meet all the rules, ClockBuilder Pro will classify a 156.25/312.5/625 MHz output as being

"precision" and guaranteed to achieve <100fs rms jitter.

2.2.3 Output Clock Format Restrictions

For the 156.25/312.5/625 MHz clocks to achieve < 100 fs jitter there are restrictions on the output formats as follows:

1. 156.25/312.5/625 MHz clocks can only be LVPECL or LVDS.

2. Domain 2 outputs can only be LVPECL, LVDS or HCSL.

3. Domain 3 outputs can only be LVPECL or LVDS.

4. If any domain 2 or 3 output is LVPECL or HCSL, then 156.25/312.5/625 MHz outputs must be LVPECL.

Si5391 Reference Manual • Family Product Comparison

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

7 Rev. 0.5 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • January 11, 2022 7

Loading...

Loading...