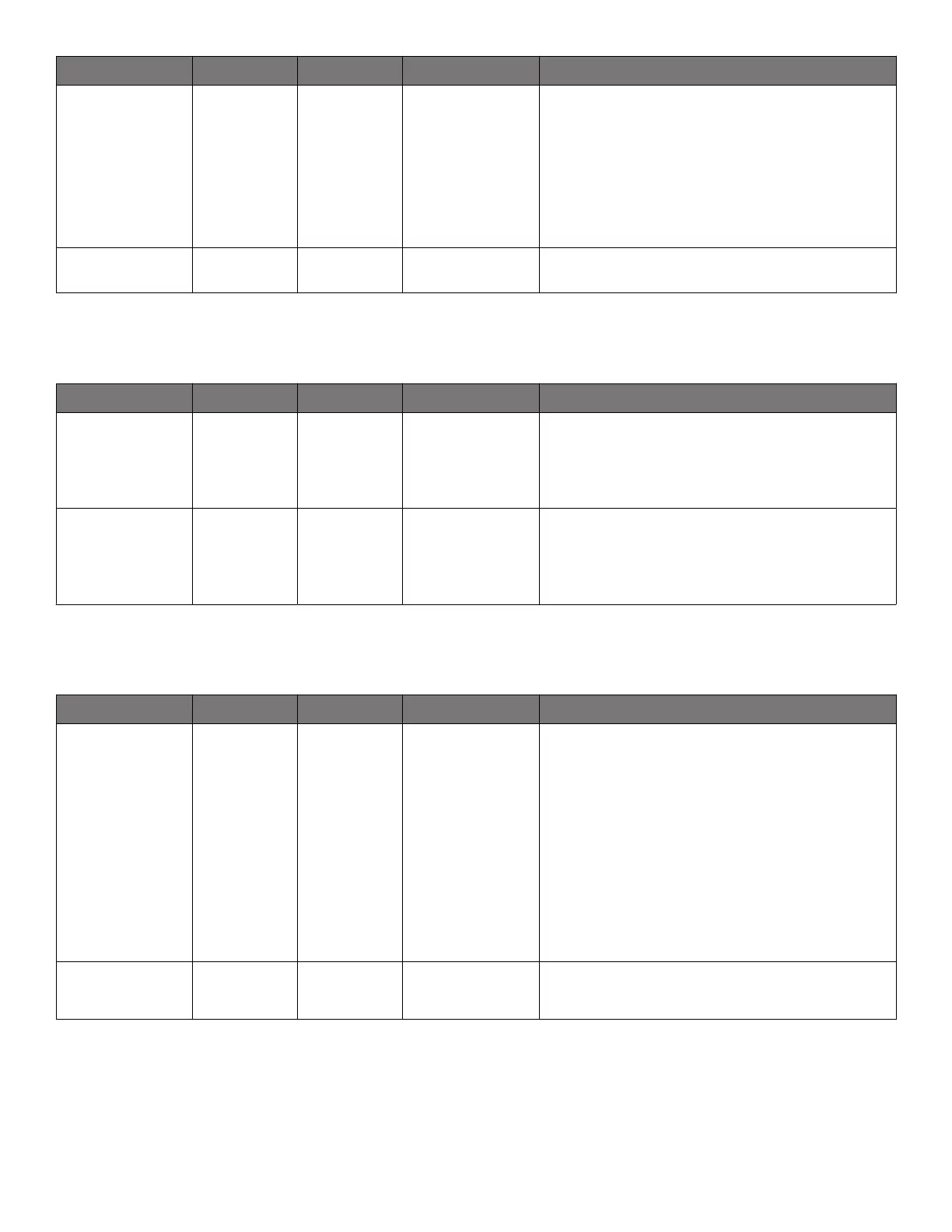

Reg Address Bit Field Type Setting Name Description

0x0104 5:4 R/W OUT0A_DIS_STAT

E

Determines the state of an output driver when disabled,

selectable as:

0: Disable in low state

1: Disable in high state

2: Reserved

3: Reserved

0x0104 7:6 R/W OUT0A_CMOS_DR

V

LVCMOS output impedance. See 8.4.8 Output Driver

Settings for LVPECL, LVDS, HCSL, and CML.

See 8.3 Performance Guidelines for Outputs.

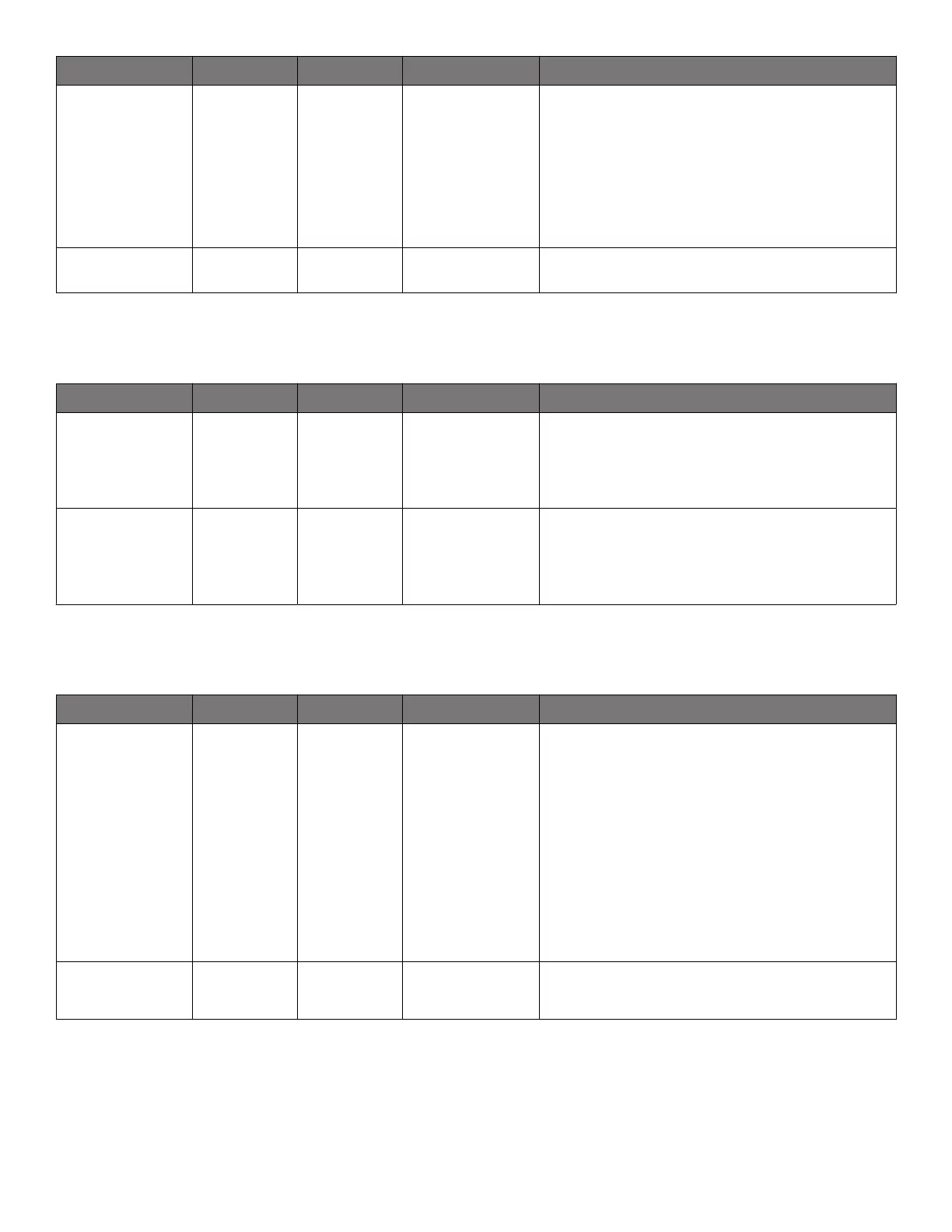

Table 15.42. 0x0105 Clock Output 0A Amplitude and Common Mode Voltage

Reg Address Bit Field Type Setting Name Description

0x0105 3:0 R/W OUT0A_CM This field only applies when OUT0A_FORMAT=1 or 2.

See 8.4.8 Output Driver Settings for LVPECL, LVDS,

HCSL, and CML and 8.4.9 Setting the Differential Out-

put Driver to Non-Standard Amplitudes for details of the

settings.

0x0105 6:4 R/W OUT0A_AMPL This field only applies when OUT0A_FORMAT=1 or 2.

See 8.4.8 Output Driver Settings for LVPECL, LVDS,

HCSL, and CML and 8.4.9 Setting the Differential Out-

put Driver to Non-Standard Amplitudes for details of the

settings.

ClockBuilder Pro sets the correct common mode voltage and amplitude for LVDS, LVPECL, and HCSL outputs.

Table 15.43. 0x0106 Clock Output 0A Mux and Inversion

Reg Address Bit Field Type Setting Name Description

0x0106 2:0 R/W OUT0A_MUX_SEL

OUT0A output source divider select. This selects the

multisynth (N divider) that is connected to the output

driver.

0: N0

1: N1

2: N2

3: N3

4: N4

5-7: Reserved

0x0106 3 R/W OUT0A_VDD_SEL_

EN

Output Driver VDD Select Enable. Set to 1

for normal operation.

Si5391 Reference Manual • Si5391A/B Register Map

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • sales@skyworksinc.com • www.skyworksinc.com

74 Rev. 0.5 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • January 11, 2022 74

Loading...

Loading...