STR-DN1010

72

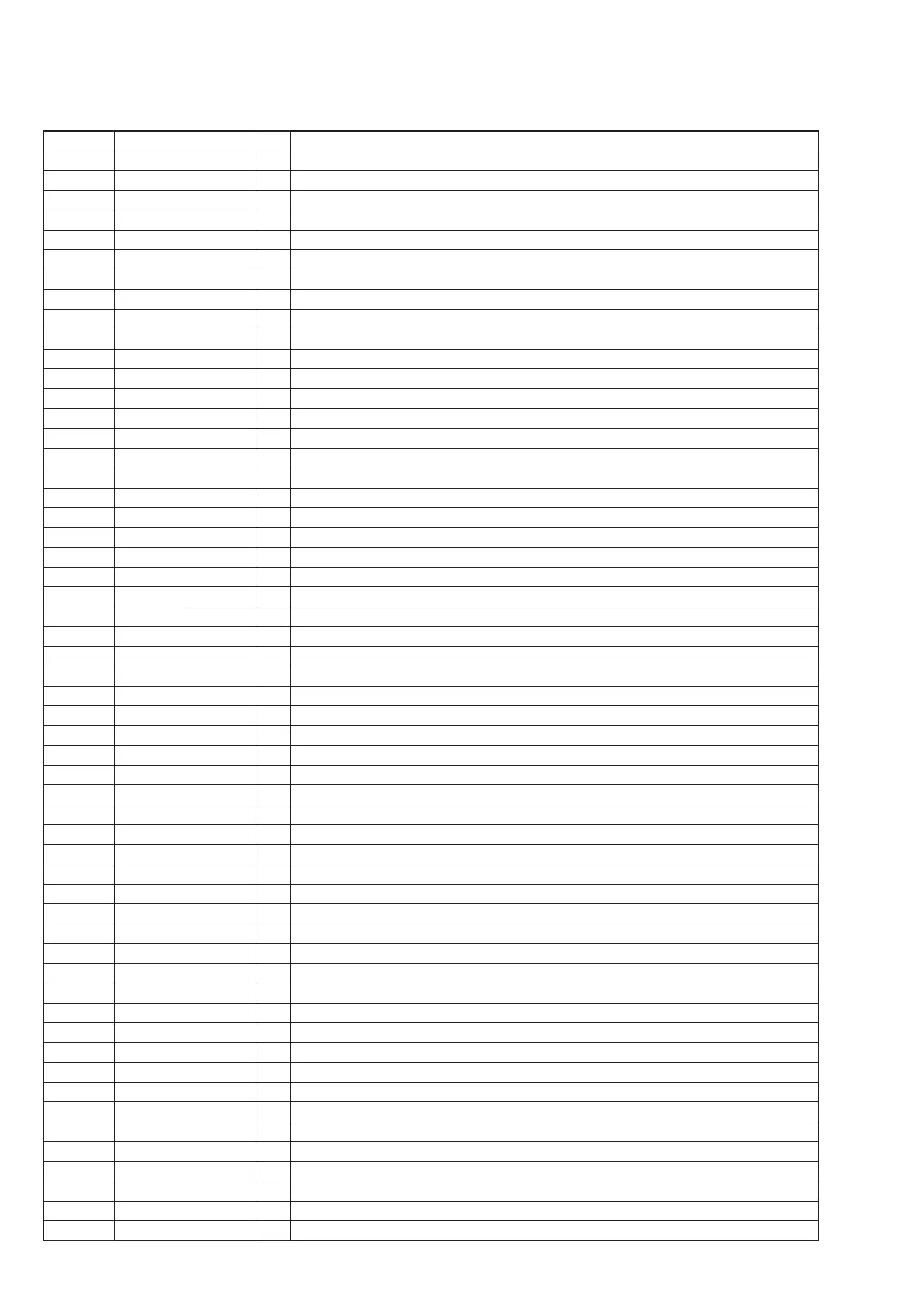

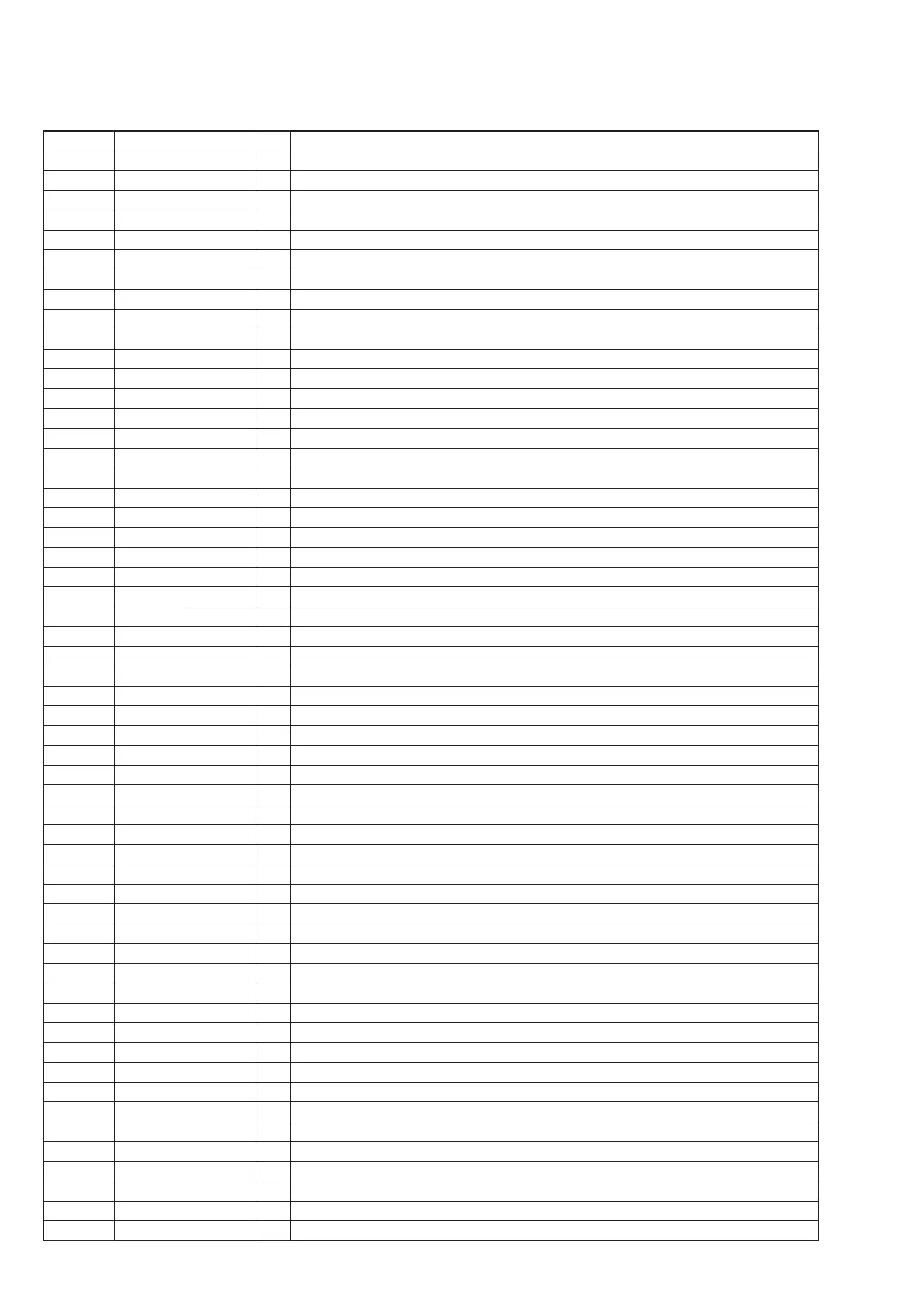

DSP BOARD IC5001 D788E002BRFP266 (DSP)

Pin No. Pin Name I/O Description

1 Vss - Ground terminal

2 AHCLIO0/AHCLKX2 I Master clock signal input from the digital audio interface receiver and BD decoder

3 AMUTE0 - Not used

4 AMUTE1 - Not used

5 AHCLKX1 - Not used

6 Vss - Ground terminal

7 ACLKX1 O Bit clock signal output to the wireless transceiver and stream processor

8 CVdd - Power supply terminal (+1.2V)

9 ACLKR1 I Bit clock signal input from the digital audio interface receiver and BD decoder

10 DVdd - Power supply terminal (+3.3V)

11 AFSX1 O L/R sampling clock signal output to the wireless transceiver and stream processor

12 AFSR1 I L/R sampling clock signal input from the digital audio interface receiver and BD decoder

13 Vss - Ground terminal

14 RESET# I Reset signal input from the system controller “L”: reset

15 Vss - Ground terminal

16 CVdd - Power supply terminal (+1.2V)

17 CLKIN - Not used

18 Vss - Ground terminal

19 TMS - Not used

20 CVdd - Power supply terminal (+1.2V)

21 TRST# - Not used

22 OSCVss - Not used

23 OSCIN I System clock input terminal (25 MHz)

24 OSCOUT O System clock output terminal (25 MHz)

25 OSCVss - Not used

26 Vss - Ground terminal

27 PLLHV - Power supply terminal (+3.3V)

28 TDI - Not used

29 TDO - Not used

30 Vss - Ground terminal

31 DVdd - Power supply terminal (+3.3V)

32 EMU[0]# - Not used

33 CVdd - Power supply terminal (+1.2V)

34 EMU[1]# - Not used

35 TCK - Not used

36 Vss - Ground terminal

37 EM_CAS# O Column address strobe signal output to the SD-RAM

38 EM_WE# O Write enable signal output to the SD-RAM

39 EM_WE_DQM[0] O Byte enable signal output to the SD-RAM

40 Vss - Ground terminal

41 EM_D[7] I/O Two-way data bus with the SD-RAM

42 DVdd - Power supply terminal (+3.3V)

43 EM_D[6] I/O Two-way data bus with the SD-RAM

44 CVdd - Power supply terminal (+1.2V)

45, 46 EM_D[5], EM_D[4] I/O Two-way data bus with the SD-RAM

47 Vss - Ground terminal

48, 49 EM_D[3], EM_D[2] I/O Two-way data bus with the SD-RAM

50 DVdd - Power supply terminal (+3.3V)

51, 52 EM_D[1], EM_D[0] I/O Two-way data bus with the SD-RAM

53 CVdd - Power supply terminal (+1.2V)

54 Vss - Ground terminal

55, 56 EM_D[15], EM_D[14] I/O Two-way data bus with the SD-RAM

57 CVdd - Power supply terminal (+1.2V)

58, 59 EM_D[13], EM_D[12] I/O Two-way data bus with the SD-RAM

60 DVdd - Power supply terminal (+3.3V)

Loading...

Loading...