PM0075 Register descriptions

Doc ID 17863 Rev 1 25/31

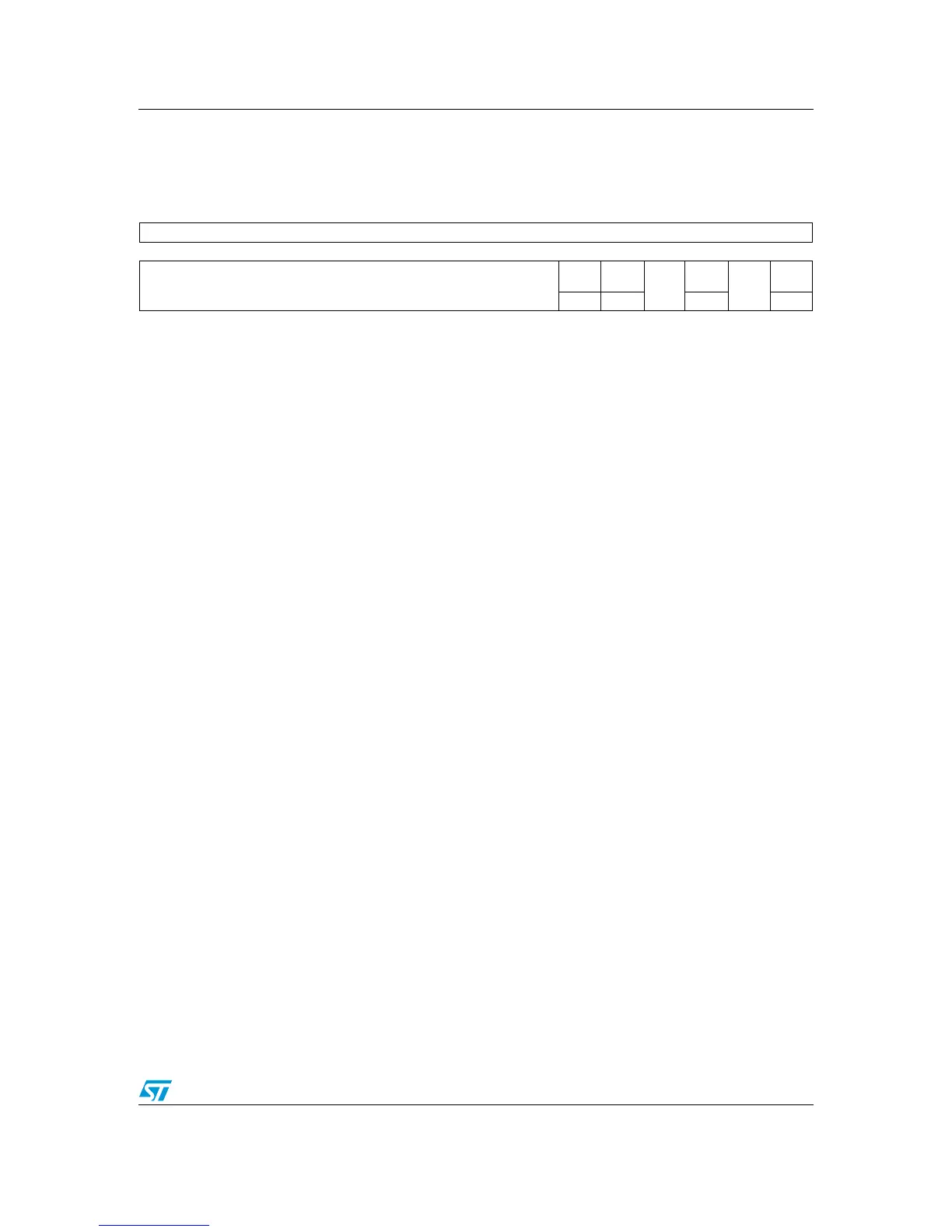

3.4 Flash status register (FLASH_SR)

Address offset: 0x0C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

EOP

WRPRT

ERR

Res.

PG

ERR

Res.

BSY

rw rw rw r

Bits 31:6 Reserved, must be kept cleared.

Bit 5 EOP: End of operation

Set by hardware when a Flash operation (programming / erase) is completed. Reset by

writing a 1

Note: EOP is asserted at the end of each successful program or erase operation

Bit 4 WRPRTERR: Write protection error

Set by hardware when programming a write-protected address of the Flash memory.

Reset by writing 1.

Bit 3 Reserved, must be kept cleared.

Bit 2 PGERR: Programming error

Set by hardware when an address to be programmed contains a value different from

'0xFFFF' before programming.

Reset by writing 1.

Note: The STRT bit in the FLASH_CR register should be reset before starting a programming

operation.

Bit 1 Reserved, must be kept cleared

Bit 0 BSY: Busy

This indicates that a Flash operation is in progress. This is set on the beginning of a Flash

operation and reset when the operation finishes or when an error occurs.

Loading...

Loading...