2-24

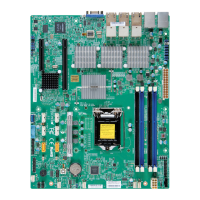

X10SDV Flex ATX Series Motherboard User’s Manual

BAR CODE

JTGLED1

X10SDV-TP8F

REV:1.01

DIMMB1

DIMMA2

DIMMB2

DIMMA1

BT1

LED3

C

LEDM1

A

C

LED8

C

LED7

A

C

JITP1

DESIGNED IN USA

COM1

1

PRESS FIT

JPS1

JPG1

JWD1

JPME2

JBR1

JPUSB1

JPL1

JPL2

JPME1

JPL3

JPTG1

JI2C2

JI2C1

JSMB1

JPB1

JNVI2C1

JIPMB1

LEDT4

A

C

LEDT2

A

C

LEDT3

A

C

LEDT1

A

C

LEDS1

A

MP_SRW1

MP_SRW2

JMP1

FAN4

FANA

FANB

FAN1

FAN3

FAN2

JSTBY1

JLANLED1

I-SGPIO1

I-SATA3

I-SATA2

I-SATA0

I-SATA1

JSD1

JSD2

JOH1

JL1

JTPM1

JF1

JSAS4

PRESS FIT

JSAS3

PRESS FIT

JSAS2

PRESS FIT

JSAS1

PRESS FIT

JPW1

JPI2C1

JD1

JGP1

JPH1

JPV1

M2_SRW2

M2_SRW3

M2_SRW1

VGA

LAN 7/8

LAN 5/6

LAN 3/4

LAN 1/2

JOH1-OH

SATA DOM + POWER

L-SAS12-15

L-SAS0-3

L-SAS4-7

L-SAS8-11

IPMI_LAN

2-3:DISABLE

1-2:ENABLE

JPUSB1:USB0/1 WAKE UP

2-3:DISABLE

LAN3/4/5/6

1-2:ENABLE

JPL3:

ON

PWR

RST

X

FF

OH

NIC2

JF1:

NIC1

LED

HDD

LED

PWR

PCI-E 2.0 X1 /

I-SATA5

CPU SLOT7 PCI-E 3.0 X8

CPU SLOT6 PCI-E 3.0 X8

USB 5/6

USB 3/4

USB 2

USB 0/1(3.0)

PCI-E 3.0 X4 / I-SATA4

JMD1: M.2

Intel Xeon

D-1500

SoC

1-2:ENABLE

2-3:DISABLE

JPG1:

2-3:DISABLE

JPL1/JPL2:

1-2:ENABLE

JL1:

2-3:NMI

1-2:RST

JWD1:WATCH DOG

JBT1:

LAN2

LAN1/

CHASSIS

CMOS

INTRUSION

CLEAR

4-7:SPEAKER

1-3:PWR LED

JD1:

1-2:ENABLE

2-3:DISABLE

JI2C1/JI2C2:

UID

1-2:ENABLE

2-3:DISABLE

JPS1:SAS

2-3:DISABLE

1-2:ENABLE

JPTG1:

10Gb LAN

JBR1

1-2:NORMAL

2-3:BIOS RECOVERY

LSI

2116

(-7TP4F/-7TP8F)

BMC

AST2400

PHY

10GbE

CS2447

i350

AM4

(-7TP8F/

-TP8F)

A. I-SGPIO1

B. JSMB1

Serial Link I/O Header

The Serial Link General Purpose In-

put/Output (SGPIO) header is used to

communicate with the enclosure man-

agement chip in the system. See the

table on the right for pin denitions.

B

A

Serial Link I/O Header

Pin Denitions

Pin# Denition Pin Denition

1 NC 2 NC

3 Ground 4 DATA Out

5 Load 6 Ground

7 Clock 8 NC

System Management Bus Header

The System Management Bus header

for additional slave devices or sensors

is located as JSMB1. Refer to the table

on the right for pin denitions.

SMBus Power

Pin Denitions

Pin# Denition

1 Data

2 Ground

3 Clock

Loading...

Loading...