www.ti.com

Example Low Power Use Cases

31

SPRAC74A–February 2017–Revised March 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

AM335x Low Power Design Guide

4.4.2 IPerf

Device Tree Name Ethernet SGX

am335x-gp-evm-powersave.dtb Yes No

AM335x EVM is configured as client UDP, PC as UDP server transmitting 100 Mbps. AM335x is able to

handling 100 Mbps at MPU OPP50.

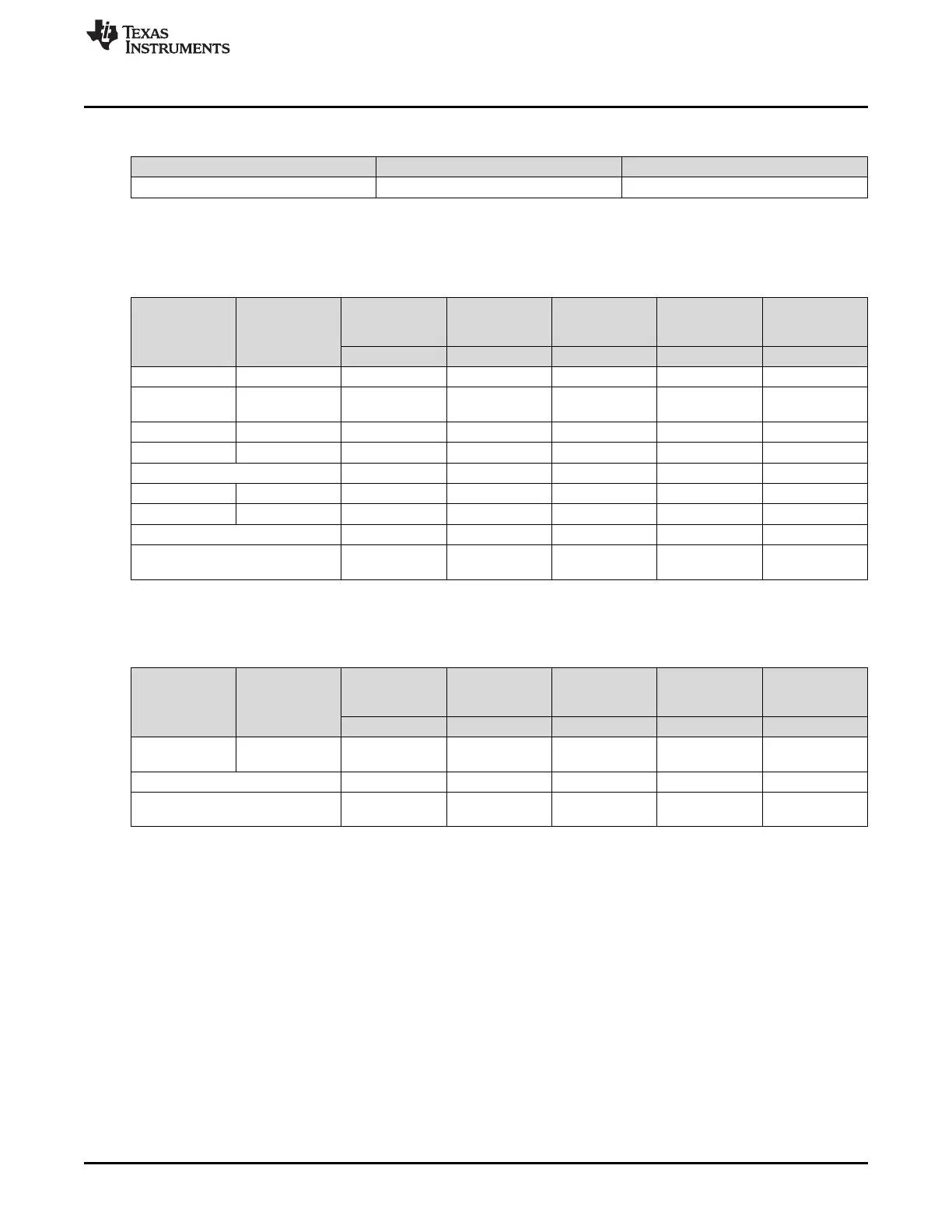

Table 12. Optimized Network Load Power Consumption

Power Rail Voltage (V)

MPU OPP50

(300 MHz)

MPU OPP100

(600 MHz)

MPU OPP120

(720 MHz)

MPU OPP

Turbo

(800 MHz)

MPU OPP Nitro

(1000 MHz)

Power (mW) Power (mW) Power (mW) Power (mW) Power (mW)

vdd_core_power 1.1 173.22 174.35 175.01 174.73 175.04

vdd_mpu_power DVFS (0.95 -

1.325)

81.75 201.77 269.82 321.49 419.29

1.8V I/O 1.8 35.87 38.33 39.29 39.89 41.88

3.3V I/O 3.3 55.76 78.62 78.86 78.62 78.82

SoC Power without DDR3 372.84 493.08 562.99 614.72 715.02

vdds_mem 1.5 136.62 143.73 145.76 147.08 146.33

vddsddrmem 1.5 94.47 94.97 94.41 92.18 92.42

DDR3 Total Power (Includes VTT) 231.08 240.17 240.17 239.26 238.75

Total Power (SoC + DDR3) with

VTT

603.92 730.78 803.17 853.98 953.77

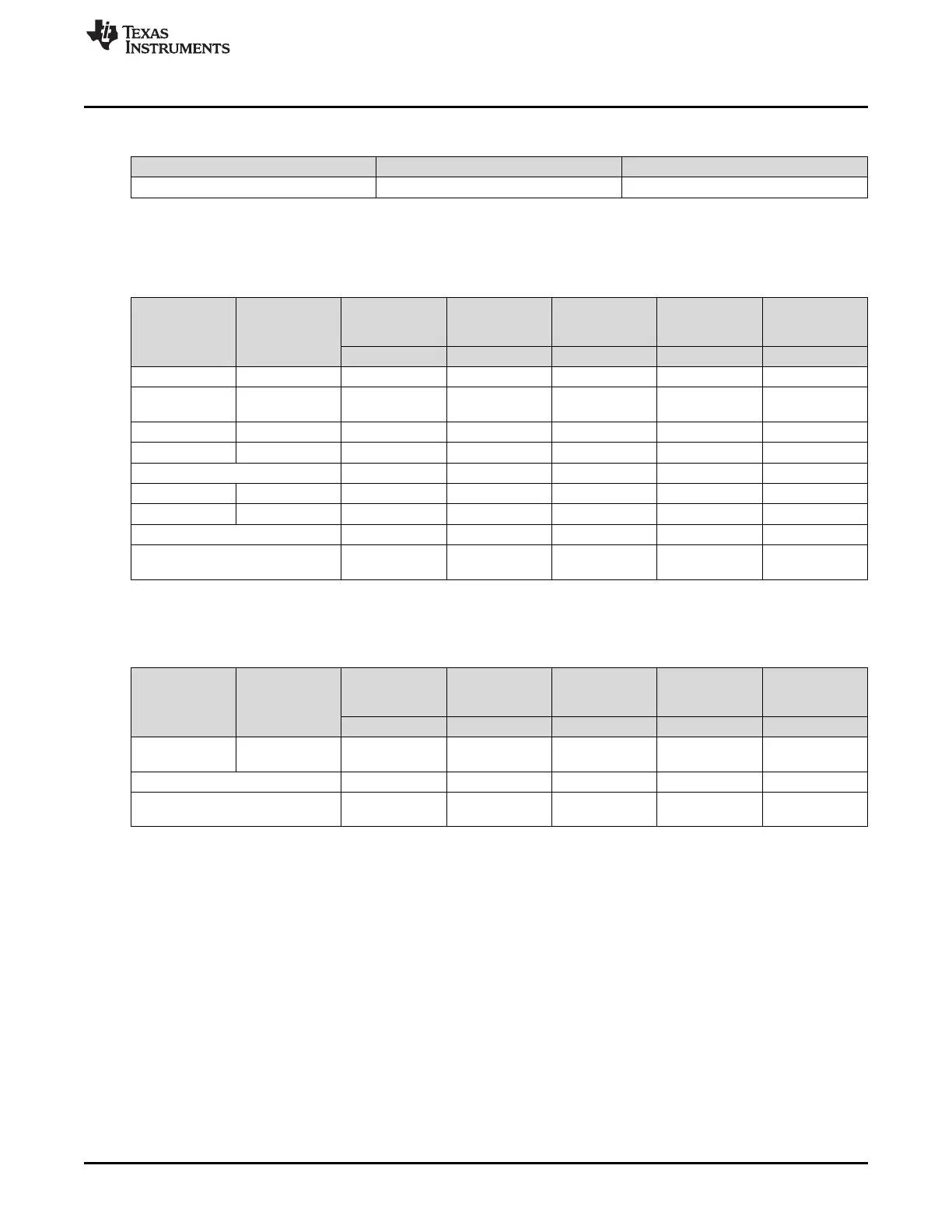

Using DDR3L data sourced from the BeagleBone Black, the power consumption of a VTT-less DDR3L

system can be approximated. VDCDC1 includes both the DDR3L memory power as well as the EMIF

interface on the AM335x. SoC power from AM335x GP EVM data summarized in Table 12.

Power Rail Voltage (V)

MPU OPP50

(300 MHz)

MPU OPP100

(600 MHz)

MPU OPP120

(720 MHz)

MPU OPP

Turbo

(800 MHz)

MPU OPP Nitro

(1000 MHz)

Power (mW) Power (mW) Power (mW) Power (mW) Power (mW)

DCDC1

(DDR+I/O)

1.35 52.29 53.12 53.15 52.84 52.20

SoC Power 372.84 492.08 562.99 614.72 715.02

Total Power (SoC + DDR3L)

without VTT

425.13 545.20 616.14 667.56 767.22

Loading...

Loading...