www.ti.com

Example Low Power Use Cases

33

SPRAC74A–February 2017–Revised March 2017

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

AM335x Low Power Design Guide

4.6 Low Power Modes

Standby and Suspend modes both put the processor into a low-power state with DDR is in self-refresh.

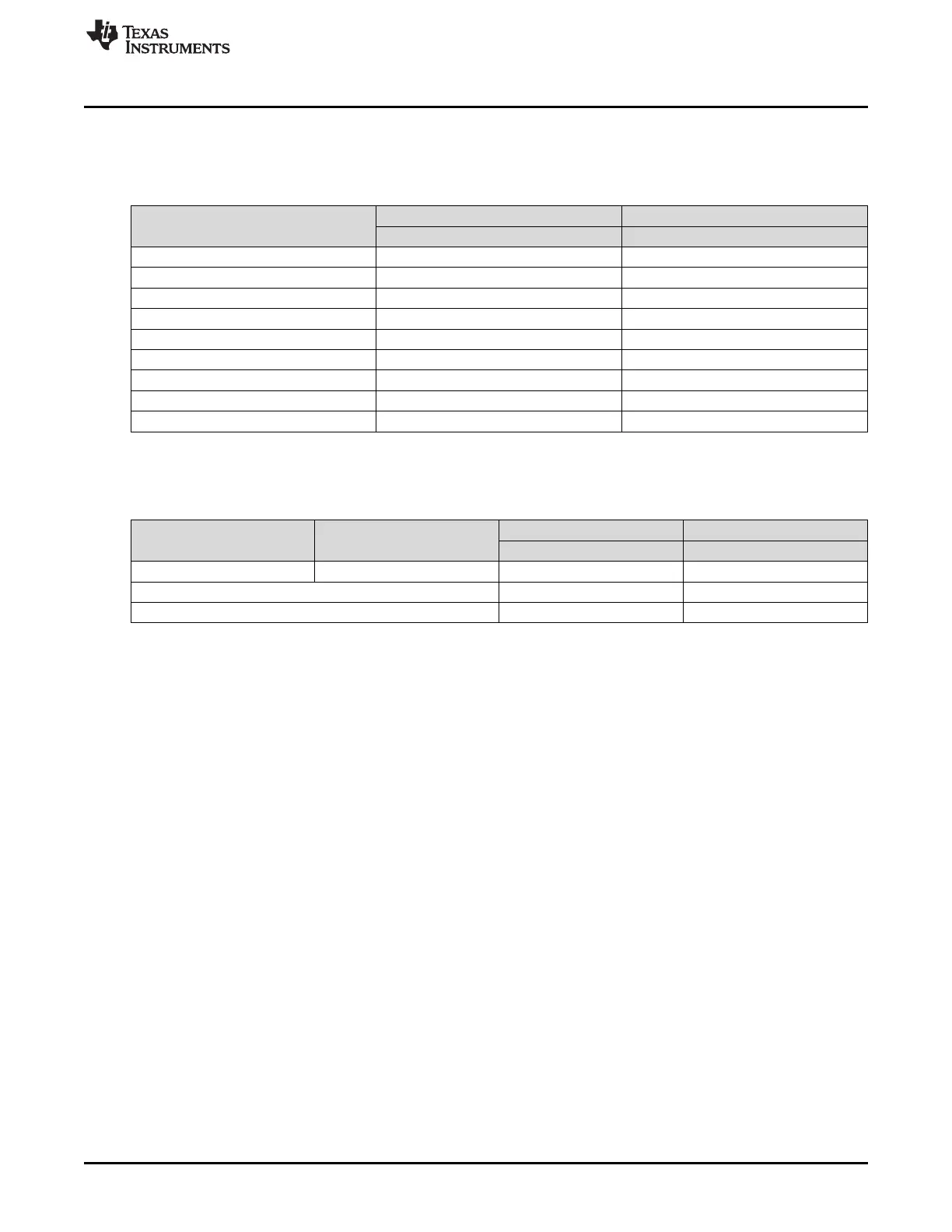

Table 14. Optimized Low Power Mode Power Consumption

Power Rail

Standby Suspend

Power (mW) Power (mW)

vdd_core_power 13.9 1.07

vdd_mpu_power 0.26 0.25

1.8V I/O 5.61 3.74

3.3V I/O 1.36 1.33

SoC Power without DDR3 21.13 6.39

vdds_ddr 0.4 0.3

vddsddrmem 27.49 27.52

DDR3 + I/O + VTT 27.53 27.55

Total Power (SoC + DDR3) with VTT 48.66 33.94

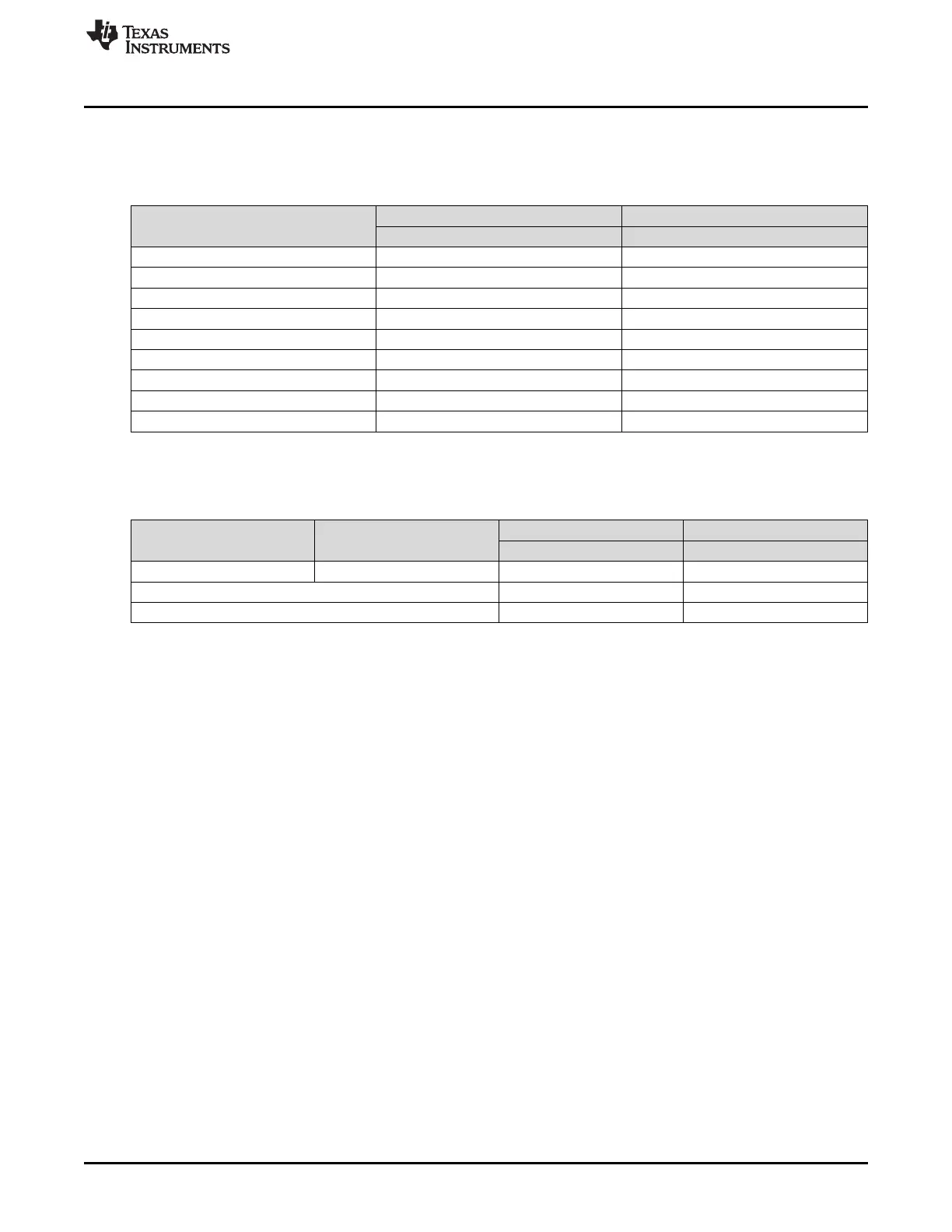

Using DDR3L data sourced from the BeagleBone Black, the power consumption of a VTT-less DDR3L

system can be approximated. VDCDC1 includes both the DDR3L memory power as well as the EMIF

interface on the AM335x. SoC power from AM335x GP EVM data summarized in Table 14.

Power Rail Voltage (V)

Standby Suspend

Power (mW) Power (mW)

DCDC1 (DDR+I/O) 1.35 11.40 11.42

SoC Power 21.13 6.39

Total Power (SoC + DDR3L) without VTT 32.53 17.81

5 References

• AM335x Power Estimation Tool wiki page

• Debugging AM335x Suspend-Resume Issues wiki page

• Optimizing AM335x IO Power in DeepSleep0 wiki page

• Linux Core Power Management User's Guide wiki page

• PMIC driver information wiki (for example, Linux Driver for TPS65910)

• AM335x PRCM Tools wiki page

• AM335x Schematic Checklist wiki page

• AM335x Hardware Design Guide wiki page

• AM335x Sitara™ Processors Data Manual

• AM335x and AMIC110 Sitara™ Processors Technical Reference Manual

• AM335x Sitara™ Processors Silicon Revisions 2.1, 2.0, 1.0 Silicon Errata

• Thermal Design Guide for DSP and ARM Application Processors

Loading...

Loading...