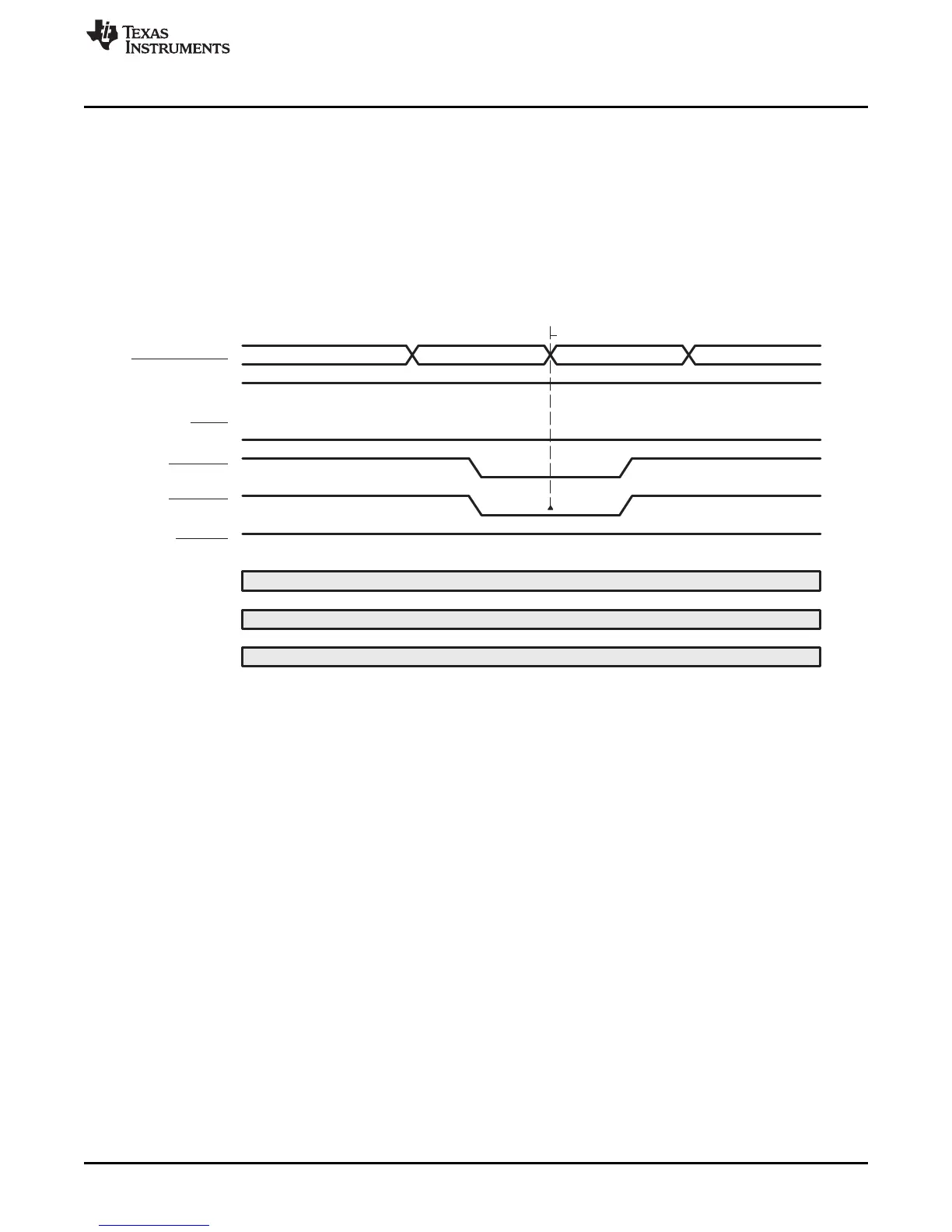

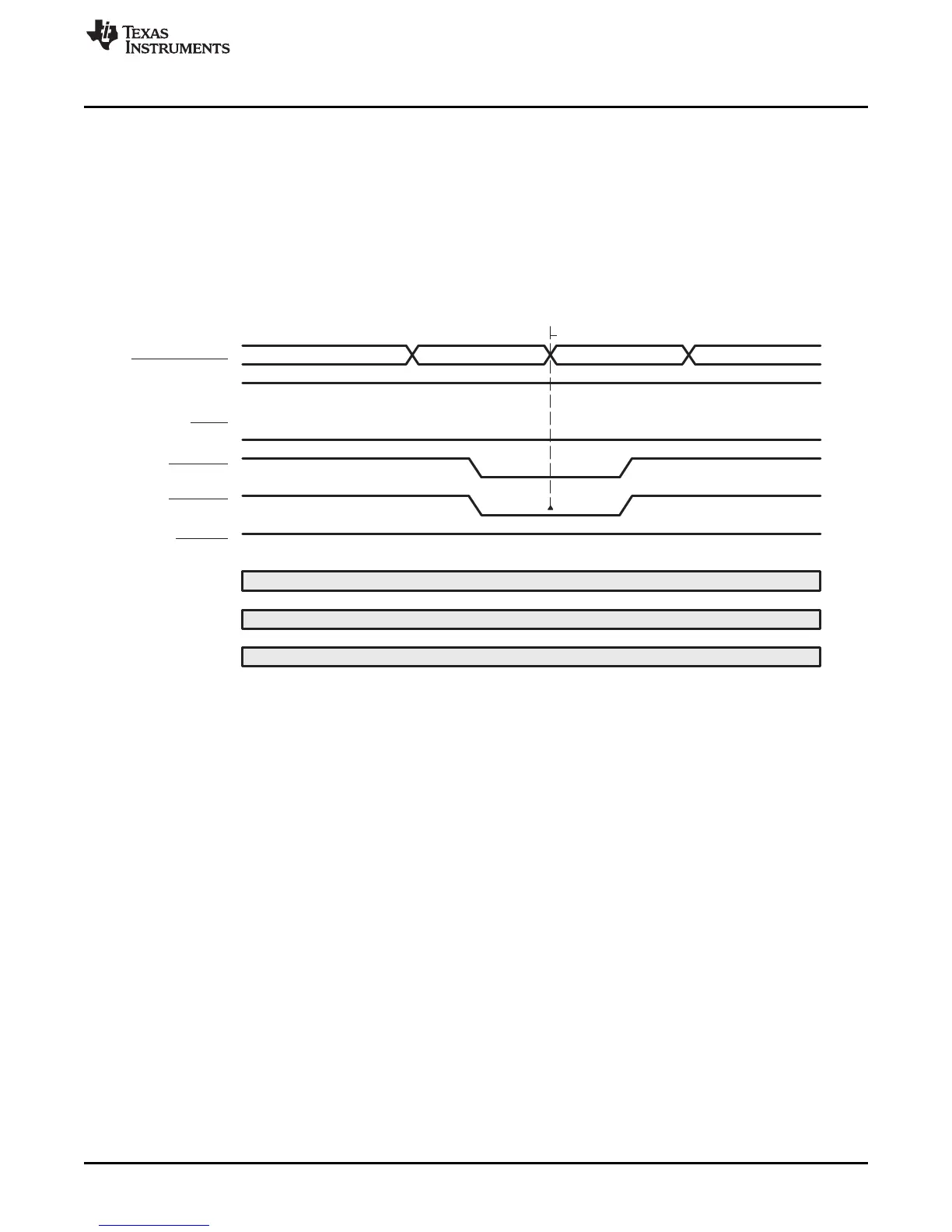

REFR

DDR2CLKOUT

DDR2CLKOUT

DCE0

DSDCKE

DSDRAS

DSDWE

DSDDQM[3:0]

DSDCAS

DBA[2:0]

DEA[13:0]

www.ti.com

Peripheral Architecture

2.4.2 Refresh Mode

The DDR2 memory controller issues refresh commands to the DDR2 SDRAM device (Figure 4). REFR is

automatically preceded by a DCAB command, ensuring the deactivation of all CE spaces and banks

selected. Following the DCAB command, the DDR2 memory controller begins performing refreshes at a

rate defined by the refresh rate (REFRESH_RATE) bit in the SDRAM refresh control register (SDRFC).

Page information is always invalid before and after a REFR command; thus, a refresh cycle always forces

a page miss. This type of refresh cycle is often called autorefresh. Autorefresh commands may not be

disabled within the DDR2 memory controller. See Section 2.8 for more details on REFR command

scheduling.

Figure 4. Refresh Command

15

SPRU970G– December 2005– Revised June 2011 C6455/C6454 DDR2 Memory Controller

Submit Documentation Feedback

Copyright © 2005–2011, Texas Instruments Incorporated

Loading...

Loading...