16 www.xilinx.com VC7203 IBERT Getting Started Guide

UG847 (v3.0) July 10, 2013

Chapter 1: VC7203 IBERT Getting Started Guide

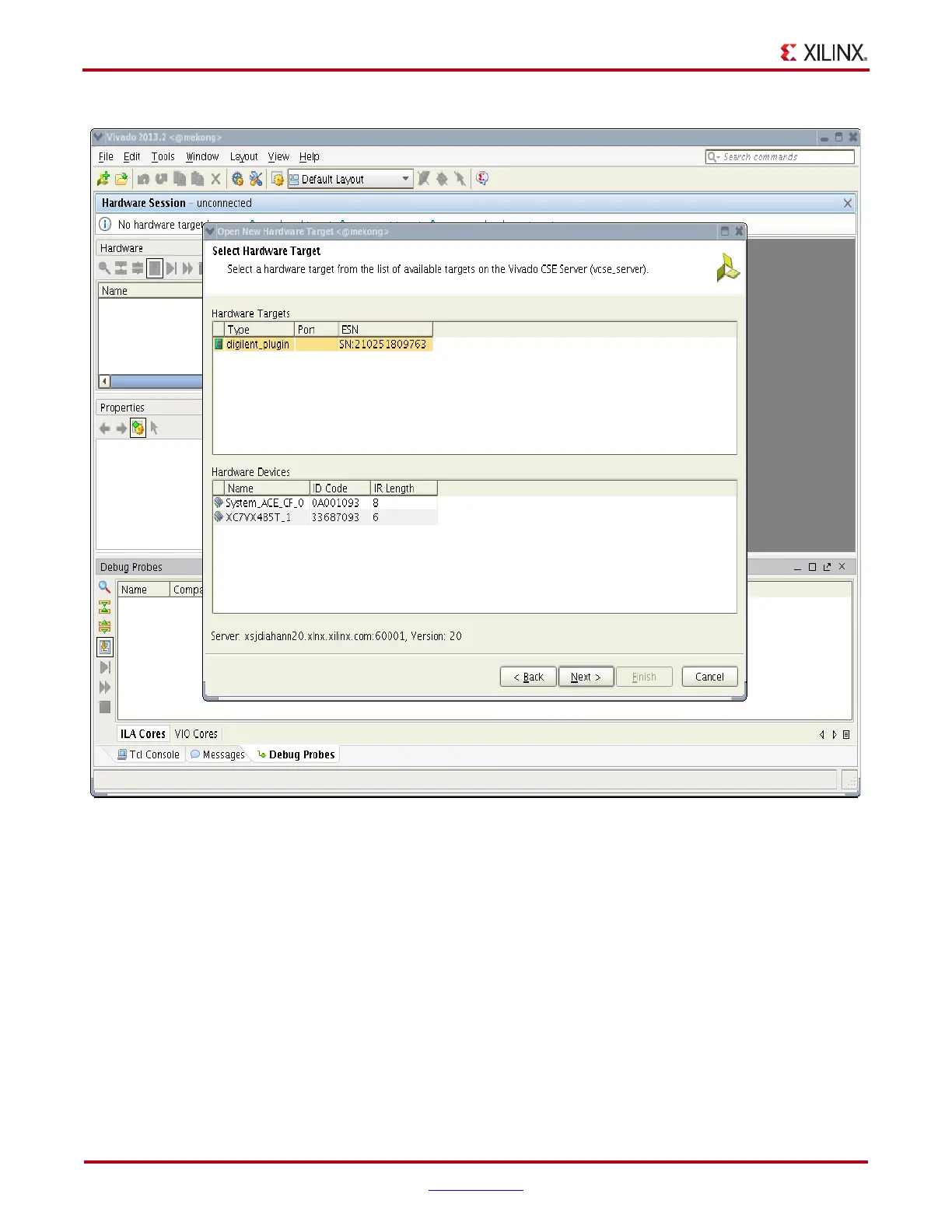

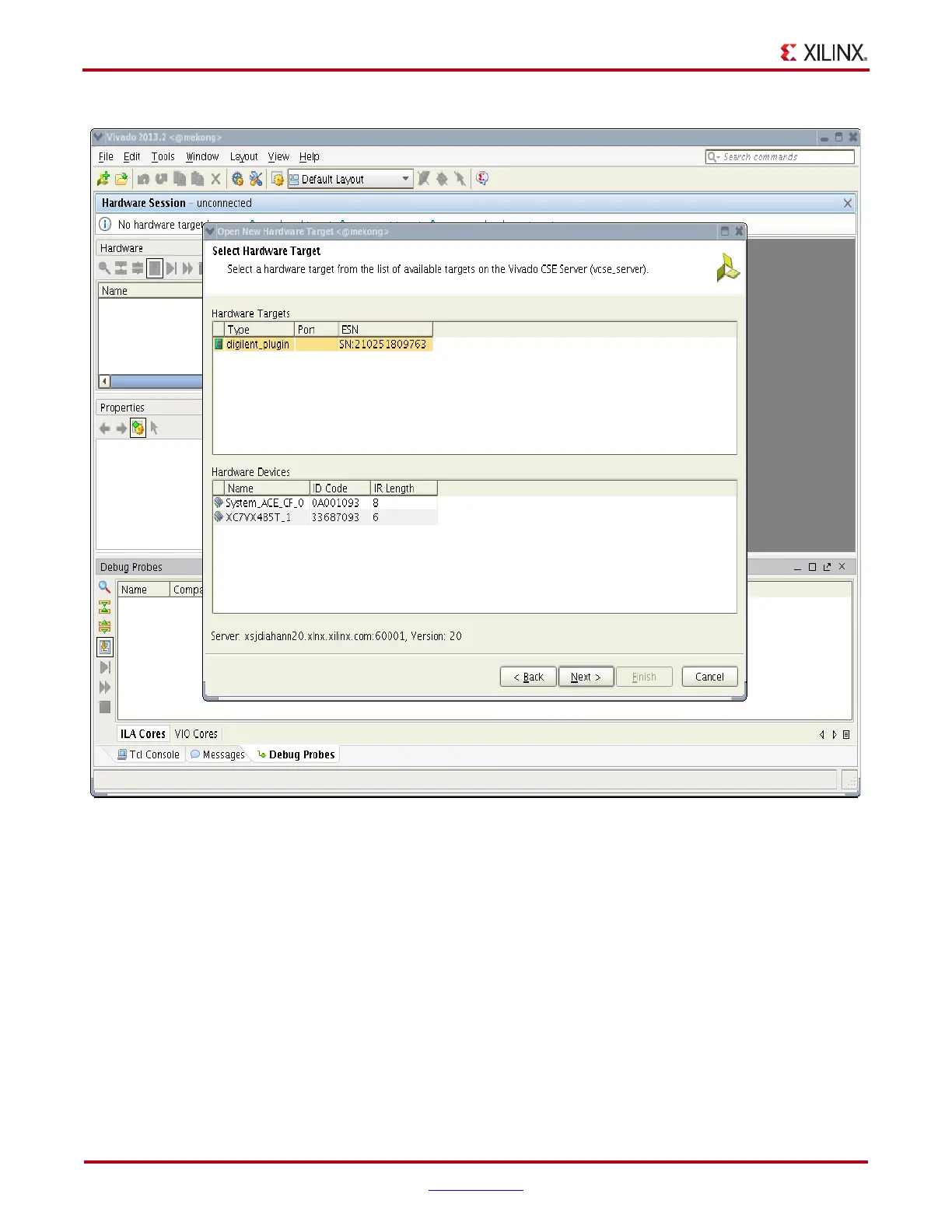

6. In the Set Hardware Target Properties window, leave the defaults and click Next. In the

Open Hardware Target Summary window, click Finish. The wizard closes and the

Vivado tool opens the hardware target.

Starting the SuperClock-2 Module

The IBERT demonstration designs use an integrated VIO core to control the clocks on the

SuperClock-2 module. The SuperClock-2 module features two clock-source components:

1) An always-on Si570 crystal oscillator and, 2) an Si5368 jitter-attenuating clock multiplier.

Outputs from either device can be used to drive the transceiver reference clocks.

X-Ref Target - Figure 1-12

Figure 1-12: Select Hardware Target

Loading...

Loading...