8 www.xilinx.com VC7203 IBERT Getting Started Guide

UG847 (v3.0) July 10, 2013

Chapter 1: VC7203 IBERT Getting Started Guide

All GTX transceiver pins and reference clock pins are routed from the FPGA to a connector

pad which interfaces with Samtec BullsEye connectors. Figure 1-2 A shows the connector

pad. Figure 1-2 B shows the connector pinout.

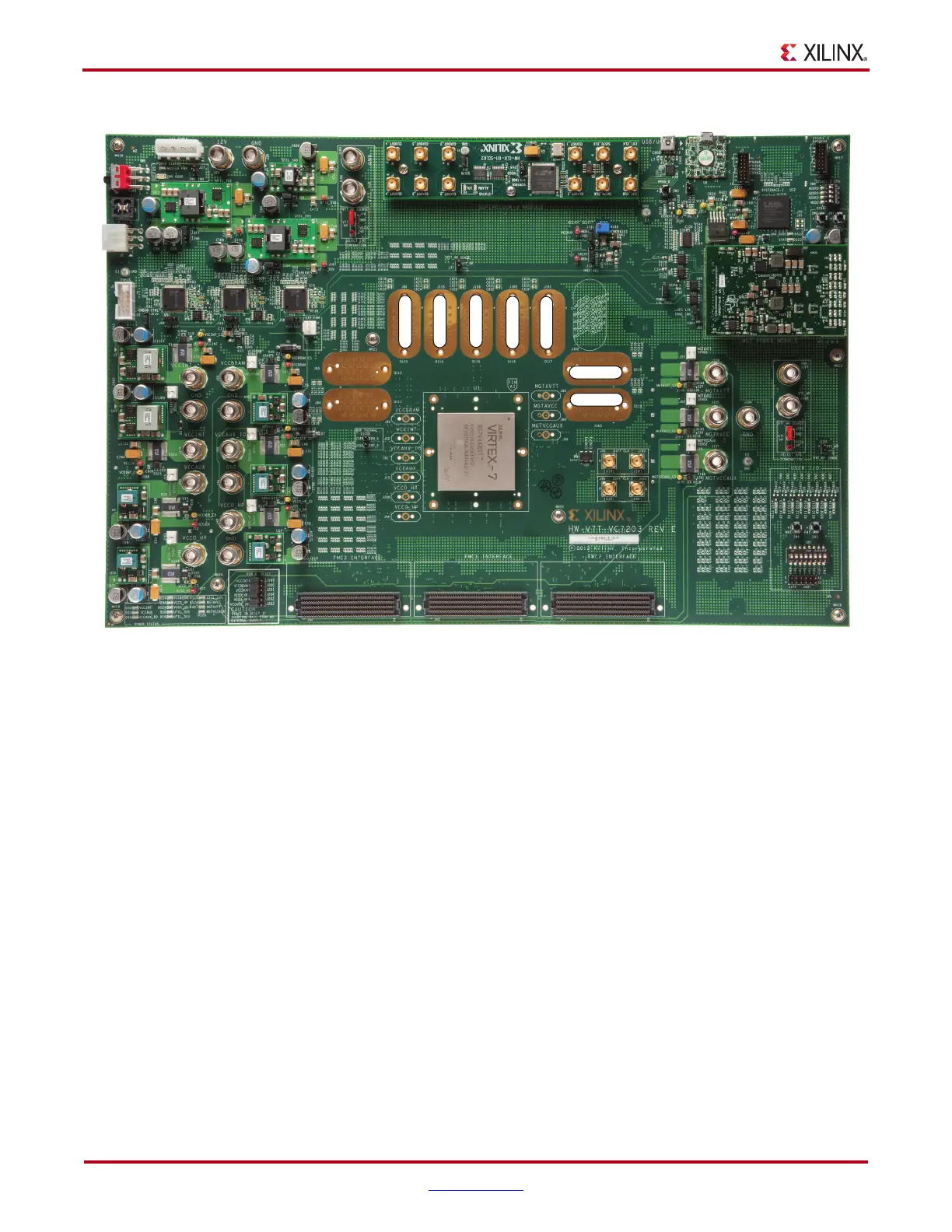

X-Ref Target - Figure 1-1

Figure 1-1: GTX Quad Locations

UG847_c1_01_1026112

QUAD_113

QUAD_114

QUAD_115

QUAD_116

QUAD_117

QUAD_118

QUAD_119

Loading...

Loading...