A5000/A4000

12

D65636GF-104-3B9 (XS369A00) SPF

PIN

NO.

NAME I/O FUNCTION

PIN

NO.

NAME I/O FUNCTION

1 ICN I Initial Clear 41 SYNIO I Serial Input0 Sync Clock(48kHz)

2 VDD - Power Supply 42 VDD - Power Supply

3 GND - Ground 43 GND - Ground

4 D0 I/O Data Bus 44 DIN0 I Serial Input0 Data Input(1.6MHz)

5 D1 I/O 45 CK256I1 I Serial Input1 256fs Clock(12.8MHz)

6 GND - Ground 46 BCKI1 I Serial Input1 Bit Clock(3.2MHz)

7 D2 I/O Data Bus 47 SYNI1 I Serial Input1 Sync Clock(48kHz)

8 D3 I/O 48 DIN1 I Serial Input1 Data Input(1.6MHz)

9 GND - Ground 49 DAC256O O 256fs Clock for DAC(12.8MHz)

10 VDD - Power Supply 50 DAC64O O 256fs Clock for DAC(3.2MHz)

11 D4 I/O Data Bus 51 DACWCKO O Word Clock for DAC(48kHz)

12 D5 I/O 52 DACDTI I DAC Data Input(1.6MHz)

13 GND - Ground 53 DACDTO O DAC Data Output(1.6MHz)

14 D6 I/O Data Bus 54 VDD - Power Supply

15 D7 I/O 55 GND - Ground

16 A4 I Address 56 MONMELO O Monitor MEL Output(1.6MHz)

17 CSN I Chip Select 57 DIT128O O 128fs Clock for DIT(6.4MHz)

18 WRN I Write 58 DITWCKO O Word Clock for DIT(48kHz)

19 RDN I Read 59 MUTEI I Mute Request Input(from CPU)

20 DREQN O DMA Request 60 MUTENO O Mute Request Output(to DAC&DIT)

21 DACKN I DMA Acknowledge 61 ERRI I PLL Error Input(from DIR)

22 GND - Ground 62 GND - Ground

23 VDD - Power Supply 63 VDD - Power Supply

24 D8 I/O Data Bus 64 ERRIRQN O PLL Error IRQ

25 D9 I/O 65 TGRESN O TG Reset Signal

26 GND - Ground 66 P7 I/O

27 D10 I/O Data Bus 67 P6 I/O

28 D11 I/O 68 P5 I/O

29 GND - Ground 69 P4 I/O I/O Port

30 VDD - Power Supply 70 P3 I/O

31 D12 I/O Data Bus 71 P2 I/O

32 D13 I/O 72 P1 I/O

33 GND - Ground 73 P0 I/O

34 D14 I/O Data Bus 74 OCSN I Option Chip Select0

35 D15 I/O 75 ODACKN I Option DMA Acknowledge

36 A1 I 76 ODDIR I Option DMA Direction

37 A2 I Address 77 OBOEN O Option Bus Buffer Output Enable

38 A3 I 78 OBDIR O Option Bus Buffer Direction

39 CK256IO I Serial Input0 256fs Clock(12.8MHz) 79 CSOUTN O Chip Select Out at A4=1, A3=1

40 BCKIO I

Serial Input0 Bit Clock(3.2MHz) 80 ASSIGN O Write Pulse Out at A4=1, A3=0, WR=0

(IC11)

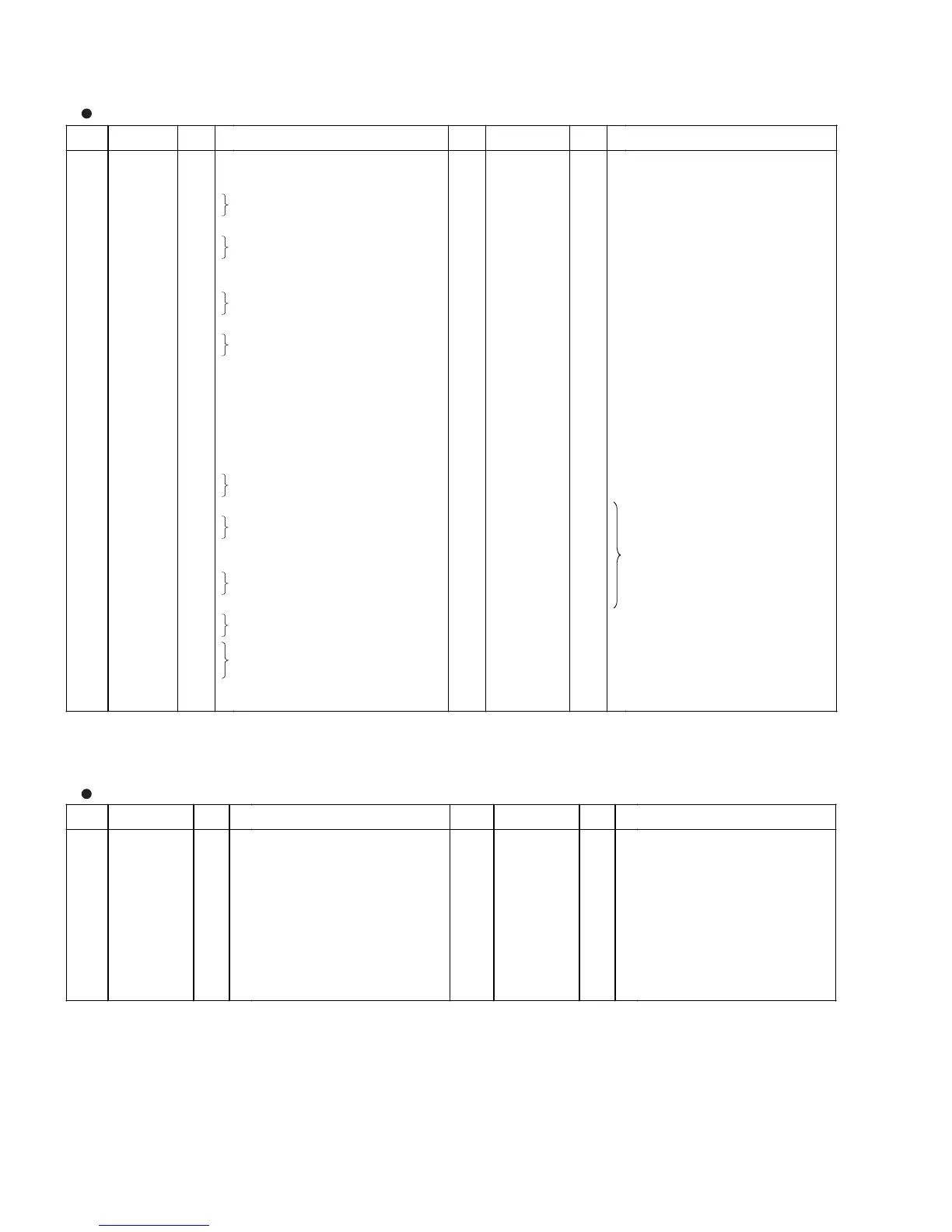

PCM1800 (XU770A00) A/D Converter

PIN

NO.

PIN

NO.

1 VINL I Analog input (L ch.) 13 LRCK I/O

Sampling clock input/ output

2 VREF1 Reference 1 decoupling cap. 14 BCK I/O

Bit clock input/ output

3 REFCOM Reference decoupling common 15 DOUT O

Audio data output

4 VREF2 Reference 2 decoupling cap. 16 SYSCK I

System clock input

5 VINR I Analog input (R ch.) 17 DGND

Digital ground

6 RSTB I Reset input active “L” 18 VDD

Power supply +5V

7 BYPAS I LCF bypass control 19 CINNR

Anti-aliasing filter cap. (-) R ch.

8 FMT0 I Audio data format 0 20 CINPR Anti-aliasing filter cap. (+) R ch.

9 FMT1 I Audio data format 1 21 CINNL

Anti-aliasing filter cap. (-) L ch.

10 MODE0 I Master/ Slave mode selection 0 22 CINPL

Anti-aliasing filter cap. (+) L ch.

11 MODE1 I Master/ Slave mode selection 1 23 VCC

Analog power supply

12 FSYNC I/O Frame sync. Input/ output 24 AGND Analog Ground

(IC807)

Loading...

Loading...