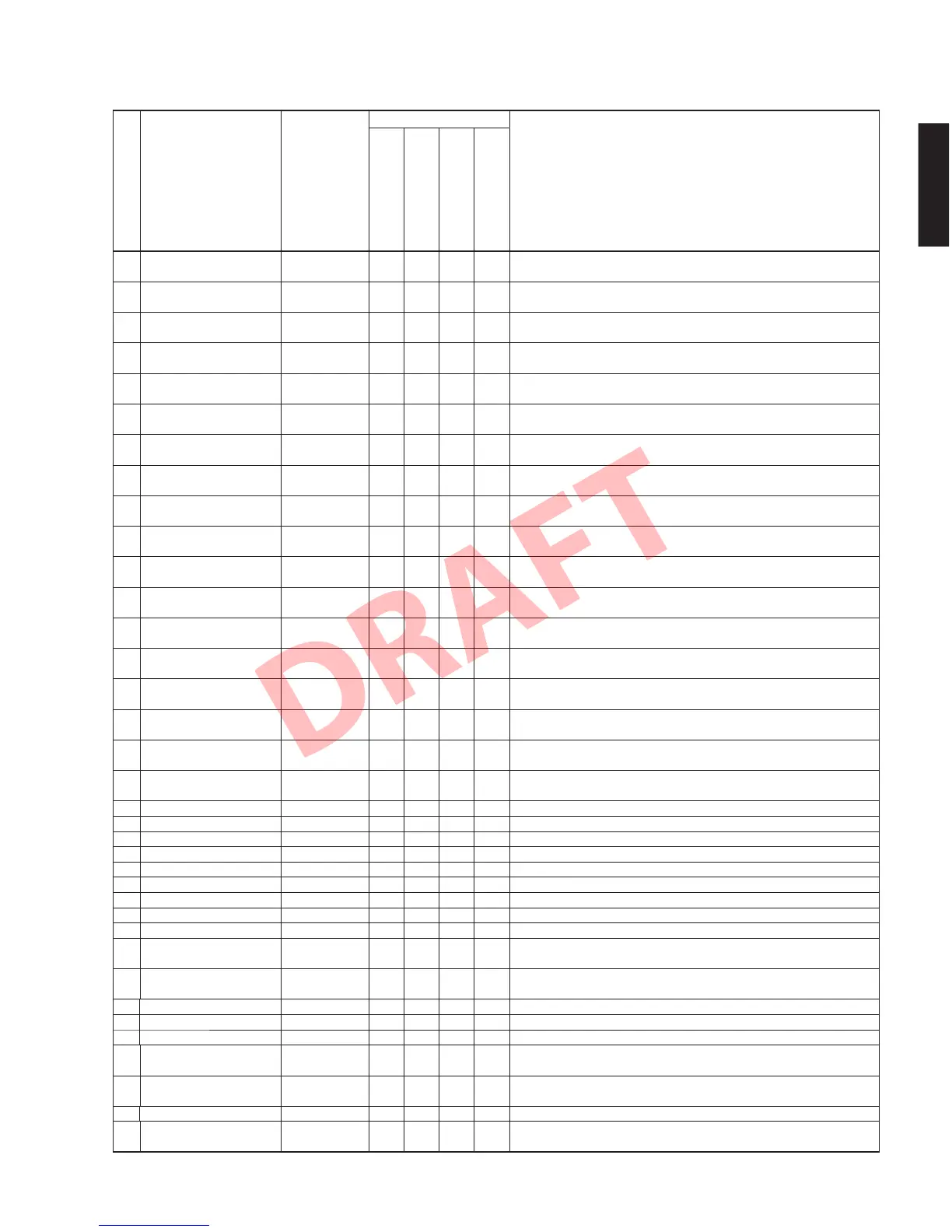

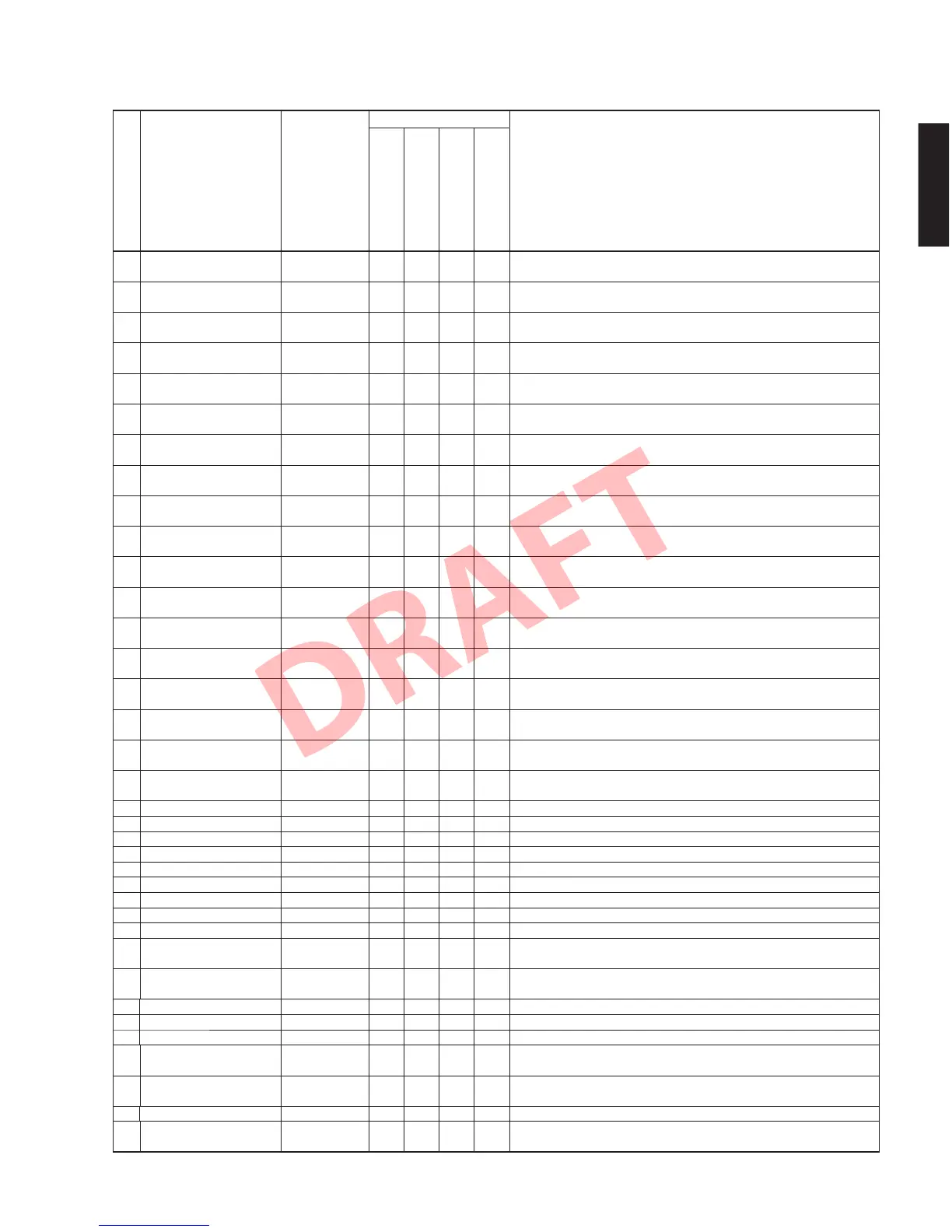

Pin

No.

Port Name

Function

Name

(P.C.B.)

I/O

Detail of Function

Power On

Standby /

[Stby AW] / (iPod)

Stby HDMI /

[Stby CEC]

When Apply Current

96 PF3 USB_FLG I HiZ USB excess current detect input (High side SW)

PF3/TRACEDATA2

97 PF4 USB_PON O O USB power control output

PF4/TRACEDATA3

98 PG0 TUN_USB_SDA SIO O TUNER/USB HOST I2C data input/output

PG0/SDA1/TB7IN0 Apple spare

99 PG1 TUN_USB_SCL SO O TUNER/USB HOST I2C clock output

PG1/SCL1/TB7IN1 Apple spare

100 PG2 MIC_N_DET I+ HiZ Microphone connection detect input

PG2/SCK1/CS0n

101 INT6 STBY_SW IRQ IRQ Input to detect power ON/OFF switch

PG3/INT6/CS1

102 PG4 TUN_N_RST O O TUNER reset output

PG4/SDA2/TB9IN0 P.U to +3.3D

103 PG5 HDSUR_LED O O HD surround LED (blue) output (High active)

PG5/SCL2/TB9IN1

104 PG6 AW_PON O O [O] AW power control output

PG6/SCK2/CS3n O

105 INT7 HDMI_N_INT IRQ O IRQ HDMI interrupt input

PG7/INT7/WDTOUTn

106 PH0 OSD_WRITE O O OSD_Flash write enable

PH0/SDA3/TBAIN0

107 PH1 HDMI_PON1 O O O HDMI power (5.0V) ON/OFF control output

PH1/SCL3/SI3/TBAIN0

108 PH2 HDMI_PON2 O O O HDMI power (1.3V) ON/OFF control output

PH2/SCK3/TBBIN0

109 PH3 HDMI_PON3 O O O HDMI power (3.3V) ON/OFF control output

PH3/INTC/TBBIN1

110 SDA4 HDMI_SDA SIO O SIO HDMI RX/TX I2C data input/output

PH4/SDA4/TBDIN0 P.U to +3.3H

111 SCL4 HDMI_SCL SO O SO HDMI RX/TX I2C clock output

PH5/SCL4/TBDIN1 P.U to +3.3H

112 PH6 HDMI_N_RST O O O HDMI reset output

PH6/SCK4/TBEIN0

113 INTD HDMI_MUTE IRQ O IRQ HDMI mute input

PH7/INTD/TBEIN1

114 REGVCC3 REGVCC3 MCU

115 XT1 XT1 MCU Low speed (32kHz) oscillator connection terminal (Input)

116 XT2 XT2 MCU Low speed (32kHz) oscillator connection terminal (Output)

117 CVCC3 CVCC3 MCU

118 X1 X1 MCU High speed (10MHz) oscillator connection terminal (Input)

119 CVSS CVSS MCU MCU MCU

120 X2 X2 MCU High speed (10MHz) oscillator connection terminal (Output)

121 DVCC3 DVCC3 MCU

122 REGVSS REGVSS MCU MCU MCU

123 PI2 232C_RTS O O 232C transmission request output

PI2/INTE Data input for CDDA writing (Spare)

124 PI3 P-CON O O Switching IC ON/OFF control input

PI3/INTF LR clock input for CDDA writing (Spare)

125 NMIn NMIn IRQ IRQ Processed in microprocessor, usually pull-up

126 TEST1 TEST1

127 TEST2 TEST2

128 BOOTn

FLASH_N_BOOT

I I FLASH single boot mode input, single boot mode at “L”

PI0/B00Tn

129 CEC HDMI_CEC SIO O SIO HDMI CEC data input/output

PI1/CEC

130 AVCC3 AVCC3 MCU

131 AIN0 KEY1 AD AD KEY input

PJ0/AIN0 * For CDDA writing mode

103

YSP-CU4300/YSP-CU3300/NS-WSW160

YSP-CU4300/YSP-CU3300/

NS-WSW160

Loading...

Loading...