eZ80

®

CPU

User Manual

UM007714-0908 CPU Instruction Set

218

LD (Mmn), rr

Load Indirect

Operation

(Mmn) ← rr

Description

The

rr

operand is any of the multibyte registers BC, DE, or HL. The CPU stores the con-

tents of the multibyte register

rr

in the memory location specified by

Mmn

.

Condition Bits Affected

None.

Attributes

Zilog recommends against using the .SIL and .LIS suffixes with this instruction. The .SIL

instruction fetches a 24-bit value, Mmn. However, this instruction ignores the upper byte

and uses address {MBASE, mm, nn} instead. The .LIS instruction fetches a 16-bit value,

mn

. However, the .LIS instruction does not use the MBASE value. Instead, it uses address

{00, mm, nn}.

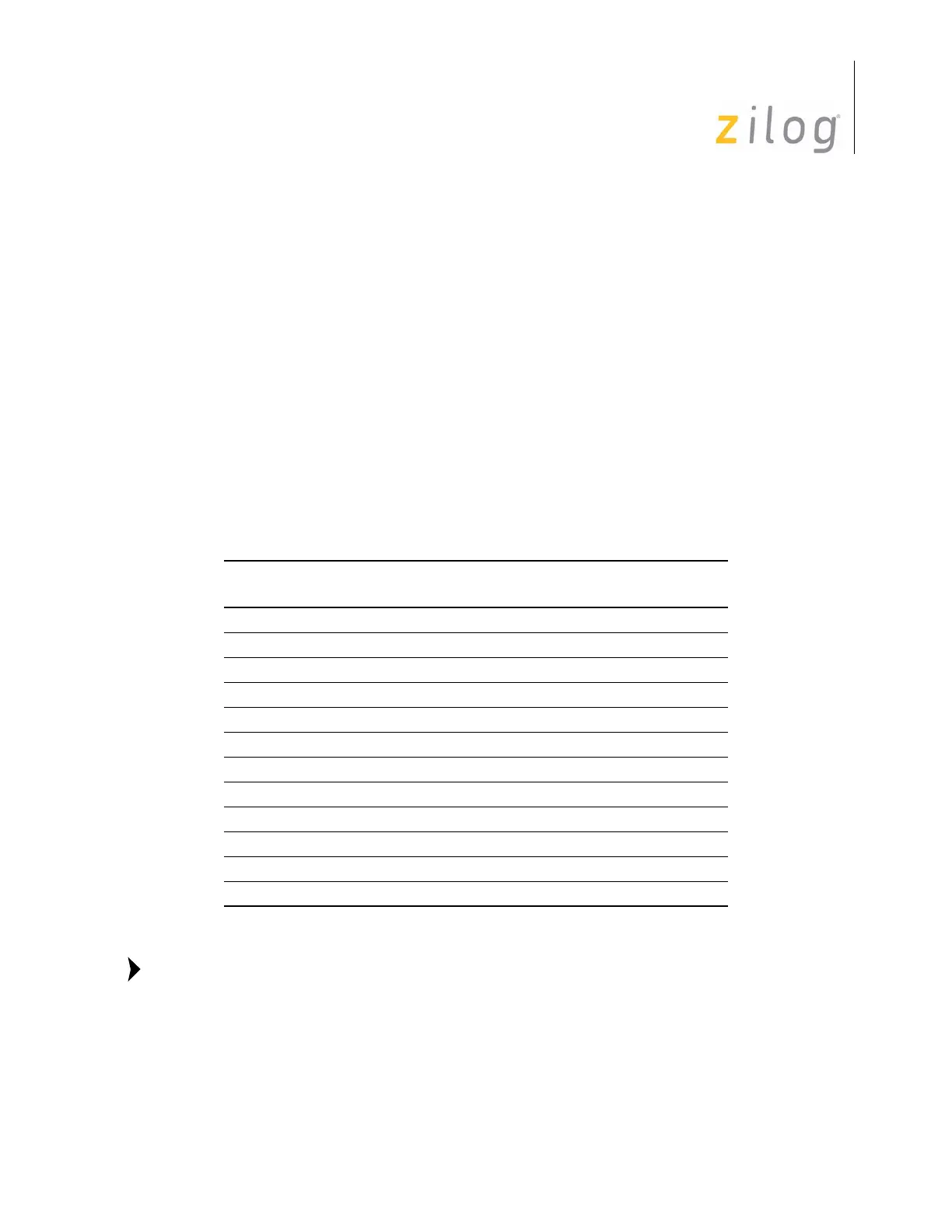

Mnemonic Operand

ADL

Mode Cycle Opcode (hex)

LD (mn),BC 0 6 ED, 43, nn, mm

LD (Mmn),BC 1 8 ED, 43, nn, mm, MM

LD.SIS (mn),BC 1 7 40, ED, 43, nn, mm

LD.LIL (Mmn),BC 0 9 5B, ED, 43, nn, mm, MM

LD (mn),DE 0 6 ED, 53, nn, mm

LD (Mmn),DE 1 8 ED, 53, nn, mm, MM

LD.SIS (mn),DE 1 7 40, ED, 53, nn, mm

LD.LIL (Mmn),DE 0 9 5B, ED, 53, nn, mm, MM

LD (mn),HL 0 5 22, nn, mm

LD (Mmn),HL 1 7 22, nn, mm, MM

LD.SIS (mn),HL 1 6 40, 22, nn, mm

LD.LIL (Mmn),HL 0 8 5B, 22, nn, mm, MM

Loading...

Loading...